逻辑综合

逻辑学综合练习题集答案

A、B、C、D有以下关系: 〔1〕如果A不真包含于B,那么C与D不全异。 〔2〕只有B与D全异,B才不真包含于D。 〔3〕B与D相容,但C与D不相容。 请推出A与B、B与D、A与D的外延关系,写出推导过程并将 A、B、C、D全异〕 〔3〕联言推理分解式

〔1〕如果B不去,那么A也不能去 〔2〕只有当C去时,B才能跟着去 〔3〕假设D去,那么E也去 〔4〕A去或D去 问:侦察连长应挑选哪两个深入敌区?请写出推导过程。

5〕假设设A去

〔6〕B去

〔1〕、〔5〕充分条件假言推理否认后件式

〔7〕C去

〔2〕、〔6〕必要条件假言推理肯定后件式

A、B、C同去,与题意不符。

组长是团员。

2 、以下三句话恰有一句为真,问:全班 46名学生有多少人会使用计算机。请写出 推导过程。

〔1〕有人会使用计算机 〔2〕有人不会使用计算机 〔3〕班长不会使用计算机

(1)与(2)为下反对关系,必有一真, 据此,那么(3)假; (3)假,那么“班 长会使用计算机〞(4);由(4)可知(1) 真,据此,那么(2)假;由(2)假,可 推出:全班46名学生都会使用计算 机。

(1)与(2)为下反对关系,不能同假,至少有一真, 据此,那么(3)假;

(3)假,那么“班长会使用计算机〞(4);

由(4)可知(1)真,据此,那么(2)假;

由(2)假,可推出:全班46名学生都会使用计算 机。

问:A与C具有什么外延关系?请写出推导过程,并将A、 B、C三个概念在外延上可能有的关系用欧拉图表示出来

A真包含于B,那么所有A是B;

由所有A是B,有C不是B,可得有C不是A〔三段论〕;

由有C不是A,可得并非C真包含于A〔4〕;

由此可知C真包含A〔〔3〕、〔4〕充分条件假言推理否 认后件式〕。

逻辑综合训练(一)

逻辑综合训练(一)1.给原来的黑白电影上色是不合适的,如果这些电影被拍成彩色的,几百种原来的艺术选择可能以其他方式做出。

这些电影场景的灯光被安排为使亮光和阴影在黑白两色下看起来合适。

以下哪项,替代上面关于电影场景灯光的宣称,将给予上面的论述以相同类型的支持?A.给予这些电影特性的一个重要部分是黑白模式的效果。

B.彩色胶片可能更好地抓住电影制作者的意图。

C.彩色胶片在拍电影时比黑白胶片更高级。

D.对演员进行化妆,使其在黑白电影中看起来合适。

E.选择黑白电影而不是彩色电影完全是口味的问题。

2.社会撰稿人:因为青少年缺乏基本的开车技巧,所以,应给予青少年的驾驶执照附加的限制。

尽管19岁和再小一点的司机只占注册司机的7%,但是他们却是超过14%的交通死亡事故的肇事者。

下面每一项,如果正确,都能削弱青少年缺乏基本的开车技巧的论述,除了:A.与其他人开的车相比,青少年开的车较旧,且稳定性较差。

B.青少年司机和他们的乘客使用座带和肩带的可能性不如其他人大。

C.青少年司机平均每年开车的距离超过其他司机的两倍。

D.青少年引起的交通事故比其他人引起的交通事故严重。

E.青少年开车时的乘客人数很有可能比一般的司机多。

3.加尔文:火灾保险单对投保人是不利的。

典型的投保人支付的保险费通常比他或她通过保险单收到的赔付款要高。

劳拉:是的,但是投保人认为持有一张保险单对他们有好处还是有道理的。

通过持有一张保险单而得到的心境平和是投保人得到的主要好处。

劳拉通过什么来回应加尔文的论述?A.对加尔文的信息来源的真实性提出质疑。

B.引入加尔文的论述忽略的一种想法。

C.指出加尔文的论述以它将要证明的东西作为假设的前提。

D.对加尔文的论述中提出的证据的真实性表示怀疑。

E.指出加尔文的证据和它推出的结论无关。

4.在D国,新的环境行动党在1988年赢得了七人市议会中的两个席位。

在1992年的选举中,它失去了这两个席位,尽管该党派保护环境的政纲实质上保持不变。

张雪峰关于综合逻辑题的30个问题

张雪峰关于综合逻辑题的30个问题综合逻辑题是指结合了多个逻辑推理和思维能力的题目,通常需要综合运用数学、逻辑、推理和常识等方面的知识来解答。

这类题目具有较高的难度,需要考生具备较强的逻辑思维和综合能力。

张雪峰是中国知名数学家和教育家,他提出了一套关于综合逻辑题的30个问题,旨在培养人们的综合逻辑思维能力。

本文将深入探讨这30个问题,并分享一些个人观点和理解。

以下是张雪峰关于综合逻辑题的30个问题:1. 人的一生中,能否找到真正无关紧要、唯一值得去做的事情?2. 学习中,理解力和记忆力哪个更重要?3. 知识是不是越多越好?应该如何选择学习的内容?4. 如何判断一篇文章或一本书是否有价值?5. 科学和艺术之间有哪些相似和不同之处?6. 宇宙中是否存在无限大和无限小?7. 在现实生活中,时间和空间哪一个更重要?8. 人类是否可以超越时间和空间的限制?9. 数学是一种发现还是创造?10. 数学和哲学之间有哪些联系?11. 如何理解无穷大和微积分?12. 经验和理论哪一个更重要?它们之间有哪些关系?13. 人脑是否可以完全理解自身?14. 信息时代下,我们如何平衡信息的获取和思考的时间?15. 如何掌握批判性思维和创造性思维?16. 科技的发展对思维方式和社会结构有何影响?17. 知识的普及是否可以消除社会不平等?18. 是否存在终极真理?我们如何寻找和判断真理?19. 知识和智慧之间有哪些区别?20. 人工智能能否取代人类的智慧?21. 真实和虚构的界限在哪里?它们之间的关系是什么?22. 个体和社会之间如何平衡?23. 自由意志是否存在?我们是否真正拥有决策的自主权?24. 如何培养创造力和创新能力?25. 人的思维是否受到语言的限制?26. 心理学和哲学之间有哪些交叉点和对话?27. 自然规律和人类意识之间有哪些联系?28. 我们是否能够超越对立和矛盾的思维模式?29. 宗教信仰对人类思维和行为的影响是什么?30. 如何培养人的情感智慧和情商?这30个问题涉及了数学、哲学、科学、艺术、心理学和社会等多个领域,反映了现代社会对于知识、思维和人生等问题的关注。

Verilog逻辑综合

一、verilog结构类型

逻辑综合工具并不能处理随意编写的verilog结构描述:通常,周期到周期的任 何RTL verilog结构描述都能为逻辑综合工具所接受。

支持综合的Verilog结构类型

结构类型

关键字或描述

注释

端口

input, inout, output

参数

parameter

模块定义

module

计算机辅助逻辑综合工具的出现已经把高层次描述向逻辑门的转化过程自 动化了。设计者现在可以把精力集中在体系结构的方案、设计的硬件语言描 述上,由综合工具在内部进行几次反复,生成优化的门级描述。

自动化的逻辑综合已经非常有效地减少了高层次设计到门级网表的转化时 间。它使设计者可以把更多的时间用于更高层次的描述上,因为把设计转换 到门级网表所需的时间大大减少了。

s);

input d0, d1, s;

output out;

reg out;

always @( s or d0 or

d1)

if (s)

out

out = d1;

else

out = d0;

endmodule

定义了所有可能的选项的if—then嵌套语句,综合结果是受条件 控制的纯组合逻辑电路。

module compif (a, b, c, d,

z_1.SUM0_0_x2

XOR2

[1]

z_1.SUM1_0_x2

[1]

z_1.N_6_i_i.O

module increment (phy, ones,z); input phy; input [1:0] ones; output [1:0] z; reg [1:0] z; always @ (phy or ones) if (phy) z = ones +1; endmodule

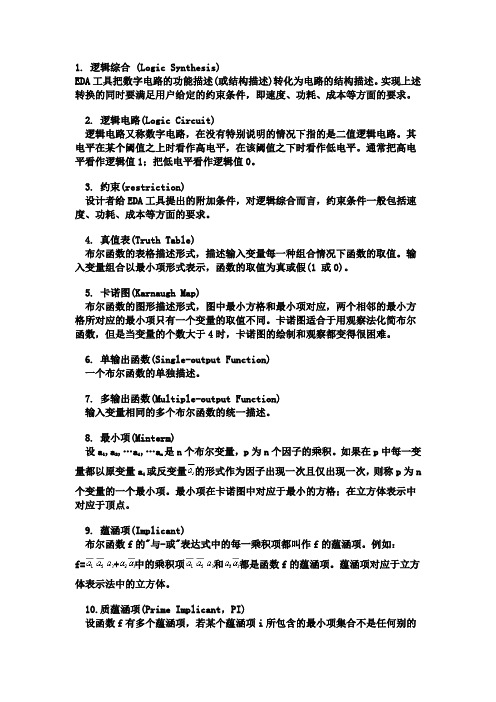

逻辑综合中的基本概念

1. 逻辑综合 (Logic Synthesis)EDA工具把数字电路的功能描述(或结构描述)转化为电路的结构描述。

实现上述转换的同时要满足用户给定的约束条件,即速度、功耗、成本等方面的要求。

2. 逻辑电路(Logic Circuit)逻辑电路又称数字电路,在没有特别说明的情况下指的是二值逻辑电路。

其电平在某个阈值之上时看作高电平,在该阈值之下时看作低电平。

通常把高电平看作逻辑值1;把低电平看作逻辑值0。

3. 约束(restriction)设计者给EDA工具提出的附加条件,对逻辑综合而言,约束条件一般包括速度、功耗、成本等方面的要求。

4. 真值表(Truth Table)布尔函数的表格描述形式,描述输入变量每一种组合情况下函数的取值。

输入变量组合以最小项形式表示,函数的取值为真或假(1 或0)。

5. 卡诺图(Karnaugh Map)布尔函数的图形描述形式,图中最小方格和最小项对应,两个相邻的最小方格所对应的最小项只有一个变量的取值不同。

卡诺图适合于用观察法化简布尔函数,但是当变量的个数大于4时,卡诺图的绘制和观察都变得很困难。

6. 单输出函数(Single-output Function)一个布尔函数的单独描述。

7. 多输出函数(Multiple-output Function)输入变量相同的多个布尔函数的统一描述。

8. 最小项(Minterm)设a1,a2,…ai,…an是n个布尔变量,p为n个因子的乘积。

如果在p中每一变量都以原变量ai或反变量的形式作为因子出现一次且仅出现一次,则称p为n 个变量的一个最小项。

最小项在卡诺图中对应于最小的方格;在立方体表示中对应于顶点。

9. 蕴涵项(Implicant)布尔函数f的"与-或"表达式中的每一乘积项都叫作f的蕴涵项。

例如:f=+中的乘积项和都是函数f的蕴涵项。

蕴涵项对应于立方体表示法中的立方体。

10.质蕴涵项(Prime Implicant,PI)设函数f有多个蕴涵项,若某个蕴涵项i所包含的最小项集合不是任何别的蕴涵项所包含的最小项集合的子集的话,则称i为函数f的质蕴涵项。

综合逻辑知识点总结归纳

综合逻辑知识点总结归纳命题逻辑是最基本的逻辑形式之一,它关注的是命题之间的关系。

命题是陈述句,可以为真或者为假。

在命题逻辑中,我们可以用符号来代表命题,比如用P代表“今天下雨”,用Q代表“我不出门”。

然后可以用逻辑连接词来表示命题之间的关系,比如用“与”、“或”、“非”等。

这样,我们可以得出许多适用于命题之间的推理规则,比如假言推理、析取三段论、二重否定律等。

谬误分析是逻辑学中的一个重要部分,它关注的是人们在思维和语言表达中所犯的错误。

谬误可以是由于人们对逻辑原则的不理解,也可以是出于故意的欺骗目的。

谬误分析的目的是帮助人们识别并避免这些错误,使思维更加客观和科学。

范畴逻辑是另一种重要的逻辑形式,它从更宽泛的角度考虑命题之间的关系。

在范畴逻辑中,我们需要考虑命题的谓词性质以及它们之间的数量关系。

范畴逻辑可以帮助我们更好地理解概念之间的关系,比如“所有的”,“有些”,“不存在”,“大于”等。

诡辩术是指用不正当的论证方式来欺骗他人。

它是一种常见的逻辑错误,可以通过谬误分析的方法来进行识别和纠正。

了解诡辩术可以帮助我们更好地理解和运用逻辑知识,同时也可以帮助我们提高辨别谎言的能力。

模态逻辑是研究命题中可能性、必然性和可能必然性的一种形式逻辑。

它可以帮助我们更好地理解命题的真实性以及推理的有效性。

模态逻辑用于分析与条件陈述性命题有关的可能性和必然性,以及命题之间的关系。

归纳逻辑是一种推理方式,它是从特殊到一般的推理形式。

归纳逻辑要求我们从已知的例子或特殊情况推断出一般规律或结论。

在日常生活中,我们常常用到归纳逻辑来进行推理和获得新的知识。

除了上述知识点之外,逻辑学还涉及很多其他的内容,比如命题算术、证明理论、递归论、哥德尔不完备定理等。

这些知识点都有助于我们更好地了解逻辑学的精髓和意义。

综上所述,逻辑学是一门重要的学科,它涉及很多知识点,包括命题逻辑、谬误分析、范畴逻辑、诡辩术、模态逻辑、归纳逻辑等。

理解和掌握这些知识点将有助于提高我们的思维能力和解决问题的能力,同时也能帮助我们更好地识别和避免逻辑错误。

逻辑综合练习题

逻辑综合练习题一填空1任何逻辑形式都是由逻辑﹍﹍﹍﹍和﹍﹍﹍﹍两个部分组成。

逻辑形式的不同是由﹍﹍﹍﹍﹍的不同决定的。

2“pVq”的逻辑常项是﹍﹍﹍﹍,变项是﹍﹍﹍﹍。

3“所有的S都不是P”这个判断形式的逻辑常项是﹍﹍﹍﹍,逻辑变项是﹍﹍﹍﹍。

4“如果某甲犯了杀人罪,则某甲应受法律制裁。

”这一判断的逻辑形式是﹍﹍﹍﹍。

其中,逻辑常项是﹍﹍﹍﹍变项是﹍﹍﹍﹍5任何概念都有两个逻辑特征,即﹍﹍﹍﹍和﹍﹍﹍﹍。

6对概念进行限制和概括的逻辑根据是﹍﹍﹍﹍﹍﹍﹍﹍。

7﹍﹍﹍﹍﹍概念不能限制和划分。

8在真包含关系中,外延大的那个概念叫﹍﹍概念,外延小的那个概念叫﹍﹍概念。

9在“刑法就是规定犯罪和刑法的法律”这一定义中,被定义项是﹍﹍﹍﹍,种差是﹍﹍﹍﹍邻近的属概念是﹍﹍﹍﹍。

10任何一个性质判断都是由﹍﹍﹍﹍、﹍﹍﹍﹍、﹍﹍﹍﹍、﹍﹍﹍﹍四个部分组成的。

11主项和谓项都周延的性质判断的逻辑形式是﹍﹍﹍﹍。

12主项与谓项都不周延的性质判断的逻辑形式是﹍﹍﹍﹍。

13一个性质判断的谓项不周延,则这个判断的质是﹍﹍﹍﹍;一个性质判断的主项周延,则这个判断的量是﹍﹍﹍﹍。

14根据有关推理规则,﹍﹍﹍﹍判断不能换位。

15对SAP换质,其结论是﹍﹍﹍﹍;对SAP换位,其结论是﹍﹍﹍﹍。

16将“有些律师不是共产党员”换质,其结论是﹍﹍﹍﹍,再将所得结论换位为﹍﹍﹍﹍其推演的逻辑形式可用公式表示为﹍﹍﹍﹍﹍﹍﹍﹍。

17将“犯罪行为是具有社会危害性的”换质,其结论是﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍,将其结论再换位,其结论是﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍。

18如果SEP取值为真,则SIP取值为﹍﹍,SOP取值为﹍﹍。

19根据性质判断对当关系,如果SAP真,则SEP﹍﹍,SIP﹍﹍,SOP﹍﹍。

20当SEP和SOP都假时,S和P的外延之间具有﹍﹍﹍﹍和﹍﹍﹍﹍。

21任何一个三段论都包括并且只包括三个不同的项,即﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍。

22某有效三段论的大前提MOP,小前提应为﹍﹍﹍﹍,结论应为﹍﹍﹍﹍。

逻辑综合

13

设计读入

读入设计有多种方法,DC支持读入Verilog,VHDL,可以是RTL级代码,也 可以是门级网表,也可是ddc格式的文件。综合前的设计不需用RTL格式(虽 然也有其它格式)输入到DC中。 可以用以下命令读入设计: 1.analyze和elaborate命令:这是两个不同的命令,它使得设计人员可以在 建立设计通用逻辑之前先对设计进行语法错误和RTL转换分析。 2.read_file命令:如: read_file –format verilog sd_clk.v 3.read_verilog或read_vhdl命令,这些是从read_file中分离出来的命令, 如: read_verilog sd_clk.v 读入代码后用命令current_design和link将读入的设计和综合库连接起来。

2

3

综合过程中时序与面积的关系 从下图中可以看出面积与延迟的折衷关系,综合工具以约束为指导,在满足时 序的情况下获得最小面积。如果不施加约束,综合工具会产生非优化的网表, 而这是不能满足要求的网表。所以约束对于综合来说是必不可少的。

4

综合的基本流程 1.准备RTL代码:RTL代码经过前端仿真后才能用于综合。 2.定义库:设定好所需要用到的综合库等多种库。 3.读入设计:综合工具读入RTL代码并进行分析。 4.定义设计环境:设定设计的工作环境、端口的驱动和负载,线负载模型等 5.设置设计约束:这是综合的一个极其重要的环节,设定好正确的约束才能 得到正确的综合结果。约束要适当,不能过紧或过松。主要是定义时钟和I/O 的约束。 6.设置综合策略:有top-down和bottom-up两种策略,各有所长,对于不同的 设计要具体分析。 7.优化设计:综合工具可以根据约束对电路进行优化,也可以人为地加入命 令,改变优化方法。 8.分析和解决设计的问题:在设计综合(compile)后,根据报告来分析设计 中出现的问题,进而修订所出现的问题。 9.保存设计数据:综合完成后,保存各种数据,以供后续的布局布线使用( 需先通过验证)。 5

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一逻辑综合1 逻辑综合的含义实现在满足设计电路的功能,速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。

2 逻辑综合的原因RTL代码是理想的情况,在实际情况中会有门的延时,导线的延时,信号的转换时间及时钟信号到达各个触发器的时间不相等情况。

3综合的过程主要包括转译(Translation),优化(Optimization),映射(Mapping)三个过程。

3.1 转译:用HDL语言描述的电路转化为用GTECH库元件组成的逻辑电路的过程。

GTECH是synopsys的通用工艺库,它仅表示逻辑函数的功能,并没有映射到具体的厂家工艺库,是独立于厂家工艺的。

3.2优化:根据设计者对电路设定延时和面积等约束条件对电路进行优化设计的过程。

它通过各种方法尽量满足设计者对电路的要求。

3.3映射:把用GTECH库元件的电路映射到某一固定厂家的工艺库上,此时的电路包含了厂家的工艺参数Library Cells.4综合的目标:得到一个功能和时序都满足的网表。

达到面积最小化,功耗最小化和性能最大化。

二综合软件(DC)Design Compile是synopsys的综合软件,它的功能是把RTL级的代码转化为门级网表。

DC综合的流程如下:1 综合环境建立1.1 启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:1)、DC的安装目录;2)、用户的home目录;3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

search_path= search_path + {“.”, synopsys_ro ot + “/dw/sim_ver” }search_path= search_path + { “~/risc32/synthesis/libraries” }target_library={ tcb773stc.db }synthetic_library={dw_foundation.sldb}link_library = { “*”, dw_foundation.sldb, tcb773stc.db }symbol_library = { tcb773s.sdb }synlib_wait_for_design_license = {"DesignWare-Foundation"}alias rt “report_timing”designer= XXXXXc ompany= “ASIC Lab, Fudan Univ.”search_path指定了综合工具的搜索路径。

target_library:为综合的目标库,它一般是由生产线提供的工艺相关的库。

synthetic_library:综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

link_library:链接库,它是DC在解释综合后网表时用来参考的库。

一般情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。

symbol_library为指定的符号库。

synlib_wait_for_design_license用来获得DesignWare-Foudation的许可(license)。

alias语句与UNIX相似,它定义了命令的简称。

最后的designer和company项则表明了设计者和所在公司。

1.2 设计实体在DC中,总共有8种设计实体:设计(Design):一种能完成一定逻辑功能的电路。

设计中可以包含下一层的子设计。

单元(Cell):设计中包含的子设计的实例。

参考(Reference):单元的参考对象,即单元是参考的实例。

端口(Port):设计的基本输入输出口。

管脚(Pin):单元的输入输出口。

连线(Net):端口间及管脚间的互连信号。

时钟(Clock):作为时钟信号源的管脚或端口。

库(Library):直接与工艺相关的一组单元的集合。

2 逻辑综合的过程DC通过Script文件,自动完成模块的综合过程,其内容如下:2.1 向DC输入用Verilog或VHDL描述的设计: RTL design entry编码指南RTL级的HDL描述实际是电路结构的文本描述,它是技术无关的,类似于网表。

HDL语言先于综合工具出现,综合工具只能根据HDL代码进行逻辑推断,对完成同一功能而书写方式不同的HDL代码,综合工具会产生不同逻辑电路。

所以不能依靠DC去修正不符合规范的代码。

写代码时,需清楚描述的硬件电路拓扑结构。

RTL描述内容如下:寄存器的结构;电路的拓扑;寄存器之间的功能;DC仅对寄存器之间的逻辑进行优化,不会对寄存器的排列进行优化。

输入命令:read和analyze&elaborate,推荐用analyze&elaborateanalyze&elaborate允许设计者在设计的GTECH建立之前,首先去分析设计的语法错误和进行HDL代码转换。

Analyze做语法的检查并产生一个“.syn”文件,存储于work路径下的定义的设计库内,可供后来elaborate使用。

对于一个analyzed设备,只需用elaborate重新输入,节省时间。

Read就不行。

2.2 设定约束:Environment constraints定义设计的工艺参数,I/O端口属性,统计wire-load模型Set_operating_conditions:设置工作条件命令芯片供应商提供的库通常有max,type,min三种类型,代表操作环境为最坏(worst),典型(type),最好(best)三种情况。

芯片的操作环境包括:操作温度,供电电压,制造工艺偏差和RC树模型。

一般说来,电压越低,操作温度越高,工艺偏差系数越大,产品速度越慢,反之,速度越快。

当电压,温度和工艺偏差有波动的时候,乘以系数K因子来模拟这种影响计算延时。

Tree_type定义了环境的互连模型,通过定义这个值选取适当的公式来计算互连线的延迟。

如:命令set_operating_conditions –min BEST –max WORST 用于指示DC对设计的WORST 和BEST条件,同时优化。

Set_wire_load <wire-load model> -mode <top|enclosed|segmented>:设置连线负载模型向DC提供wire_load信息。

在DC综合的过程中,连线延时是通过设置连线负载模型确定。

连线负载模型基于连线的扇出,估计它的电阻电容等寄生参数,它由foundary提供。

根据导线负载模型(wire_load_model),DC可以估算出连线的电容,电阻和面积。

找出这条线所驱动的负载,得出其扇出数,通过以网表可以查出相应的线的长度。

通常技术库里包含许多负载模型,每一种wire-load模型都代表一定模块的尺寸。

导线负载模型模式(wireload model mode)用来选择穿过层次边界时的线的模型,有top,enclosed,segmented三种模式,如果不指定模式,默认的模式是top。

Set_load<value><object list> :设定输出负载综合出来的电路必须要驱动下一级电路,如果负载取得过小,下级电路无法正常工作,负载取得过大,会增大上一电路的难度。

用set_load命令可以设置端口或者线上的电容负载,从而保证输出路径的时序(transition time)。

set_driving_cell -cell<cell name> -pin<pin name> <object list>:设置输入驱动驱动是指施加到待综合电路的驱动能力。

如果取值不当,综合出来的电路就不能正常工作。

如果驱动太大,综合出来的电路的负载很大;驱动太小,信号的变化边沿会很差。

set_drive 命令用特定的驱动阻抗来设置输入端口的驱动强度。

保证输出路径的时序,确定输入信号的transition time。

在默认的情况下,DC认为驱动输入的单元的驱动能力为无穷大,即transition time 为0。

DRC的设计规则约束:set_max_transition <value> <object list>:设置最大传输时间Transition time是指改变某线所驱动的pin所需用的时间,该时间的计算方法是基于工艺库的。

输出的传输时间是输入传输时间及输出负载的函数关系。

DC在优化的过程中就是确保所有net的对应的传输时间小于所设定的最大传输时间。

set_max_capacitance <value> <object list>:设置线负载电容Transition time不能提供对net(线)的电容的直接控制,此命令可实现独立于传输时间约束的最大容值的约束。

对于连接输出pin上的net,其对应的容值是net本身的电容加上所连接的pin的容值,DC将这个计算结果与所设定的Max_capacitance比较,决定是否违反设计规则约束。

set_max_fanout <value> <object list>:设置最大扇出负载设置某线所能驱动的负载数量上线,如果某线的扇出负载过重,DC可通过改变单元的驱动强度来修正该约束违例的情况。

这些约束用于的input ports,output ports或current_design,一般在技术库内部设置。

当技术库的内部设置不能满足时,可用以上命令设置。

例如;set_max_transition 0.3 current_designset_max_capacitance 1.5 find(port,”out1”)set_max_fanout 3.0 all_outputs()2.3 设计和面积约束:Design and clock constraints描述设计的目标,包括时序和面积约束,要注意约束必须是可实现的,否则会导致面积超额,功耗增加或时序不能满足要求。

主要包括两点:●约束综合模块的最大面积(set_max_area )●约束综合模块timing path(Create_clock, Set_input_delay, Set_output_delay)IC代码的综合过程可以说就是时序分析过程,DC会将设计打散成一个个路经,这些路经上有cell延迟和net延迟,然后DC会根据加的约束,来映射库中符合这种延迟以及驱动的器件。