ISE软件使用说明

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

ISE使用教程(修改稿)

点击project菜单的New Source

设计输入

• 要完成这个计数器模块,可以在ISE自动生成的代 码框架基础上通过自己编写代码完成,也可使用 ISE的语言模板(ISE Language Template)工具 来完成。 • 选择Edit->Language Template或者通过点击工 具栏中最右端的灯泡按钮 来打开语言模板。 在语言模版(Language Template )窗口中,有 很多Xilinx提供的参考代码片断,找到需要的 counter代码片断。

功能仿真

• 首先在 Project Navigator 中创建一个 testbench 波形源 文件该文件将在 HDL Bencher 中进行修改 • 1. 在工程项窗口Project Window的源文件中选中计数器 (counter.vhd) • 2. 选择 Project -> New Source • 3. 在新的对话框中选择新文件类型为 Test Bench Waveform, 键入文件名为counter_tbw • 5. 点击 Next • 6. 点击 Next • 7. 点击 Finish • 此时HDL Bencher 程序自动启动并等候你输入所需的时 序需求

语言模版工具界面截图

设计输入

从 VHDL 综合模板中选择 计数器模板(Counter Template) 并把它拖动或粘 贴到源程序 counter.vhd 的 begin 和 end 之间

粘贴修改后的

Counter.vhd

设计输入

保存counter.vhd即 完成了设计输入

1.将输入好的 VHDL保存

1.选中

2.双击 编写完成后保存

自动布局布线

1.选中

2.双击

ISE使用指导

-3-

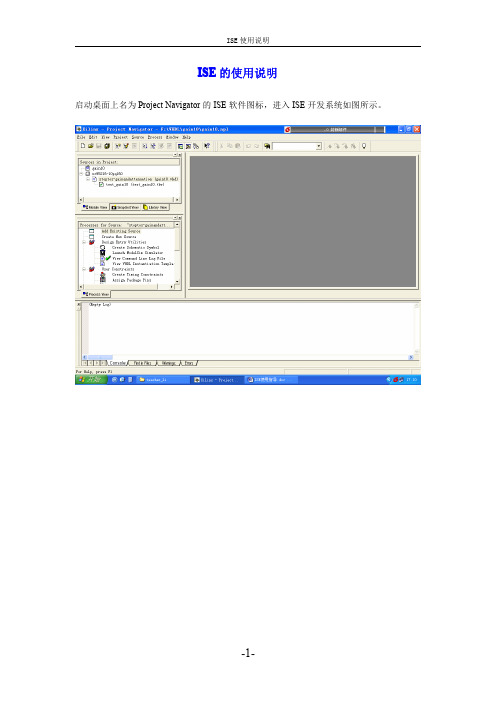

ISE 使用说明

下一步,进行可编程器件型号的选择以及设计流程的设置。在器件型号栏有 Device family , Device (型号) ,封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相 应选项。对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了 New Project Information 的设置。如图所示:

-9-

ISE 使用说明

count<="000000"; end if; elsif flag='1' and flag1='1' then if count<59 then count<=count+1; elsif count>=59 then count<="000000"; end if; end if; end if; end process; end Behavioral; -- flag='1' , 则进行 60 进制计数

然后单击工程 counter 下的子目录 count-Behavioral(count.vhd) , 接着在界面的 Processes for Source 一栏选择 Implement Design,进行布局布线的综合:

-15-

ISE 使用说明

然后工程名 counter 上单击右键,弹出对话框,选择新建 Test Bench Waveform,在 file 命名 为 test_counter。

在界面的 Processes for Source 一栏,是一系列综合工具。 Synthesize XST 工具一般可以分析 代码的语法错误,查看错误报告和 RTL 级的电路设计图。 单击 View Synthesis,出现如图所示对话框:

ISE软件说明

1.安装XILINX的ISE和EDK工具以及最新的Service Pack 安装如下图所示3个必须的工具。

iMPACT最低版本必须如下图所示:ISE最低版本必须如下图所示:XPS最低版本必须如下图所示:2.TS201板中CPLD和FPGA设计的目录结构将CPLD和FPGA设计的整个目录edk_ise_615拷入到微机的D:盘根目录下,使得整个目录结构看上去如下面所描述。

这一点很重要,否者打开工程时可能会出现缺各种文件的情况。

只要严格按本说明去操作,可以避免手工去修改工程的各项配置,可以顺利地熟悉整个T201板上CPLD和FPGA的设计工作。

目录结构和相应的ISE主工程文件:D:\edk_ise_615\cpld\pandr\cpld.iseD:\edk_ise_615\edk81\615htmii_ise\projnav\system.ise 不推荐使用D:\edk_ise_615\edk91\615htmii_ise\projnav\system.iseD:\edk_ise_615\edk91\615htgmii_ise\projnav\system.ise注意目录中还存在下列JTAG烧写文件:D:\edk_ise_615\edk81\615htmii_ise\ipf\prom_htmii.cdf 不推荐使用D:\edk_ise_615\edk81\615htmii_ise\ipf\all_htmii.cdf 不推荐使用D:\edk_ise_615\edk91\615htmii_ise\ipf\prom_htmii.cdfD:\edk_ise_615\edk91\615htmii_ise\ipf\all_htmii.cdfD:\edk_ise_615\edk91\615htgmii_ise\ipf\prom_htgmii.cdfD:\edk_ise_615\edk91\615htgmii_ise\ipf\all_htgmii.cdf说明:cpld目录是给TS201板上的CPLD工程用的;edk81目录代表TS201板上的FPGA工程是用8.1版本的EDK&ISE工具设计的;edk91目录代表TS201板上的FPGA工程是用9.1版本的EDK&ISE工具设计的,推荐使用最新版本的EDK&ISE工具,最好不要使用老版本;htmii表示的是hard temac mii的意思,即V4百兆硬核,该工程FPGA实现的是百兆网;htgmii表示的是hard temac gmii的意思,即V4千兆硬核,该工程FPGA实现的是千兆网;615htmii_ise和615htgmii_ise中的_ise表示工程最终的编译工具用的是ISE,也就是说先通过EDK设计好,然后输出到ISE,最后通过ISE编译完生成FPGA的BIT位流文件。

ISE教程

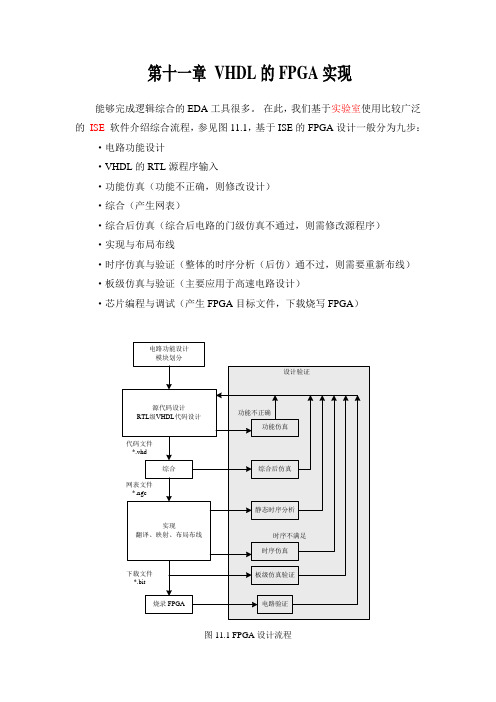

第十一章VHDL的FPGA实现能够完成逻辑综合的EDA工具很多。

在此,我们基于实验室使用比较广泛的ISE 软件介绍综合流程,参见图11.1,基于ISE的FPGA设计一般分为九步:·电路功能设计·VHDL的RTL源程序输入·功能仿真(功能不正确,则修改设计)·综合(产生网表)·综合后仿真(综合后电路的门级仿真不通过,则需修改源程序)·实现与布局布线·时序仿真与验证(整体的时序分析(后仿)通不过,则需要重新布线)·板级仿真与验证(主要应用于高速电路设计)·芯片编程与调试(产生FPGA目标文件,下载烧写FPGA)图11.1 FPGA设计流程在仿真模型中完全可以用VHDL来描述一项设计的时序特性,但在综合中,这些时序行为(如惯性或传输延迟)的描述都会被VHDL综合器忽略,而此设计的实际时序行为仅依赖于目标器件的物理结构和映射方式。

因此,若将设计模型从一个目标器件移植到另一个目标器件时,那些依赖于正确的延迟特性才能正常工作的VHDL模型,将不可能得到期望的综合结果和时序仿真效果。

仿真模型可以描述一些无限制的条件(如无穷循环或无范围限制的整型数),硬件却不能提供这些条件。

在某些情况下,如无穷循环或循环次数不确定的情况下,综合工具会产生错误并退出。

在其他的情况下,如无范围的整数,VHDL综合器会假设一个默认的表示方式,如以32bit二进制数表示无范围的整数。

尽管这是可综合的,但却无法生成所期望的电路。

11.2 VHDL的FPGA逻辑综合以下将以第七章例7.15交通信号灯监测电路的程序为例来说明如何对VHDL程序进行综合。

具体步骤如下:1.启动ISE如图11.2所示,在windows操作系统的开始菜单中启动Xilinx ISE Design Suite 10.1中的ISE主窗口,之后如图11.3。

图11.2 启动ISE 10.1图11.3 ISE 10.1 主窗口2.创建一个新的项目ISE 10.1主窗口打开后,选择创建一个新的项目,一般分为以下七步:(1) 单击【File】 【New Project …】命令,如图11.4.1,出现图11.4.2所示的【Create New Project】对话框。

ISE使用指南中

ISE使用指南中ISE(Integrated Software Environment)是一种软件开发工具,帮助开发人员编写和调试程序。

它提供了许多功能,使开发过程更加高效和容易。

本文将介绍ISE的基本使用指南,帮助初学者了解如何使用这个强大的工具。

安装ISE开始一个新项目在安装完成后,您可以打开ISE并开始一个新项目。

在“文件”菜单中选择“新建项目”,然后按照向导的指示操作。

在新项目设置过程中,您需要输入项目名称、目标设备、工作目录等信息。

确保所有信息都输入正确,然后点击“完成”按钮。

编写代码进行综合完成代码编写后,您需要进行综合。

综合是将高级代码转换为门级网表或其他低级描述的过程。

在ISE中,您可以通过选择“综合”选项来进行综合。

确保设置正确,然后点击“运行综合”按钮。

实现与映像调试一旦设计映像到目标设备,您可以进行调试。

在ISE中,您可以使用仿真器来模拟设计行为,并找出错误。

您还可以使用调试工具来分析信号波形、查看寄存器状态等。

确保所有功能都按照预期工作。

优化性能最后,您可以优化设计的性能。

在ISE中,您可以使用不同的优化技术来减少延迟、面积等。

通过调整参数和设置,您可以使设计更加高效和稳定。

确保优化后的设计满足性能要求。

总结在本文中,我们介绍了ISE的基本使用指南。

通过正确安装软件、开始一个新项目、编写代码、进行综合实现、调试和优化性能,您可以利用ISE开发高质量的程序。

希望这些信息对您有所帮助,祝您在使用ISE中取得成功!。

思科ISE部署手册说明书

部署•思科ISE部署术语,第2页•分布式思科ISE部署中的角色,第2页•配置思科ISE节点,第2页•支持多种部署方案,第4页•思科ISE分布式部署,第5页•部署和节点设置,第8页•日志记录设置,第17页•管理员访问设置,第20页•管理节点,第23页•支持管理节点的自动故障切换,第30页•策略服务节点,第31页•监控节点,第33页•监控数据库,第37页•配置用于自动故障切换的监控节点,第39页•思科pxGrid节点,第40页•查看部署中的节点,第47页•从MnT节点下载终端统计数据,第47页•数据库崩溃或文件损坏问题,第48页•设备的监控配置,第48页•同步主要和辅助思科ISE节点,第48页•更改节点角色和服务,第48页•在思科ISE中修改节点的影响,第49页•创建策略服务节点组,第49页•从部署中删除节点,第50页•关闭思科ISE节点,第51页•需要重新注册节点的场景示例示例,第52页•更改独立思科ISE节点的主机名或IP地址,第53页部署思科ISE部署术语思科ISE部署术语以下是讨论思科ISE部署方案时常用的术语:•服务:服务是角色提供的特定功能,例如网络访问、分析器、终端安全评估、安全组访问、监控和故障排除等。

•节点:节点是运行思科ISE软件的单个实例。

思科ISE可用作设备,也可用作能在VMware上运行的软件。

运行思科ISE软件的每个实例(设备或VMware)叫节点。

•角色:节点的角色决定节点提供的服务。

思科ISE节点可以承担以下任意角色:管理、策略服务、监控和pxGrid。

通过管理员门户可用的菜单选项取决于思科ISE节点承担的职责和角色。

•部署模式:决定您的部署是分布式、独立式还是作为基本双节点部署的独立式高可用性部署。

分布式思科ISE部署中的角色思科ISE节点可以承担管理、策略服务或监控角色。

思科ISE节点可以根据它承担的角色提供各种服务。

部署中的每个节点均可承担管理、策略服务和监控角色。

ISE软件使用说明

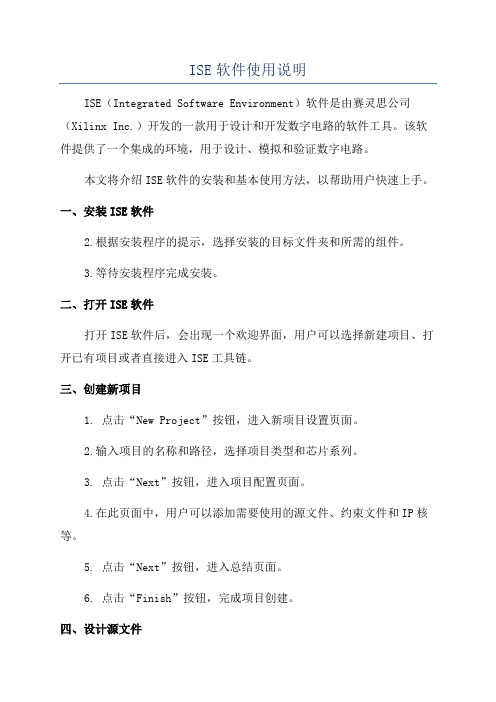

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

给出了整个工 程大致属性

Finish

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

完成后在Sources窗口中显 示工程文件夹以及工程所用 芯片。

在该窗口中右键

可以新建文件,添加已经写 好的文件,添加文件并复制 该文件到工程文件夹中。

Xilinx公司ISE10.1软件设计流程介绍

Xilinx公司ISE10.1软件设计流程介绍

--打开ISE软件时的面板

当以前使用 过该软件时会默 认打开上一个工 程。

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

选择芯片

选择综合工具 选择仿真工具 选择代码语言

--添加波形仿真文件

给出该波形 文件的相关 属性

Finish

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

注意选择

波形测试文件内容,具体 参考Blackboard中举例

波形测试文件,

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

注意选择

仿真时一定要点在 测试文件上

Next

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

这里可以新建一 个文件,也可以 在工程属性建立 完成后在工程内 新建,我们选择 Next

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

这里可以添加工 程文件,也可以 在工程建立后添 加,我们选择 Next

Xilinx公司ISE10.1软件设计流程介绍

双击进行仿真 仿真结果

--添加实体端口

Xቤተ መጻሕፍቲ ባይዱlinx公司ISE10.1软件设计流程介绍

--自动生成文件结构框架

双击gate文件 自动生成实体结构

生成了结构体框架 只需加入逻辑语句即可

Xilinx公司ISE10.1软件设计流程介绍

--添加代码及注释

添加的 逻辑代 码

--之后为 注释语句

Xilinx公司ISE10.1软件设计流程介绍

这个图标指示顶层文件 选中顶层文件,Processes窗口中 给出能操作的项目

双击XST进行综合操作

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

Next

Xilinx公司ISE10.1软件设计流程介绍

--添加波形仿真文件

选择所要仿真的 VHDL文件

Next

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

新建文件 的类型, 不同的类 型有着不 同的功能 和意义。

该文 件的 实体 名

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

Next

端口名

端口的类型及位数

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

给出了该文件 的概要

Finish

Xilinx公司ISE10.1软件设计流程介绍