第20章 IBIS模型原理和功能

走进IBIS模型

AN-715应用笔记One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106 • Tel: 781/329-4700 • Fax: 781/326-8703 • 走近IBIS 模型:什么是IBIS 模型?它们是如何生成的?作者:Mercedes Casamayor简介在进行系统设计时节省时间和降低成本是很关键的。

在原型制作之前,系统设计人员可以用模型来进行设计仿真。

在高速系统设计中正是如此,进行信号完整性仿真来分析不同条件下传输线中的电路行为,在设计初期就能预防并检测出典型的问题,例如过冲、欠冲、阻抗不匹配等。

然而,可用的数字IC 模型非常少。

当半导体厂商被索要SPICE 模型时,他们并不愿意提供,因为这些模型会包含有专有工艺和电路信息。

这个问题已经通过采用IBIS 模型来 (输入/输出缓冲器信息规范)解决,IBIS 也被称为ANSI/EIA-656,这是一个建模的新标准,在系统设计人员中越来越流行。

什么是IBIS ?IBIS 是一个行为模型,通过V/I 和V/T 数据描述器件数字输入和输出的电气特性,不会透露任何专有信息。

IBIS 模型与系统设计人员对传统模型的理解不同,例如其它模型中的原理图符号或多项式表达式。

IBIS 模型包括由输出和输入引脚中的电流和电压值以及输出引脚在上升或下降的转换条件下电压与时间的关系形成的表格数据。

这些汇总的数据代表了器件的行为。

IBIS 模型用于系统板上的信号完整性分析。

这些模型使系统设计人员能够仿真并预见到连接不同器件的传输线路中基本的信号完整性问题。

潜在的问题可以通过仿真进行分析,潜在的问题包括由传输线上阻抗不匹配导致的到达接收器的波形反射到驱动器的能量;串扰;接地和电源反弹;过冲;欠冲;以及传输线路端接分析等等。

Rev. 0 | Page 1 of 8IBIS 是一种精确的模型,因为它考虑了I/O 结构的非线性,ESD 结构和封装寄生效应。

IBIS 模型介绍及如何产生IBIS 模型

IBIS 模型介绍及如何产生IBIS 模型何为IBIS?IBIS 是一种可以利用V/I 和V/T 数据(不包含任何版权信息)描述一个器件的数字输入和输出端口电气特征的行为级模型。

IBIS 模型不同于传统系统设计师使用的原理图符号的常规理想化模型。

一个IBIS 模型是由输入和输出引脚上的电流和电压值,也可以是输出引脚上电平上升或下降转换过程中相关电压和时间组成的列表数据。

该表数据反映了器件行为。

IBIS 模型通常被用于系统板的SI 分析。

潜在的问题可以通过仿真分析得出由于传输线的阻抗失调而引发的能量反射大小;串扰、地或电源反弹、过冲及线端分析等。

IBIS 是一种精确的模型,因此可以用在非线性的I/O 特征、ESD 特征和封装寄生效应的描述。

在一些方面已经超越了传统模型的性能,如SPICE。

例如,在分析速度上要至少比SPICE模型仿真快25 倍,同时IBIS 还不像SPICE 模型那样存在版权问题。

IBIS 的发展历史:IBIS 最先由Intel 公司在1990 年提出。

在1993 年发布了IBIS 1.0 版本并且设立了IBIS 开放性论坛。

IBIS 开放性论坛由EDA 厂商、计算机制造商、半导体厂商、高校和终端用户组成,负责更新、修改和校对标准和组织研讨。

并在1995年与EIA(电子工业联盟)建立合作关系。

最新的IBIS 版本为4.0,在2002 年7月发布,但是目前仍然还不是ANSI/EIA 标准。

最早的IBIS 版本可以描述CMOS电路和TTL I/O 缓冲器,其后每个版本均添加新的功能,并且实现完全向下兼容。

如何创建一个IBIS 模型?通常可以利用采集仿真数据和仪器测量获取建立IBIS 模型所需的数据,另外,也可以将SPICE 模型直接翻译成IBIS 模型(可以从IBIS 官方网站/eig/ibis/ibis.htm 免费获得)。

模型可以从三个不同角度条件下创建:典型、最小化和最大化。

- 典型:在常温、常压和常规处理参数条件下;- 最小化:在高温、最低电压和小参数条件下;- 最大化:在低温、最高电压和大参数条件下;刨析IBIS 模型中的数据:在IBIS 规范中支持包括三态、开漏(open drain)、开集(open collector)、I/O 和ECL 等形式的多种类型输入输出端口。

ibis模型仿真培训教材

IBIS模型培训要点:模型的概论模型的分类模型的基本理论模型的检查连接器和过孔的模型一.模型的概论仿真的第一步离不开IBIS模型的收集,下面是关于模型的一些基本知识:模型产生的流程:模型的转换工具:上图中的IBIS to DML的转换的工具已经整合到Cadence的仿真工具中,DML是指DEVICE MODEL Language模型的精度:模型是否能够准确反映器件BUFFER的工作状态,直接关系到仿真的准确性,因此模型内部的检查是必须的:下面是一个模型的BUFFER的图与实际测量的结果对比:(二)模型的分类:模型的分类方式有两种:以文本格式的分类和以器件类型的分类以文本格式的分类:SPICE(典型的晶体管模型)同类的模型有PSPICE HSPICEIBIS (行为极的模型)器件类型分类的模型:DEVICE MODELIO BUFFER(Drive receive)Discrete deviceBoardmodelINTERCONNECT MODELTransmission lineConnectorCablePackageViaIBIS模型的定义:IBIS模型的作用:SPICE模型与SPICE模型的比较:三.IBIS的基本理论IBIS 模型的几种等效电路:IBIS模型版本的区别IBIS 1.1版本的时候,仅仅只是CMOS的电平无边沿控制,对于高速芯片的由电平的上升沿及下降沿控制的电路,显然不适用。

IBIS模型2.0版本最主要增加包括ECL的多总线支持,终端和漏极开路模型,差分I/O及复杂包装参数定义。

模型3。

2版本主要增加的是FBGA的PIN模型选择,及多级驱动和动态箝位 (所以特别注意的是当你拿到厂家给你的模型,首先要检查模型的版本信息,当然观察模型的曲线,版本越高级,曲线的精度越高,但是可能有些芯片的IBIS模型版本没有升级到那麽高,但是也要看是否可用,比如我这次有一个器件的模型中Buffer的类型是差分I/O,但是供应商给的版本是V2.0,模型中没有定义差分的关键字,由于差分模型是在V2.1以上版本才有,所以就必须和厂家联系重新给你更新版本的IBIS模型。

IBIS模型及其应用讲解

IBIS模型及其应用CDMA事业部眭诗菊摘要:本文介绍了用于高速系统信号完整性分析的IBIS模型的历史背景、IBIS模型的结构、IBIS模型的建模过程、IBIS模型的参数、语法格式,以及在使用IBIS模型时常遇到的问题和解决方法。

关键词:IBIS模型、EDA、信号完整性、缓冲器、单调性、收敛高时钟频率下运行的并行处理系统或其它功能更加复杂的高性能系统,对电路板的设计提出了极其严格的要求。

按集总系统的方法来设计这些系统的线路板已不可想象。

许多EDA (电子设计自动化)供应商都提供能进行信号完整性分析和EMC分析的PCB设计工具。

这些工具需要描述线路板上元器件的电气模型。

IBIS(I/O Buffer Information Specification)模型是EDA供应商、半导体器件供应商和系统设计师广泛接受的器件仿真模型。

一、IBIS的背景及其发展在IBIS出现之前,人们用晶体管级的SPICE模型进行系统的仿真,这种方法有以下三个方面的问题:第一,结构化的SPICE模型只适用于器件和网络较少的小规模系统仿真,借助这种方法设定系统的设计规则或对一条实际的网络进行最坏情况分析。

第二,得到器件结构化的SPICE模型较困难,器件生产厂不愿意提供包含其电路设计、制造工艺等信息的SPICE模型。

第三,各个商业版的SPICE软件彼此不兼容,一个供应商提供的SPICE模型可能在其它的SPICE仿真器上不能运行。

因此,人们需要一种被业界普遍接受的、不涉及器件设计制造专有技术的、并能准确描述器件电气特性的行为化的、“黑盒”式的仿真模型。

1990年初,INTEL公司为了满足PCI总线驱动的严格要求,在内部草拟了一种列表式的模型,数据的准备和模型的可行性是主要问题,因此邀请了一些EDA供应商参与通用模型格式的确定。

这样,IBIS 1.0 在1993年6月诞生。

1993年8月更新为IBIS 1.1版本,并被广泛接受。

此时,旨在与技术发展要求同步和改善IBIS模型可行性的IBIS论坛成立,更多的EDA供应商、半导体商和用户加入IBIS论坛。

IBIS 模型简介

IBIS 模型簡介IBIS(Input/Output Buffer Information Specification)模型是一種基於V/I曲線的對I/O BUFFER快速準確建模的方法,是反映晶片驅動和接收電氣特性的一種國際標準,它提供一種標準的檔格式來記錄如驅動源輸出阻抗、上升/下降時間及輸入負載等參數,非常適合做振盪和串擾等高頻效應的計算與仿真。

IBIS規範最初由一個被稱為IBIS開放論壇的工業組織編寫,這個組織是由一些EDA廠商、電腦製造商、半導體廠商和大學組成的。

IBIS的版本發佈情況為:1993年4月第一次推出Version1.0版,同年6月經修改後發佈了Version1.1版,1994年6月在San Diego通過了Version2.0版,同年12月升級為Version2.1版,1995年12 月其Version2.1版成為ANSI/EIA-656標準,1997年6月發佈了Version3.0版,同年9月被接納為IEC 62012-1 標準,1998年升級為Version3.1版,1999年1月推出了當前最新的版本Version3.2版。

IBIS本身只是一種檔格式,它說明在一標準的IBIS檔中如何記錄一個晶片的驅動器和接收器的不同參數,但並不說明這些被記錄的參數如何使用,這些參數需要由使用IBIS模型的仿真工具來讀取。

欲使用IBIS進行實際的仿真,需要先完成以下四件工作:1.獲取有關晶片驅動器和接收器的原始資訊源;2.獲取一種將原始資料轉換為IBIS格式的方法;3.提供用於仿真的可被電腦識別的佈局佈線資訊;4.提供一種能夠讀取IBIS和佈局佈線格式並能夠進行分析計算的軟體工具。

IBIS是一種簡單直觀的檔格式,很適合用於類似於Spice(但不是Spice,因為IBIS檔格式不能直接被Spice工具讀取)的電路仿真工具。

它提供驅動器和接收器的行為描述,但不洩漏電路內部構造的知識產權細節。

IBIS_model详解

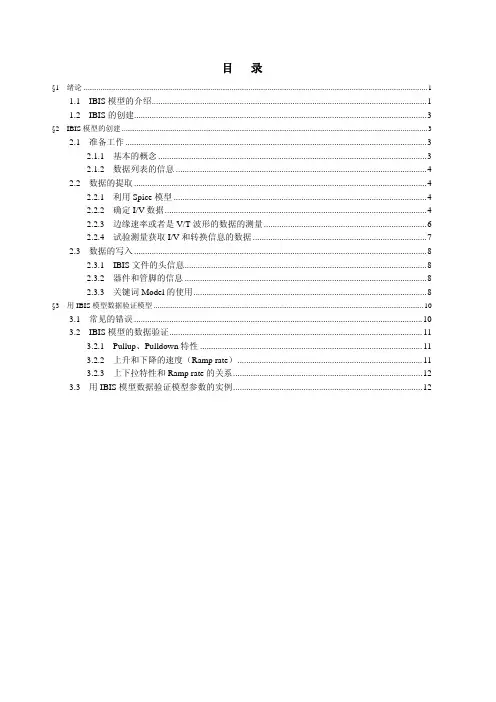

§1 绪论 .....................................................................................................................................................................................1

§3 用 IBIS 模型数据验证模型 ..............................................................................................................................................10

号 , [File Name] 文 件 的 名 称 , [File Rev] 文 件 的 版 本 号 , [Component] 器 件 的 名 称 和 [Manufacturer]. 器件的制造商。 2. 关于器件的封装电气特性和管脚与Buffer模型的映射关系。可以使用关键词 [Package] 和 [Pin] 描述。 3. 为了表述器件管脚的Buffer所需要的相关的数据信息。关键词 [Model] 是用来表示每个 Buffer的数据,具体的内容有:Model_type(Buffer的类型)、Vinh、Vinl以及C_comp (IC芯片的电容)。在前面的内容中提到了Buffer的特性描述,在IBIS模型中需要下面的一 些关键词描述:[Pull-up]、 [Pull-down]、[GND clamp]、[Power clamp]和 [Ramp]。当然对 于不同的Buffer可能不需要上面的全部的关键词来描述。如OC和漏极开路电路就不需要 [Pull-up] 关键词的数据信息。

IBIS模型及其应用讲解

CDMA事业部眭诗菊摘要:本文介绍了用于高速系统信号完整性分析的IBIS模型的历史背景、IBIS模型的结构、IBIS模型的建模过程、IBIS模型的参数、语法格式,以及在使用IBIS模型时常遇到的问题和解决方法。

关键词:IBIS模型、EDA、信号完整性、缓冲器、单调性、收敛高时钟频率下运行的并行处理系统或其它功能更加复杂的高性能系统,对电路板的设计提出了极其严格的要求。

按集总系统的方法来设计这些系统的线路板已不可想象。

许多EDA (电子设计自动化)供应商都提供能进行信号完整性分析和EMC分析的PCB设计工具。

这些工具需要描述线路板上元器件的电气模型。

IBIS(I/O Buffer Information Specification)模型是EDA供应商、半导体器件供应商和系统设计师广泛接受的器件仿真模型。

一、 IBIS的背景及其发展在IBIS出现之前,人们用晶体管级的SPICE模型进行系统的仿真,这种方法有以下三个方面的问题:第一,结构化的SPICE模型只适用于器件和网络较少的小规模系统仿真,借助这种方法设定系统的设计规则或对一条实际的网络进行最坏情况分析。

第二,得到器件结构化的SPICE模型较困难,器件生产厂不愿意提供包含其电路设计、制造工艺等信息的SPICE模型。

第三,各个商业版的SPICE软件彼此不兼容,一个供应商提供的SPICE模型可能在其它的SPICE仿真器上不能运行。

因此,人们需要一种被业界普遍接受的、不涉及器件设计制造专有技术的、并能准确描述器件电气特性的行为化的、“黑盒”式的仿真模型。

1990年初,INTEL公司为了满足PCI总线驱动的严格要求,在内部草拟了一种列表式的模型,数据的准备和模型的可行性是主要问题,因此邀请了一些EDA供应商参与通用模型格式的确定。

这样,IBIS 在1993年6月诞生。

1993年8月更新为IBIS 版本,并被广泛接受。

此时,旨在与技术发展要求同步和改善IBIS模型可行性的IBIS论坛成立,更多的EDA供应商、半导体商和用户加入IBIS论坛。

IBIS模型简介

IBIS 模型简介

IBIS(Input/Output Buffer Information Specification)模型是一种基于 V/I 曲线的 对 I/O BUFFER 快速准确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,它提 供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入负载等参数,非常适 合做振荡和串扰等高频效应的计算与仿真。

IBI驱动器 和接收器的不同参数,但并不说明这些被记录的参数如何使用,这些参数需要由使用 IBIS 模 型的仿真工具来读取。欲使用 IBIS 进行实际的仿真,需要先完成以下四件工作:

(1)获取有关芯片驱动器和接收器的原始信息源; (2)获取一种将原始数据转换为 IBIS 格式的方法; (3)提供用于仿真的可被计算机识别的布局布线信息; (4)提供一种能够读取 IBIS 和布局布线格式并能够进行分析计算的软件工具。

IBIS 模型的分析精度主要取决于 I/V 和 V/T 表的数据点数和数据的精确度。由于基于 IBIS 模型的 PCB 板级仿真采用查表计算,因而计算量较小,通常只有相应的 SPICE 模型的 1/10 到 1/100。

采用 SPICE,产品推向市场的时间取决于获得模型,得到仿真结果的时间;在 IBIS 中, 主要是从 SPICE 仿真界果中建立模型。换句话说, IBIS 模型能够很容易的验证产品测试结 果(并且,如果有必要产生新的模型)。如果同样进行测量和模型验证的话,IBIS 模型能够 同 SPICE 具有同样的精度。IBIS 模型提供的信息需要 I/O 传输特性、而不是内部电路的信息。 IBIS 是为了满足信号完整性(SI)仿真的需要,其结果是 IBIS 模型具有信号完整性(signal integrity)分析所需要的信息,如在不同的负载下信号上升/下降时间。由于提取的水平如 此之高,所以模型不能够很容易的调整大小,但是对于信号完整性(SI)的应用不成问题。

ibis模型的基本知识[中国pcb论坛网]

[原创]IBIS模型的基本知识[中国PCB论坛网]IBIS模型的基本知识--------------------------By Yinko----------------------IBIS模型的由来随着数字系统性能的不断提升,信号输出的转换速度也越来越快,在信号完整性分析中,不能简单的认为这些高速转换的信号是纯粹的数字信号,还必须考虑到它们的模拟行为。

为了在PCB进行生产前进行精确的信号完整性仿真并解决设计中存在的问题,要求建立能描述器件I/O特性的模型。

这样,Intel最初提出了IBIS的概念,IBIS就是I/O Buffer Information Specification的缩写。

为了制定统一的IBIS格式,EDA公司、IC供应商和最终用户成立了一个IBIS格式制定委员会,IBIS公开论坛也随之诞生。

在1993年,格式制定委员会推出了IBIS的第一个标准Version 1.0,以后不断对其进行修订,现在的版本是1999年公布的Version 3.2,这一标准已经得到了EIA的认可,被定义为ANSI/EIA-656-A标准。

每一个新的版本都会加入一些新的内容,但这些新内容都只是一个IBIS模型文件中的可选项目而不是必须项目,这就保证了IBIS模型的向后兼容性能。

现在,已经有几十个EDA公司成为IBIS公开论坛的成员,支持IBIS的EDA公司提供不同器件的IBIS模型以及软件仿真工具。

有越来越多的半导体厂商开始提供自己产品的IBIS 模型。

IBIS与SPICE的比较SPICE作为一种通用的电路模拟语言,最早由加州大学伯克利分校发明。

SPICE模型是对电路中实际的物理结构进行描述。

由于其精确性和多功能性,已经成为电子电路模拟的标准语言。

SPICE模型目前有两个主要的版本:HSPICE和PSPICE,HSPICE主要应用于集成电路设计,而PSPICE主要应用于PCB板和系统级的设计。

采用SPICE模型在PCB板级进行SI分析时,需要集成电路设计者和制造商提供能详细准确的描述集成电路I/O 单元子电路的SPICE模型和半导体特性的制造参数。

二极管的ibis模型 -回复

二极管的ibis模型-回复二极管的IBIS模型是一种常用的仿真模型,用于对二极管的电性能进行建模和分析。

本文将从何为IBIS模型开始,逐步介绍二极管的IBIS模型的原理、构建流程和应用,帮助读者了解和应用IBIS模型。

一、何为IBIS模型IBIS(I/O Buffer Information Specification)模型是由美国电子产业协会(EIA)和JEDEC协会共同推出的电子设备仿真模型规范。

它定义了各种电子元件和封装的行为,使得设计工程师能够通过仿真软件在计算机上模拟和测试设计的电路性能。

IBIS模型一般包括电源、输入/输出特性、逻辑功能和封装等各个方面的模型。

二、二极管的IBIS模型原理二极管是最简单的电子元件之一,它具有单向导电性,可以将电流只向一个方向流动。

二极管的IBIS模型主要包括两个方面的参数:电压-电流特性和电容特性。

1. 电压-电流特性:二极管的IV曲线是描述二极管导通特性的一个重要参数。

在导通情况下,二极管的电压-电流特性可以用指数形式进行建模,即I = I_s * (e^(V/V_T) - 1),其中I_s为饱和电流,V_T为热电压。

2. 电容特性:二极管存在电容效应,主要分为空乏电容和扩展空乏电容。

空乏电容是指在二极管正向偏置情况下,由于耗尽层与扩散区之间的电荷分布不均匀导致的电容效应。

扩展空乏电容是指在二极管反向偏置情况下,由于扩散区发生摩尔结空乏现象导致的电容效应。

这些电容可以通过等效电容和等效电阻的方式建模。

三、二极管IBIS模型的构建流程构建二极管的IBIS模型需要经历以下几个步骤:1. 收集数据:通过实验或者仿真软件获取二极管的电压-电流特性和电容特性的数据。

可以用仪器测量实际二极管的IV曲线,并通过采样等方法获取所需数据。

2. 参数拟合:根据收集到的数据,用合适的数学模型进行参数拟合,以得到合适的模型参数。

在二极管的电压-电流特性方面,可以用指数模型进行参数拟合;在电容特性方面,可以用等效电容和等效电阻进行建模。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3

IBIS模型定义

IBIS模型用于对系统板上的信号完整性进行分析。

通过IBIS模型,系统设计人员能够仿真并预见连接不同器件的传输线路 中基本的信号完整性问题。

IBIS是一种精确的模型,这是因为模型考虑了I/O结构的非线性,ESD 结构和封装寄生效应。

Copyright © 2009 Altium Limited

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输出模型

封装参数

R_Pin、L_Pin和C_Pin是每个引脚到缓冲器连接的电阻、电感和电容 的电气特性。

R_Pkg、L_Pkg和C_Pkg是整个封装的集总值。与C_Comp参数一样, 最大的值以最大值列出,最小的值以最小值列出。

IBIS模型原理和功能

何宾 2015.07

学习内容和目标

IBIS模型定义 IBIS发展历史 IBIS模型生成 IBIS模型所需数据 IBIS文件格式 IBIS模型验证

Copyright © 2009 Altium Limited

2

IBIS模型定义

IBIS是一个行为模型,通过V/I和V/T数据,描述器件数字输入和 输出的电气特性,而不会泄露任何元器件专有的信息。

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输出模型

在–VCC至2×VCC的范围内,获得所需要的数据。 虽然这个电压范围超过了半导体厂商在器件手册中指出的绝对最大额定

值,但是这个范围覆盖了传输线中可能发生的欠冲、过冲和反射情况。 因此,驱动器和接收器需要使用这个电压范围建模。 注:下拉数据是相对于GND的,而上拉数据是相对于VCC的。由于输出电流取 决于输出端和VCC引脚之间的电压,而不是输出端和接地引脚之间的电压。 所以,IBIS文件中的上拉数据应按照下面的表达式输入:

IBIS文件包括三个主要部分:

头文件或关于文件、器件和公司的一般信息。 器件名称、引脚排列和引脚到缓冲器映射。 每个模型的I/V和V/T数据。 IBIS模型可包含多个器件的特征。在这种情况下,第2和第3点随包含的

器件而重复多次。

Copyright © 2009 Altium Limited

对于输出模型,有一些参数应包含在文件中,对时序要求进行后 端仿真。这些时序测试用于测试:

负载和测量点是测试负载电容值(CREF)。 测试负载电阻值(RREF)。 测试负载上拉或下拉参考电压(VREF)。 输出电压测量点(VMEAS)。 当指定传播延迟和/或器件输出切换时间时,他们与半导体厂商使用的测

Copyright © 2009 Altium Limited

IBIS模型验证 --内容

此后,应采用不同EDA厂商提供的多种IBIS仿真器在不同标准负载下运 行模型。这些厂商包括HyperLynx、Cadence和Avanti Corporation。

7

IBIS模型生成

可以通过仿真过程中或基准测量中收集的数据来获得IBIS模型

如果选择前一种方法,可以在使用SPICE进行仿真时,收集每个输出/ 输出缓冲器的V/I和V/T数据。

这样,可以在模型中包含过程转折数据。然后,使用IBIS网站上的 SPICE至IBIS转换程序,由yright © 2009 Altium Limited

9

IBIS模型生成

每种条件会产生相应的典型、慢速和快速模型。即:

具有快速转换时间和最小封装特性的最高电流值条件下生成快速模型。 具有较慢转换时间和最大封装值的最低电流值条件将生成慢速模型。

如果数据是在实验室测量中获得的,那么模型取决于器件的特性 。如果是标称器件,将获得典型模型。

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输出模型

上拉数据描述当输出为逻辑高电平状态,即:PMOS晶体管导通时的I/V 行为。

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输出模型

下拉数据表示当输出为逻辑低电平状态,即:NMOS晶体管导通时的直 流电气特性。

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输出模型

C_Comp

这是硅芯片电容,不包括封装电容。它是焊盘与驱动器之间的电容. C_Comp是关键参数,特别是对于接收器的输入。C_Comp对于每个不

同转折点(最小、典型和最大)都有一个对应值。 C_Comp最大的值应在最大转折点之下,最小值应在最小转折点之下。

Copyright © 2009 Altium Limited

IBIS模型生成

收集完数据后,将其以可读的ASCII文本格式存入文件中。 Golden Parser,也称为ibischk3,用于根据标准检查IBIS文件的 句法和结构。

IBIS规范支持几种输入和输出,例如:

可建模为三态、集电极开路、开漏、I/O和ECL的输入/输出。

IBIS开放式论坛包括EDA厂商、计算机制造商、半导体厂商、大学和终 端用户

它负责提议进行更新和评审、修订标准,组织会议。它促进IBIS模型的 发展,在IBIS网站上提供有用的文档和工具。

Copyright © 2009 Altium Limited

6

IBIS发展历史

1995年,IBIS开放式论坛与电子工业联盟(EIA)开始进行合作

一个PMOS晶体管和一个NMOS晶体管 两个ESD保护二极管 芯片电容和封装寄生电容

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输出模型

通过直流电气数据、交流或转换数据以及参数输出模型,对该模型 进行描述 上拉和下拉曲线

上拉和下拉数据决定器件的驱动强度。如下图所示,这些曲线通过特征 化输出中的两个晶体管来获得。

IBIS模型与系统设计人员对传统模型的理解不同,比如:其它模 型中使用原理图符号或多项式表达式。

IBIS模型包括:

输出和输入引脚中的电流和电压值的关系。 在上升或下降的转换条件下,输出引脚的电压与时间关系。 这些数据代表了器件的行为。

Copyright © 2009 Altium Limited

Copyright © 2009 Altium Limited

IBIS的器件及引脚信息

封装参 数

IBIS文件格式 -- IBIS器件模型数据

对模型的描述

时序测试负载和芯片 电容

IBIS器件模型数据(1)

Copyright © 2009 Altium Limited

IBIS文件格式 -- IBIS器件模型数据

包括从ESD二极管获得的电源和GND箝位数据。这些曲线遵照用 于输出端的相同的程序生成。 扫描电压范围:

对于GND箝位是–VCC至VCC, 对于电源箝位曲线是VCC至2 × VCC。

此外,由于电源箝位数据是相对于VCC的,它需要以 VTABLE=VCC– VIN的方式输入文件中。

IBIS模型所需数据 --其他参数

4

IBIS模型定义

相对于其它传统模型(例如:SPICE)来时,IBIS模型有以下优 势:

仿真时间最多可缩短25倍。 IBIS没有SPICE不收敛的问题。 IBIS可以在任何行业平台运行。

Copyright © 2009 Altium Limited

5

IBIS发展历史

IBIS模型由Intel公司在上世纪90年代初开发。IBIS 1.0版本于 1993年6月发布,IBIS开放式论坛也在那时成立。

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输入模型

其模型可视为接收器。它包括:

两个ESD保护二极管。 芯片电容。 封装寄生电容。

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输入模型

这些元件构成输入特性的V/I曲线。 在这种情况下,除了封装寄生和C_Comp参数外,输入端模型也

Golden Parser,也称为ibischk3,是对文件的句法和结构进行核对的程 序,确保其符合IBIS规范。

接下来,设计者应该对从文件中生成的I/V和V/T曲线进行检查,确保结 果和预期是一致的。

可以使用Innoveda公司提供的Visual IBIS Editor完成,该软件可从IBIS 网站免费获取。

Copyright © 2009 Altium Limited

IBIS模型所需数据 --输出模型

斜坡速率和切换波形

斜坡速率,即:dV/dt,描述乐输出端从当前逻辑状态切换到其它逻辑 状态的转换时间默认在50欧姆阻性负载条件下,在20%和80%点测得斜 率。

下降和上升波形给出器件在驱动连接到地和VDD的阻性负载从高电平到 低电平和从低电平到高电平所需的时间。

IBIS文件格式 -- IBIS的文件头部和一般信息

以下部分显示了IBIS文件的主要部分。

括号内的文字被称为关键字; 它们中的一些是可选的; 其它的必须被包括。

关键字

Copyright © 2009 Altium Limited

IBIS文件格式 -- IBIS的器件及引脚信息

指定的引脚模 型

I/V下拉数据

Copyright © 2009 Altium Limited

IBIS器件模型数据(2)

IBIS文件格式 -- IBIS器件模型数据

切换波形

IBIS器件模型数据(3)

IBIS文件格式 -- IBIS器件模型数据

斜坡速率

IBIS器件模型数据(4)

IBIS模型验证 --内容

一旦生成了IBIS文件,就必须对这个文件所包含的IBIS模型进行 验证。

目前,已经发布了几个IBIS版本。第一个版本描述了CMOS电路和TTL I/O缓冲器。