近阈值非预充静态随机存储器

静态随机存储器工作原理

静态随机存储器工作原理

静态随机存储器(Static Random Access Memory,SRAM)是

一种用于计算机内存的存储设备,其工作原理是利用存储电路中的稳定电荷储存信息。

SRAM由一组双稳态触发器构成,每个触发器可以储存一个

二进制位(bit),这些触发器以交叉反馈方式连接,形成稳

定的存储单元。

每个存储单元都有两个稳定的状态,即0和1,分别对应着低电平和高电平的电信号。

SRAM的读写操作是通过控制信号来完成的。

当要读取某个

存储单元的值时,控制电路将相应行线选通,并将其连接到读取电路,读取电路通过放大和判别电路将单元的电平状态转换为相应的输出信号。

当要写入某个存储单元的值时,控制电路将相应行线选通,并将写入数据送入存储单元,存储单元根据输入数据的电平状态来改变其状态。

SRAM相对于动态随机存储器(DRAM)来说,具有读写速

度快、读写可靠性高的特点,但也相应占用较大的面积和功耗较高。

因此,在计算机系统中,SRAM通常用于高速缓存等

需要快速读写的存储器部分。

静态随机存储器单粒子翻转效应截面的蒙特卡罗模拟

静态随机存储器单粒子翻转效应截面的蒙特卡罗模拟高丽娟; 白彩艳【期刊名称】《《山西师范大学学报(自然科学版)》》【年(卷),期】2019(033)003【总页数】5页(P40-44)【关键词】单粒子翻转效应; 截面; Geant4; 重离子【作者】高丽娟; 白彩艳【作者单位】晋中学院数理学院山西晋中030619【正文语种】中文【中图分类】O571.1; O572.2近三十年来,单粒子翻转(SEU)分析的理论和实验分析均基于长方体(RPP)模型,但是该模型在评估亚微米和纳米器件时会出现较大的偏差[1~6].这主要是因为尺寸较小的器件对电荷更加敏感,发生单粒子效应需要的临界电荷更少,仅为fC级,即使很少的电荷被收集,也会使器件发生单粒子翻转,而RPP模型仅将离子的径迹描述为一条直线,没有考虑其具体的径迹分布,造成电荷收集的模拟不够准确.对于小尺寸的器件来说,详细的描绘离子的径迹(直接电离或核反应)显得更为重要.随着计算机模拟技术的发展,人们更偏向于使用蒙特卡洛方法结合器件仿真软件来评估器件的可靠性,近年来,Kevin等人提出一种新的模拟计算方法[7],这种方法可以弥补RPP模型的不足,对器件的SEU评估有较准确的模拟结果.Kevin等人的模拟主要基于0.25 μm的静态随机存储器(SRAM).本文将针对更小尺寸的SRAM(0.15 μm),基于蒙特卡罗软件Geant4 来进行单粒子翻转效应的模拟.表1 实验用离子及其参数Tab.1 The experiment ions and their parameters离子种类离子能量(MeV)表面LET(MeV·cm-2/mg)射程(μm)Li47.30.42282.7C32.5803.111.7335.49127.1F1004.4372.65Si1508.8057. 84Cl16512.947.69Ti17021.934.85Br23041.931.40图1 器件的单粒子翻转截面Fig.1 SEU cross section of the SRAM1 实验介绍及结果本次实验中选取日本瑞萨公司0.15 μm工艺16 M的静态随机存储器(型号R1LV1616RSA)作为测试对象,在中国原子能科学研究院HI-13串列加速器上对其进行了单粒子翻转效应实验.实验中选择的离子种类及参数如表1所示.经过测试,该器件的单粒子翻转截面如图1所示.图中横坐标为离子零度入射器件时的有效LET.在计算有效LET时,考虑了器件敏感区上方的覆盖层厚度.纵坐标为得到的单粒子翻转截面,图中的误差为统计误差.2 单粒子翻转的蒙特卡罗模拟2.1 物理过程的选取在微电子器件的单粒子效应模拟中,离子径迹是模拟计算电荷收集、瞬态脉冲和节点电压变化等的重要参数,其精度会影响单粒子效应的模拟结果.本工作使用Geant4模拟SRAM的单粒子翻转截面,必须选择合适的物理模型,得到较准确的电荷沉积,才能获得较为准确的计算结果.离子入射Si材料,如仅考虑直接电离,除主径迹之外还需考虑δ电子(可以发生三次以上电离的电子)电离沉积的能量,若离子能量较高,还要考虑核反应过程.理论研究表明,随着器件特征尺寸的减小和重金属(Cu、Au等)的使用,δ电子和核反应已成为器件发生单粒子效应的原因[8~12].因此模拟时要针对主离子和电子选择物理过程和模型,对Li离子还添加了核反应过程.对于电子选择了Geant4中的Penelope(PENetration and Energy Loss of Positron and Electrons)代码.在该代码中包含了光子、电子和正电子的一系列物理过程.对重离子能量损失的模拟主要选择了G4ionIonisation类,该类包含了BetherBloch模型、 Bragg模型和BraggIon模型.为了验证物理过程选取的准确性,计算了δ电子和300 MeV/n Fe离子的阻止本领(图2和图3).图2为电子射程随能量的变化,从图中可以看到本次工作中阻止本领与其他结果有较好的一致性[13~18],尤其是电子的射程与Xapsos[17]的结果几乎吻合.图3为300 MeV/n Fe离子的阻止本领随射程的变化,从图中可以看到在射程小于1 000 nm大于10 nm的范围内,本次工作的结果与Colladant[18]和Akkerman[13]的结果都有较好的一致性,但是当射程小于10 nm时,本次结果和Colladant的结果都逐渐小于Akkerman的结果.而当射程大于1 000 nm 后,随着射程的增大,本次计算结果与Colladant的结果相差也越来越大.造成这Energe (eV)Radial distance (nm)图2 电子射程随能量的变化Fig.2 Dependence of electronic range on the energy图3 300 MeV/n Fe离子阻止本领随射程变化Fig.3 Dependence of stopping ability on radial distance for 300MeV/n Fe ion些差别的原因主要是计算代码不同,其中的物理模型的精度也有所不同.这些差别不会影响下面的计算.2.2 模型介绍本文所采用的器件为商用器件,很难获取准确的参数,同时采用经验模型来构建器件的敏感体积,这种敏感体积是一种线性关联的权重敏感体积,如下式所示.其中,αi为权重因子,用来度量电荷收集效率,它代表由能量Ei收集到电荷Q的效率因子.总的电荷收集是N个敏感体积中沉积能量权重分布的总和.如果N=1,则模型过渡为RPP模型.假设:(1)截面曲线的形状完全是来自内在单元的电荷收集效率,敏感体积的表面积直接与重离子截面相关;(2)敏感体积为同轴的立方体;(3)敏感体积的深度相同;(4)体积中的电荷收集效率α是归一的(在所有体积重叠的部分,α=1)通过假定1,LET 对应En的敏感区域可以由式(2)描述,公式中的E0,σsat,s和w是威布尔拟合参数.(2)An的计算是任意的,可以根据式(3)来选择,其中n取值为0到N-1.(3)点数N对应于模拟中敏感体积的个数,第n个敏感体积的效率αn由式(4)给出, 式中u是单位阶跃函数,Ec是 En到En+1之间的能量值,由式(5)计算得到, 式(4)中的单位阶跃函数是为了满足假定4,即式(6).(4)(5)(6)由于敏感体积设计为同轴的,通过式(6),第0个体积中的净电荷收集效率为100 %.该敏感体积的深度D与阈值LET0处的临界电荷(单位:fC)相关,LET单位为MeV·cm-2/mg,深度单位为μm,它们的关系如式(7)所示.在模拟计算时,必须根据已有的信息,预先假定一个临界电荷或敏感体积深度D.Qcrit(fC)=10.35·LET0·D(7)构建好灵敏体积后,将其放置在另一个代表存储单元的体积中,令离子随机入射存储单元的表面,统计在灵敏体积中沉积的能量大于临界电荷的粒子数占总粒子数的比例,再乘以存储单元的面积S则可以获得器件的截面.3 单粒子翻转效应截面模拟3.1 截面拟合首先对器件的实验数据进行Weibull拟合,Weibull函数如式(8)所示σ=σsat×{1-exp[-(L-E0)/W]s}(8)拟合时,截面的误差为统计误差,认为分布在2倍标准偏差范围内的数据为有效数据,即置信区间为95 %.采用约化χ2来评价拟合结果.通过多次拟合,得到的最佳拟合参数如表2所示.3.2 敏感体积构建获得拟合参数后,拟构建10个权重敏感区,即N=10,再利用式(2)~式(5)计算每个敏感区的面积和电荷收集效率,计算结果如图4所示.表2 Weibull函数拟合参数Tab.2 The fitting parameters of Weibull Function 参数σsatE0sWχ2/n拟合值2.62e-90.95.4516.412.71图4 权重敏感体积的面积和电荷收集效率Fig.4 Dependence of the area of the weight sensitive volume on the charge collection efficiency图5 存储单元示意图Fig.5 Storage unit schematic diagram构建好权重灵敏体积后,将其放置在构建的存储单元中(图5),图中的SV即权重灵敏体积.在灵敏区上方设置了厚度为8 μm的Si覆盖层,存储单元的衬底也是Si 材料.另外,我们假定敏感区深度为漏区反偏pn结的耗尽层宽度,约为0.25 μm,Si衬底为10 μm.3.3 计算结果本次模拟计算了实验中使用的所有离子,其中Li离子考虑了核反应,模拟中的入射粒子数为5×107结果,结果如图6所示.图中黑色原点为计算结果,方框为上文中的实验结果,可以看到,计算结果与实验结果有较好的一致性,尤其是F、Si、Cl和Ti离子的结果与实验结果吻合得更好.图6 截面随LET的变化Fig.6 Dependence of cross section on LET4 结语本文基于蒙特卡罗软件Geant4,建立合理的经验模型,模拟计算了0.15 μm工艺的SRAM的单粒子翻转截面,结果表明该经验模型适用于亚微米特征尺寸的器件,对器件的评估有重要的意义.【相关文献】[1]Dodd P E, Shaneyfelt M R, Horn K M, et al.SEU-sensitive volumes in bulk and SOI SRAMs from first-principles calculations and experiments [J].IEEE Trans NuclSci,2003,489(6):1893~1903.[2]Schwank J R, Dodd P E, Shaneyfelt M R, et al.Charge collection in SOI capacitors and circuits and its effect on SEU hardness [J].IEEE Trans Nucl Sci, 2002, 49(6): 2937~2947. [3]Reed R A, Marshall P W, Kim H, et al.Evidence for angular effects in protoninduced single-event upsets [J].IEEE Trans Nucl Sci,2002,49(6):3038~3044.[4]Reed R A,McNulty P J, Abdel-Kader W G.Implications of angle of incidence in SEU testing of modern circuits [J].IEEE Trans Nucl Sci,1994, 41(6): 2049~2054.[5]Weller R A, Sternberg A L, Massengill L W, et al.Evaluating average and atypical response in radiation effects simulations [J].IEEE Trans Nucl Sci,2003,50(6):2265~2271. [6]Petersen E L.Predictions and observations of SEU rates in space [J].IEEE Trans Nucl Sci,1997,44(6):2174~2187.[7]Kevin M Warren, Rorbert A Weller.Application of RADSAFE to model the single evevt upset respose of a 0.25 μm CMOS SRAM [J].IEEE Trans Nucl Sci,2007,54(4):898~903. [8]Dodd P E, Schwank J R, Shaneyfelt M R, et al.Impact of heavy ion energy and nuclear interactions on single-event upset and latchup in integrated circuits[J].IEEE Trans Nucl Sci,2007,54(6):2303~2311.[9]Warren K M, Weller RA, Mendenhall M H,et al.The contribution of nuclear reactions to heavy ion single event upset cross-section measurements in a high-density SEU hardened SRAM [J].IEEE Trans Nucl Sci,2005,52(6):2125~2131.[10]Kobayashi A S, Ball D R, Warreb K M, et al.The effect of metallization layers on single event susceptibility[J].IEEE Trans Nucl Sci, 2005, 52(6):2189~2193.[11]Melanie Raine, Marc Gaillardin.Effect of the ion mass and energy on the response of 70 nm SOI transistors to the ion deposited charge by direct Ionization [J].IEEE Trans Nucl Sci,2005,57(4):1892~1899.[12]King M P, Reed R A, Warren R A, et al.The impact of delta-rays on single-event upsets in highly scaled SOI sRAMs [J]. IEEE Trans Nucl Sci, 2010, 57(6):3169~3175.[13]Akkerman A, Barak J, Emfietzoglou D, et al.Ion and electron track-structure and its effects in silicon:model and calculations [J].Nuclear Instruments and Methods in Physics Research B,2005,227:319~336.[14]David K Brice.Stopping powers for electrons and positrons ICRU report37:international commission on radiation units and measurements[J].Nuclear Instruments and Methods in Physics Research Section B,1985,12(1):187~188.[15]Hamm R N.Dose calculations for Si-SiO2 layred structures by X rays and Co-60 gamma rays [J]. IEEE Trans Nucl Sci,1986,33(6):1236~1239.[16]Kuhr J Ch, Fitting H J.Monte Carlo simulation of electron emission from solids [J].Electron Spect Relat Phenom,1999,105:257~273.[17]Xapsos M A.Applicability of LET to single events in microelectronic structures [J].IEEETrans Nucl Sci,1992,39(6):1613~1621.[18]Howard J W, Block R C,Dussault H, et al.A novel approach for measuring the radial distribution of charge in a heavy-ion track[J].IEEE Trans Nucl Sci, 1994,41(6): 2077~2084.。

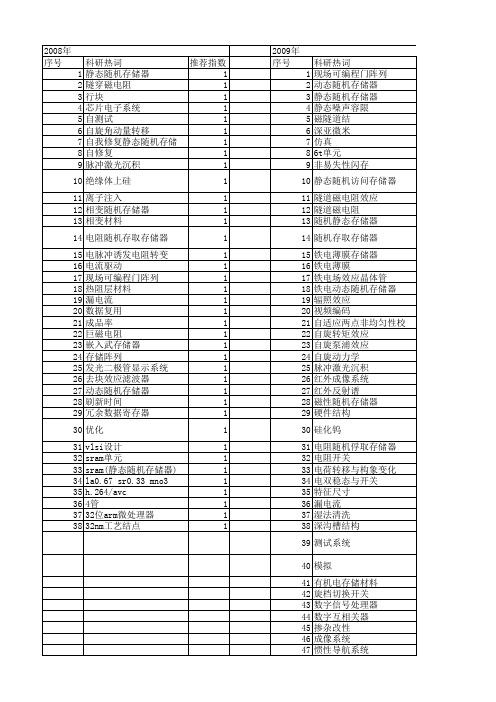

【国家自然科学基金】_随机存储器_基金支持热词逐年推荐_【万方软件创新助手】_20140802

科研热词 静态随机存储器 随机写 超大规模集成电路 质子 读写效率 芯片系统 脉冲激光沉积 脉冲宽度存储容量 翻转 缓冲层 纠错码 电磁脉冲 模幂 模乘 有效体积 数字信号处理器 故障识别标志 故障字典表 故障分辨率 故障修复率 擦除操作 控制系统电路 微机电系统 嵌入式存储器 嵌入式sram 密钥管理 密钥 存储器架构 存储器 多位翻转截面 处理器 图像识别 图像处理 固态存储器 同步读写存储器 可靠性 可信计算机平台 可信计算 单粒子翻转截面 写穿透 写合并 冗余行 内建自测试 内建自修复 内建冗余分析 光栅光调制器 tio2 sram rsa算法 pzt gan flash转换层

53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71

宏模型 失效机制 多时钟 增强型直接内存存取 可变尺寸块运动估计 反应堆 单粒子效应 全球定位系统 傅里叶变换红外光谱仪 侧壁残留 低能中子 临界电荷 串行通信 tmr效应 mram mgo la0.67sr0.33mno3 hspice al2o3

2008年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38

科研热词 推荐指数 静态随机存储器 1 隧穿磁电阻 1 行块 1 芯片电子系统 1 自测试 1 自旋角动量转移 1 自我修复静态随机存储器 1 自修复 1 脉冲激光沉积 1 绝缘体上硅 1 离子注入 1 相变随机存储器 1 相变材料 1 电阻随机存取存储器 1 电脉冲诱发电阻转变 1 电流驱动 1 现场可编程门阵列 1 热阻层材料 1 漏电流 1 数据复用 1 成品率 1 巨磁电阻 1 嵌入武存储器 1 存储阵列 1 发光二极管显示系统 1 去块效应滤波器 1 动态随机存储器 1 刷新时间 1 冗余数据寄存器 1 优化 1 vlsi设计 1 sram单元 1 sram(静态随机存储器) 1 la0.67 sr0.33 mno3 1 h.264/avc 1 4管 1 32位arm微处理器 1 32nm工艺结点 1

随机存取存储器

读/写控制电路用于对电路的工作状态进行控制。CS 称为片选信号,当CS=0时,RAM工作,CS=1时,所有 I/O端均为高阻状态,不能对RAM进行读/写操作。称为读 /写控制信号。R/W=1 时,执行读操作,将存储单元中的 信息送到I/O端上;当R/W=0时,执行写操作,加到I/O端 上的数据被写入存储单元中。

2. 动态随机存储器 动态随机存储器(DRAM) 动态RAM的存储矩阵由动态MOS存储单元组成。动态 MOS存储单元利用MOS管的栅极电容来存储信息,但由于 栅极电容的容量很小,而漏电流又不可能绝对等于0,所以 电荷保存的时间有限。为了避免存储信息的丢失,必须定 时地给电容补充漏掉的电荷。通常把这种操作称为“刷新” 或“再生”,因此DRAM内部要有刷新控制电路,其操作 也比静态RAM复杂。尽管如此,由于DRAM存储单元的结 构能做得非常简单,所用元件少,功耗低,所以目前已成 为大容量RAM的主流产品。

读出信息时也使字线为高电平,V管导通,这时CS经 V向CO充电,使位线获得读出的信息。设位线上原来的电 位UO=0,CS原来存有正电荷,电压US为高电平,因读 出 前 后 电 荷 总 量 相 等 , 因 此 有 USCS=UO(CS+CO) , 因 CO>>CS ,所以UO<<US 。例如读出前US=5V,CS/CO=1/50, 则位线上读出的电压将仅有 0.1V, 而且读出后CS上的电 压也只剩下 0.1V,这是一种破坏性读出。因此每次读出 后,要对该单元补充电荷进行刷新,同时还需要高灵敏 度读出放大器对读出信号加以放大。

随机存取存储器

9.1.2 随机存取存储器 随机存取存储器(RAM)

随机存取存储器也称随机存储器或随机读/写存储器, 简称RAM。RAM工作时可以随时从任何一个指定的地址写 入(存入)或读出(取出)信息。根据存储单元的工作原理不同, RAM分为静态RAM和动态RAM。 1. 静态随机存储器 静态随机存储器(SRAM) 1) 基本结构 SRAM主要由存储矩阵、地址译码器和读/写控制电路 三部分组成,其框图如图 9-12 所示。

静态ram的名词解释

静态ram的名词解释静态RAM(Static Random-Access Memory)是一种常用于计算机内存系统的半导体存储器。

它与动态RAM(Dynamic Random-Access Memory)相对,两者之间有着一些重要的差异。

本文将对静态RAM进行详细的名词解释,介绍其结构、工作原理、特点以及应用领域。

一、结构和工作原理静态RAM由一组存储单元组成,每个存储单元通常由一个触发器(flip-flop)构成。

存储单元可存储一个二进制位(0或1),多个存储单元则构成了一个静态RAM单元。

在每个存储单元中,触发器的状态(高电平或低电平)表示着对应二进制位的值。

静态RAM以位(bit)为基本存储单元,不同于动态RAM以字节(byte)为基本存储单元。

每个位都由一个触发器组成,通常由6个晶体管构成。

这些晶体管实现了存储、刷新和读取操作。

在静态RAM中,数据的状态可以被保持,直到被修改或重新写入。

这种保持数据的特性使得静态RAM较为快速,读取速度快,对读写访问速度的限制较小。

然而,静态RAM也需要消耗更多的电力和占用更多的空间。

二、特点1. 高速性:相对于动态RAM而言,静态RAM具有更快的存取速度。

这主要是因为静态RAM存储单元的构造较为简单,不需要刷新操作。

2. 不需要刷新:静态RAM的数据状态可以一直保持,无需定期刷新。

这在某些实时应用中尤其重要,例如高性能计算、图像处理和网络通信等。

3. 较低的功耗:由于静态RAM不需要频繁的刷新操作,相对于动态RAM而言,它对功耗的需求较低。

4. 容量限制:静态RAM存储单元所需的面积较大,因此相对来说其容量限制较为严格。

这也导致静态RAM在成本上相对较高,因此在大容量存储需求下往往采用动态RAM。

5. 稳定性:静态RAM的存储单元可以保持数据状态,因此对于需要保持长时间数据稳定性的应用是一种理想的存储解决方案。

三、应用领域静态RAM广泛应用于各种计算机系统和电子设备,包括个人电脑、服务器、网络路由器、嵌入式系统等。

存储芯片分类

存储芯片分类存储芯片是计算机系统中常见的一种主要硬件设备,用于存储和读取数据。

根据不同的工作原理和使用场景,存储芯片可以分为多种不同的类型。

下面将介绍几种比较常见的存储芯片分类。

一、随机存取存储器(RAM)随机存取存储器,即RAM(Random Access Memory),是指可以按照任意顺序访问的存储器。

RAM芯片根据存储单元的基本结构和工作方式的不同,可以分为静态RAM(SRAM)和动态RAM(DRAM)两大类。

1. 静态RAM(SRAM)静态RAM(SRAM)在存储每一位数据时,使用一个触发器来存储,因此读写速度快,且不需要刷新操作。

但是,由于每个触发器需要多个晶体管,所以芯片密度较低,成本也较高。

静态RAM主要用于高速缓存存储器等需要快速读写的应用。

2. 动态RAM(DRAM)动态RAM(DRAM)使用电容来存储每一位数据。

虽然动态RAM的存储单元比静态RAM简单,因此可以实现更高的芯片密度,但是电容容易失去电荷,需要定期进行刷新操作,因此读写速度相对较慢。

动态RAM广泛应用于主存储器等大容量存储需求较高的环境。

二、只读存储器(ROM)只读存储器,即ROM(Read-Only Memory),是指在制造过程中被烧写或者写入之后就无法再次修改的存储器。

根据ROM芯片的工作原理和可修改性,可以将ROM分为多种不同类型。

1. 掩模式只读存储器(Mask ROM)掩模式只读存储器(Mask ROM)在制造过程中被烧写了数据,一旦烧写完成后就无法再次修改。

掩模式只读存储器的成本比较低,但是需要在设计阶段提前确定需要存储的内容。

2. 可编程只读存储器(Programmable ROM)可编程只读存储器(Programmable ROM)可以在生产过程中通过特定的设备进行一次性的编程。

可编程只读存储器的成本比较低,但是编程过程不可逆。

3. 电可擦除可编程只读存储器(Electrically Erasable Programmable ROM)电可擦除可编程只读存储器(Electrically Erasable Programmable ROM,EEPROM)可以通过电压调节擦除和编程操作,可以多次擦写和编程。

计算机硬件技术基础(第2版) 习题答案 耿增民 孙思云 第3章 习题答案

第三章习题答案1.名词解释随机存储器:随机存取存储器简称RAM,也叫做读/写存储器,它能够通过指令随机地、个别地对其中各个单元进行读/写操作。

随机存储器中任何一个存储单元都能由CPU或I/O设备随机存取,且存取时间与存取单元的物理位置无关。

按照存放信息原理的不同,随机存储器又可分为静态和动态两种。

只读存储器:只读存储器是只能随机读出已经存储的信息,但不能写入新的信息的存储器。

位扩展:位扩展是指用多个存储器器件对字长进行扩充。

位数的扩展是利用芯片的并联方式来实现的,各存储芯片地址线、片选端和读写控制线并联,数据端单独引出。

全译码法:除了将低位地址总线直接连至各芯片的地址线外,余下的高位地址总线全部参加译码,译码输出作为各芯片的片选信号。

相联存储器地址映象:地址映像的功能是应用某种函数把CPU发送来的主存地址转换成Cache的地址。

地址映象方式通常采用直接映象、全相联映象、组相联映象三种方式。

Cache:高速缓冲存储器。

虚拟存储器:虚拟存储器(VirtualMemory)又称为虚拟存储系统,是以存储器访问的局部性为基础,建立在主存一辅存物理体系结构上的存储管理技术。

它是为了扩大存储容量,把辅存当作主存使用,在辅助软、硬件的控制下,将主存和辅存的地址空间统一编址,形成个庞大的存储空间。

程序运行时,用户可以访问辅存中的信息,可以使用与访问主存同样的寻址方式,所需要的程序和数据由辅助软件和硬件自动调入主存,这个扩大了的存储空间,就称为虚拟存储器。

存储器带宽:内存储器每秒钟访问二进制位的数目称为存储器带宽,用Bm表示。

它标明了一个存储器在单位时间内处理信息的能力。

存取时间存取时间又称存储器访问时间,是指启动一次存储器操作到完成该操作所需的时间。

逻辑地址:用户可以像使用内存一样利用虚拟存储器的辅存部分。

编程时,涉及辅存大小的空间范围的指令地址称为“虚地址(Virtual Address)”或“逻辑地址”。

物理地址:实际的主存储器单元地址则称为“实地址”或“物理地址(Physical Address)。

静态存储器介绍

Slide1. SRAM的全称是static random access memory,它是一种最常用的memory,核心部分是两个cross-coulped inverter 组成的bi-stable latching circuit,通常称为flip-flop的电路。

SRAM static的特性主要是它不需要像DRAM那样定期对存储的数据进行刷新,只要Vdd 不掉电,数据就可以稳定存储。

SRAM最主要的应用就是缓存,缓存的作用是在CPU和内存之间进行数据缓冲。

像智能手机这样的一些高端电子产品,SRAM是必不可少的。

SRAM 之所以可以做缓存是因为它有一个最为重要的优点:speed, SRAM的读写频率可以到几个Giga Hz,比DRAM至少快一个order。

SRAM最大的劣势在于density比较低,用的最多的SRAM是所谓的6T traditional SRAM, 1个bitcell有六个MOSFET组成,与SRAM对应的DRAM只需要一个MOSFET加一个capacitor。

bitcell占用面积大导致desity低,density低造成cost 高,具体表现是同样容量的缓存会比内存条造价高很多。

Slide 2. 这是一个目前典型的memory 架构,CPU+3级缓存再加内存条,其中一级缓存经常用8T dual port SRAM,可以用两个port同时读写,速度最高,集成度也最低,三级缓存会用high-density design的SRAM,集成度最高,速度最低。

从下面这幅实物图可以清楚看到multi-core 和三级缓存做在一起,stand alone的SRAM已经很少看到,一些低端的电子产品在介绍CPU性能参数的时候不会把缓存的信息单独列出来,但是对于像智能手机这样高端的电子产品,缓存的容量和工作频率绝对是一个重要的性能指标。

下面这张图根据价格和读写速度对memory进行一个排列,硬盘速度最低,价格最便宜,内存条其次,缓存速度最高,造价也最高。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

片. 测试和仿真数据表 明, 这 种 新 型存 储 器 相 比 常 规 8管 存 储 器 在 功 耗 的 抑 制 上 具 有 显 著 优 势 , 可 以作 为

近 阈值 非预 充 静 态 随机 存 储 器

蔡 江 铮 , 黑 勇 , 袁 甲 ,陈黎明

( 1 .q - 国科 学 院微 电子 研 究所 智 能 感 知 中心 , 北京 1 0 0 0 2 9 ; 2 . 中 国科 学 院 大 学 微 电 子 学 院 , 北京 1 0 0 0 2 9 )

Fu r t h e r mo r e ,mu l t i p l e t h r e s h o l d t e c h n o l o g y i s e mp l o y e d i n t h e c e l l ,wh i c h n o t o n l y g u a r a n t e e s t h e r e a d

Abs t r a c t : I n or de r t o s a ve t he po we r c ons um e d by t he s t a t i c r a nd o m a c c e s s m e m or y wh e n i t d e a l s wi t h

Ne a r ’ _ t h r e s ho l d n o n 。 。 pr e c ha r g e d S RAM

CAI Ji a n g z h e n g , H EI g o n g 一, YU A N J i a 一,CH EN Li mi n g ,

s t a t i c no i s e ma r gi n, bu t a l s o e nh a nc e s r e a d a bi l i t y. I n a dd i t i o n, a Sc hm i t t t r i gg e r b as e d i n ve r t e r i s a l s o

2 0 1 8年 2月

ห้องสมุดไป่ตู้

西 安 电子 科 技 大 学 学 报 ( 自然 科 学 版 )

JOU RNAL 0F XI DI AN UNI VERSI TY

Fe b . 2 0 1 8 Vo 1 . 4 5 No . 1

第4 5卷

第 1期

d o i : 1 0. 3 9 6 9 / j . i s s n . 1 0 0 1 — 2 4 0 0. 2 0 1 8 . 0 1 . 0 1 9

摘 要 :为 了降 低 静 态 随机 存 储 器 在 处 理 声 音和 视 频 数 据 时 的功 耗 , 提 出一 款 新 型 的 非 预 充 单 元 . 相 比常 规

6管 和 8管 单元 , 其 读 操 作 消 除 了预 充 机 制 , 抑 制 了无 效 的翻 转 , 因此 功 耗 得 到 显著 优 化 . 本 单元通 过多 阈 值技术 , 在 保 证 低 电压 区域 读 噪 声 容 限 的 同 时 也 加 强 了数 据 读 出 的 能 力 . 而 且 通 过 引 入 切 断 反 馈 环 的 机 制, 有 效 地 提 升 了单 元 写 能 力 . 此 外, 在 存 储 阵 列 中应用 半 斯 密特 反 相 器 , 大 幅地 提 升 了静 态 随 机 存 储 器 读

低 功 耗 应 用 的 良好 选 择 . 关 键 词 : 静 态 随机 存 储 器 ; 非预充; 声音和视频 ; 低 功 耗 中 图分 类 号 : T N4 3 文 献标 识码 : A 文章 编 号 : 1 0 0 1 — 2 4 0 0 ( 2 0 1 8 ) 0 1 — 0 1 0 6 — 0 6

v o i c e o r v i d e o d a t a ,a n o v e l me mo r y c e l l i s p r o p o s e d wh i c h e l i mi n a t e s t h e p r e c h a r g e me c h a n i s m i n t h e r e a d

( 1 . S ma r t S e n s i n g Rg a D C e n t r e , I n s t i t u t e o f Mi c r o e l e c t r o n i c s o f C h i n e s e A c a d e my o f S c i e n c e s ,B e i j i n g 1 0 0 0 2 9

o p e r a t i o n, t h u s s u p p r e s s i n g t h e i n v a l i d p o we r c o mp a r e d wi t h t h e c o n v e n t i o n a l 6 T a n d 8 T c e l 1 .

C h i n a ; 2 .S c h o o l o f Mi c r o e l e c t r o n i c s ,Un i v .o f Ch i n e s e Ac a d e my o f S c i e n c e s ,B e i j i n g 1 0 0 0 2 9 ,Ch i n a )