Altera project实验报告

verilog 实验实验一具体步骤

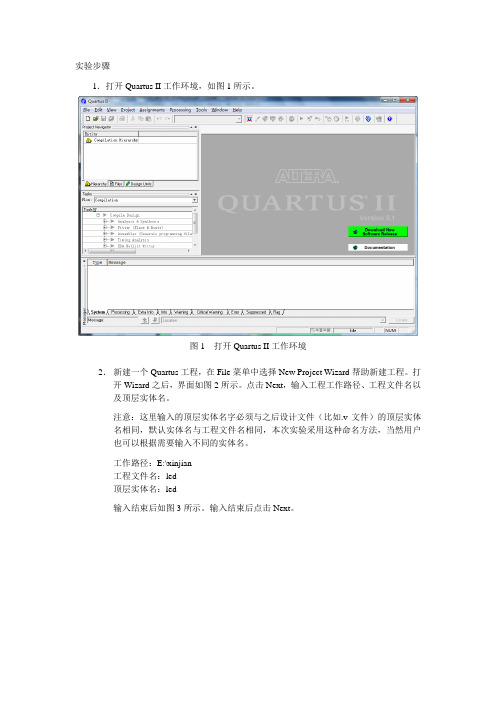

实验步骤1.打开Quartus II工作环境,如图1所示。

图1 打开Quartus II工作环境2.新建一个Quartus工程,在File菜单中选择New Project Wizard帮助新建工程。

打开Wizard之后,界面如图2所示。

点击Next,输入工程工作路径、工程文件名以及顶层实体名。

注意:这里输入的顶层实体名字必须与之后设计文件(比如.v文件)的顶层实体名相同,默认实体名与工程文件名相同,本次实验采用这种命名方法,当然用户也可以根据需要输入不同的实体名。

工作路径:E:\xinjian工程文件名:led顶层实体名:led输入结束后如图3所示。

输入结束后点击Next。

图2 New Project Wizard界面图3 输入设计工程信息3.添加设计文件,界面如图4所示。

如果用户之前已经有设计文件(比如.v文件),那么再次添加相应文件,如果没有完成的设计文件,点击Next,之后添加并且编辑设计文件。

图4 添加设计文件4.选择设计所用器件。

由于本次实验使用Altera公司提供的DE2开发板,用户必须选择与DE2开发板相对应的FPGA器件型号。

在Family菜单中选择CycloneII在Target device选项框中选择Specific device selected in ‘A vailable devices’ list 在A vailable device列表中选择EP2C35F672C6这个型号的器件。

完成后如图5所示,点击Next。

图5 选择相应器件5.设置EDA工具。

设计中可能会用到的EDA工具有综合工具、仿真工具以及时序分析工具。

在本次实验中不使用这些工具,因此点击Next直接跳过设置。

图6 设置EDA工具6.查看新建工程总结。

在基本设计完成后,Quartus II会自动生成一个总结让用户核对之前的设计(如图7所示),确认后点击Finish完成新建。

图7 新建工程总结在完成新建后,Quartus II界面中Project Navigator的Hierarchy标签栏中会出现用户正在设计的工程名以及所选用的器件型号,如图8所示。

project项目管理实验报告

project项目管理实验报告项目管理实验报告一、引言在现代社会中,项目管理已经成为各个行业中不可或缺的一部分。

项目管理的目标是通过有效地规划、组织、执行和控制项目活动,以实现项目的目标和交付成果。

本次实验旨在通过一个实际的项目案例,探讨项目管理的重要性和应用。

二、项目背景本次实验的项目是一个软件开发项目,旨在开发一款在线购物平台。

项目团队由开发人员、设计师和测试人员组成,总共有十人。

项目的目标是在三个月内完成开发,并成功上线。

三、项目规划在项目规划阶段,团队首先进行了需求分析和范围确定。

通过与客户的沟通和讨论,明确了平台的功能和特性,并制定了详细的项目计划。

项目计划包括了各个阶段的时间安排、资源分配和风险管理策略。

四、项目执行项目执行阶段是整个项目的核心,团队成员根据项目计划开始进行开发工作。

开发人员采用敏捷开发方法,将项目分为多个迭代周期,每个周期都有具体的任务和交付物。

团队成员之间进行了紧密的合作和沟通,确保任务按时完成。

五、项目控制项目控制是项目管理的重要环节,通过监控项目进展和控制项目变更,确保项目按计划进行。

团队使用了项目管理工具来追踪任务的进度和资源的使用情况。

同时,团队定期召开会议,讨论项目的问题和挑战,并制定相应的解决方案。

六、项目评估在项目完成后,团队进行了项目评估,对项目的整体表现进行了分析和总结。

评估包括了项目的成本、时间和质量等方面的考量。

通过评估,团队发现了项目中存在的问题和不足,并提出了改进的建议。

七、项目管理的意义通过本次实验,我们深刻认识到了项目管理的重要性和意义。

项目管理可以帮助团队有效地组织和协调各项工作,提高工作效率和质量。

同时,项目管理还可以帮助团队应对项目中的风险和挑战,确保项目的顺利进行。

八、结论通过本次实验,我们不仅学习了项目管理的理论知识,还亲身体验了项目管理的实践过程。

项目管理不仅仅是一种工具和方法,更是一种思维方式和管理能力。

只有通过不断的实践和反思,我们才能不断提升自己的项目管理能力,更好地应对各种挑战和问题。

熟悉Altera Quarstus II 开发环境

昆明理工大学信息工程与自动化学院学生实验报告(2011 —2012 学年第 2 学期)课程名称: FPGA 开课实验室:信自楼xxx 2012年 03 月 04日年级、专业、班计科xxx 学号Xxxxxxxxx 姓名Xxx 成绩实验项目名称熟悉Altera Quarstus II 开发环境指导教师Xxxx 教师评语教师签名:年月日注:报告内容按实验须知中七点要求进行。

一、实验目的●熟悉QuartusII软件的操作环境。

●熟悉QuartusII软件开发FPGA的基本操作流程。

●可独立使用使用QuartusII软件开发新工程。

二、实验原理Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL 以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。

具有运行速度快,界面统一,功能集中,易学易用等特点。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

对第三方EDA 工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统(SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台。

三、实验内容本次实验通过给定的工程实例“38译码器”来熟悉Altera QuartusII软件的基本操作、设计、编译以及仿真流程。

实验二+Qutartus+II+入门实验

实验二Quartus II使用入门姓名:学号:班级:日期:一、实验目的和要求1、了解Altera 公司EDA软件Qutartus II的基本设计流程2、通过对DE1的操作,初步掌握设计项目的建立,编译,适配过程3、初步认识Verilog硬件描述语言二、实验环境1、PC机,Pentium 4 2.0G以上,内存1G以上,硬盘500G以上,1024×768彩显,USB接口,网络接口,串口。

2、友晶DE1开发板和相关配件。

3、软件:Windows XP或者Windows 7操作系统,DE1配套光盘。

三、实验内容1、通过最简单工程项目了解Quartus II基本设计过程。

2、DE1开光和发光管的对应显示控制,即拨动开关,对应的LED亮或灭。

3、了解Modelsim仿真工具和Quartus II的逻辑仿真及时序仿真。

四、实验步骤1、建立Quartus 工程:1)打开Quartus II 工作环境。

2)点击菜单项File->New Project Wizard 帮助新建工程。

3)输入工程工作路径、工程文件名以及顶层实体名。

自己起名字,例如学号等。

注意:输入的顶层实体名必须与之后设计文件的顶层实体名相同,默认的顶层实体名与工程文件名相同,本类实验均采用这种命名方法以便于管理。

4)添加设计文件。

如果用户之前已经有设计文件(比如.v 文件)。

那么直接添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑新的设计文件。

5)选择设计所用器件。

由于本次实验使用 Altera 公司提供的DE1 开发板,用户必须选择与之相对应的FPGA 器件型号,如下图:6)设置 EDA 工具。

设计中可能会用到的EDA 工具有综合工具、仿真工具以及时序分析工具。

本次实验中不使用这些工具,因此点击Next 直接跳过设置。

7)查看新建工程总结。

在基本设计完成后,Quartus II 会自动生成一个总结让用户核对之前的设计,确认后点击Finish 完成新建。

用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

用ModelSimSE进行 功能仿真和时序仿真的方法 (ALTERA篇)黄俊April 2007用ModelSim SE进行功能仿真和时序仿真的方法 (ALTERA篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1界面的。

我个人认为,如果是开发StratixII或CycloneII或MAXII,用QuartusII6.0+SP1+SP2比较稳定。

(2) ModelSim SE. ALTERA仿真库要已经装好,安装仿真库的笔记已记录于《在ModelSimSE中添加ALTERA仿真库的详细步骤》中。

我电脑上装的是ModelSim SE6.1b。

例子程序的制作先在Quartus II里生成一个例子程序,以方便介绍三种仿真的方法。

步骤如下:1、新建一个工程(Project),工程名取lpm_shift, 器件选CycloneII EP2C5Q208C, 第三方的工具暂时都不选。

2、菜单栏上ToolsÆMegaWizard Plug-In Manager, 点Next,在storage中选LPM_SHIFTREG,输出文件格式根据习惯选一种语言,在这里以Verilog的为例,在右边的output file名字中加上lpm_shift。

点Next。

3、这个例子是做一个移位寄存器,调用lpm库,和cycloneII元件库,也正好可以作为对前面建好的ALTERA库的一个验证。

点可以查到该模块的使用说明和详细介绍。

移位寄存器比较简单,就不用细看了。

如下图设置.点Next.4、加上一个异步清零端,点Next,再点Next,最后点Finish.Add/Remove Files in Project…,6、点图标,选中生成的lpm_shift,点打开再点Add都加到项目中去。

7、在这里直接把lpm_shift.v当成顶层文件,就不需要再例化它了。

8、下面写一个简单的TestBench.a)Quartus II工具栏上点图标,选Verilog HDL;b)点,设文件名为top_tb;c)如下所述写一个简单的TestBench.(例子见附件)开始仿真z ModelSim仿真有很多种流程,下面我采用个人感觉比较好一个流程进行仿真验证:基于工程(Project)的流程Step1 新建一个工程Step2 添加文件到工程中去Step3 编译设计文件Step4 启动仿真器,指定顶层设计单元Step5 查看和调试结果z对的设计有三个阶段的仿真。

project项目管理实验报告.doc

project项目管理实验报告项目管理可交付物项目管理软件project项目管理案例microsoftproject 篇一:project计算机项目管理实验报告计算机辅助项目管理课程报告班级:学号:姓名:指导教师:完成日期:目录一、项目基本信息1、项目简介2、项目任务关系、固定成本及资源需求量3、可用资源4.、项目管理要求二、项目初始计划1、定义项目2、定义常规工作时间3、列出项目中任务4、初始计划的内容5、初始计划的分析三、基准计划1、分配资源2、删除(替换)资源3、资源的调整4、基准计划调整5、监控6、第一轮监控7、第二轮监控8、第三轮监控9、第四轮监控10、第五轮监控四、竣工验收1、竣工验收的程序五、心得体会摘要:目前工程建设项目规模逐渐增大,渐趋复杂,业主要求采用计算机进行项目管理。

各单位市场竞争的需要、项目管理人才自身发展的需要、导致应用计算机进行项目管理的客观条件已基本成熟。

如何有效管理这些冗杂的项目信息?如何对收集的大量信息进行加工?如何将加工后的信息及时分享给组织中的每个成员?这些问题都可以用project软件解决!项目Microsoft Project 不仅可以快速、准确地创建项目计划,而且可以帮助项目经理实现项目进度、成本的控制、分析和预测,使项目工期大大缩短,资源得到有效利用,提高经济效益!本文仅以一个案例来说明该软件的部分功能!关键词:资源分配;调整;监控;一、项目基本信息1、项目简介项目的主要工作是维修某主要道路下一段长约1公里的供水管道,市政局要求电力部门配合施工,同时铺设一条地下电缆,以增加该道路两侧的用电用户。

由于该项目是在现有道路上开挖,故市政局决定在回填后顺便铺设新的混凝土路面。

为此,专门成立了一个项目管理办公室,以管理、协调该项目。

项目内容包括:供水工程、电力工程和道路工程。

整个项目从2011年7月1日提交预算报批为开始,市政局希望将项目施工对公众造成的影响降至最低,故希望该项目能在2011年10月底竣工并恢复交通。

《FPGA系统设计》实验报告》QuartusII软件入门并设计1位半加器

《FPGA系统设计》实验报告》QuartusII软件入门并设计1位半加器

一、设计任务

1、熟悉ALTERA公司EDA设计工具软件QuartusII。

2、熟悉EDA实验箱。

3、学习QuartusII软件。

4、在QuartusII软件中使用原理图输入法设计并实现一个1位半加器。

二、设计过程

1、半加器的设计:电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。

是实现两个一位二进制数的加法运算电路。

2、半加器表达式:进位:co=a and b

和:so=a xnor (not b)

3、半加器原理图、如下:

图1.1 半加器原理图

1.行为描述程序

2.数据流描述程序

3.结构体描述程序

图1.2 半加器实验操作图4、真值表

表1.1 半加器真值表

5、引脚分配图

图1.3 引脚分配图

6、调试过程

将99脚和98脚接到拨码开关,87脚和86脚接发光二极管,当开关全拨至1或全拨至0不亮,反之会亮。

三、总结

通过这次实验,我学会了用VHDL语言实现半加器功能,掌握Quartus‖软件输入设计流程,本次实验我分别用实验箱上的开关K1、K2作为半加器两输入A、B;分别用LED灯LED1、LED2作为半加器的两个输出端S、C。

实验时将实验箱的拨动开关拨向下时为低电平“0”。

拨向上时为高电平“1”,LED高电平时灯亮,低电平时灯灭。

其结果均符合半加器的真值表。

PROJECT软件应用实验报告

2017-2018学年第二学期《Project软件应用》课程实验报告班级: 12011501学号: 2015302850姓名:张盼盼2018年6月目录一、项目目标 (2)二、项目初始创建计划 (2)三、基准计划 (4)(1) 资源调配分析 (6)(2) 资源调配结果 (7)四、跟踪调整计划 (7)1.8月底的进度监控 (7)(1)跟踪项目日程 (8)(2)跟踪项目成本 (8)(3)跟踪项目工时 (8)(4)调整方法和结果 (9)2.9月份进度监控 (9)(1)项目跟踪结果 (9)3.10月底的监控 (10)(1)项目跟踪结果 (10)4.11月底的监控 (10)五、项目实施心得体会 (11)1. 学习中的重点与困难 (11)2. 反思和感悟 (11)一、项目目标项目范围:维修某主要道路下一段长约1公里的供水管道进度目标:2018年8月1日开始,2018年11月底通过学习和运用MS Project 软件,进行项目规划、项目监控和项目调整,使得该维修供水管道项目在项目计划时间内完成,即2018年11月底完成,并控制项目成本在项目成本预算以下。

二、项目初始创建计划1.打开 MS Project 软件,由文件-新建,并保存。

2.打开文件-选项-日程,调整工作周和工作日,设置项目开始日程,为2018年8月1日;设置项目日程(包括工期和工时的显示单位,资源单位等)。

3.创建一个新的日历。

由〔项目〕菜单选取〔更改工作时间〕。

选择新建日历,改新建日历的名称;“标准”的副本(项目日历)。

由于在项目执行期间有节假日(中秋节与国庆节),在日历下方选择添加例外日期,设置开始和完成时间如图所示,并保存。

然后运用新的日历。

由〔项目〕菜单选取〔项目信息〕。

4.建立资源列表,根据项目数据可知,技工与壮工(非技工的)按工时一天8小时来计算,则技工标准费率=50(元/日)/8(小时)=6.25元/小时,壮工则为3.75元/日。

管理费标准费率也同样计算为6.25元/小时。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ALTERA Project实验报告

选题:打砖块

第二组:张渝缘,李任,李烨

一、实验目的:

1、通过实验能独立的运行文件达到效果。

2、深入了解软硬结合的功能,学会独立的解决问题。

二、实验器材:

1、ALTERA DE2板子一个

2、台式显示器一个

3、PC机一台

三、实验步骤:

1、硬件部分的编译:

(1)打开所给的lab3文件,文件中自给的代码如图:

代码分析:

对时钟信号的定义:

控制砖块左右移动的按键:

起止条件的判断:

(2)单击NEW中选择Block Diagram/Schematic File得到:

(3)打开TOOLS-Sopc Builder,对软核进行编译。

选择Processors-Nios II Processor,打开界面:

选择确定:

双击Project项中的de2_sram_controller,对静态随机存储器进行编译。

选择确定,将其重命名为sram。

选择Interface Protocols-Serial-JTAG UART,对JTAG UART进行编译:

选择Memories and Memory Controllers-External Memory Interfaces-SDRAM interfaces-SDRAM Controller并将参数按图中设置:

并将其重命名为sdram。

编译显示器与DE板间的传输器VGA,在Project中选择DE2 _vga _raster,并进行编译。

最后选择Project中的rotary_controller,重命名为rotary:

再对CPU进行设置:

最后整理得到软核如图:

单击确定按钮,进行编译。

编译完成后,双击我们建立的BDF文件,选择建立好的PTF文件。

得到所编译好的图,再右键选择GENERATE PINS FOR SYMBOL PORTS。

可以得到器件连接的原理图。

再导入所给的TCL文件,完

成对引脚的分配,则此时软核的编译已经完成。

若想要检查自己引脚分配是否有问题,则点击pin-planner。

可以看到引脚分配上没有错误,下面运行已编译好的程序。

耐性等待一段时间后发现编译并没有错误。

那么硬件部分的编译已经完成,说明没有问题。

2、软件部分的编译:

打开NIOS SOFTWARE文件,选择NEW-NIOS II APPLICATION and BSP from Template。

按如图结果对其进行设置,设置好后进行运

行完成。

可以看到出现了两个文件夹,这就是我们软件的编译环境。

下面添加一个源文件,右键选择NEW-SOURCE FILE,建立一个main.c 的主文件,点击FINISH,完成建立。

在源文件里面将已给源代码考入进去完成建立。

原文件建立好后,点击保存建立好的main函数,如果不保存将导致文件BUILD错误。

下面对文件进行编译右键选择BUILD PROJECT,

等待一段时间后发现文件建立完成。

则现在软件部分也编译完成。

3、连接DE2板子并进行调试。

将画面切回到刚才的QUARTUS中,连接好DE2板,将硬件考入到板子中去。

点击START将硬件考入到了CE2板中。

可以看到板子和显示器上的结果如图:

显示器上

再运行NIOS II,右键选择RUN AS-NIOS II HARDW ARE,这运行了软

件,观察实验结果。

四、实验小结

本次实验是ALTERA的最后一次实验,其目的是将以前所学的综合起来让我们去运行,通过此次学习,我们理解了ALTERA的具体的运行方式,明白了如何去完整的实验软硬件的结合,并且基本掌握了ALTERA的使用方法。

五、任务分配

张渝缘:负责硬件的编写和报告的书写。

李任:负责软件的编写。

李烨:负责整体的运行和调试。