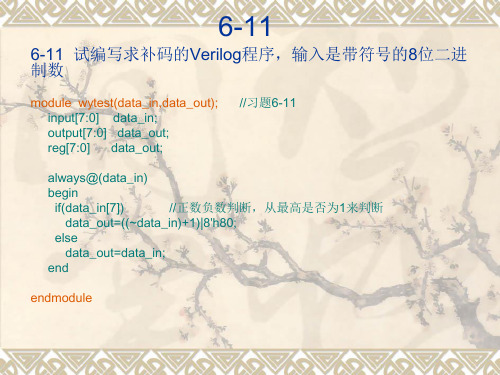

第6章_Verilog_HDL设计进阶习题

EDA技术与Verilog设计第六章课后习题部分答案

6-15

6-16

设计一个74161的电路。

6-16

注意:异步清零、同步置位

CO= Q3 Q2 Q1 Q0 CTT

6-16

module wytest(reset,load,ctt,ctp,clk,data_in,out,co);//习题6-16 input reset,load,ctt,ctp,clk; input[3:0] data_in; output[3:0] out; output co; reg[3:0] out; reg co; always@(posedge clk or negedge reset) if(!reset) begin out<=4'b0; co<=1'b0; end else if(!load) out<=data_in; else if(!ctt) out<=out; else if(!ctp) out<=out;

always@(posedge clk) begin firsta[3:0]<=a[7:4]; seconda[3:0]<=a[3:0]; firstb[3:0]<=b[7:4]; secondb[3:0]<=b[3:0]; end

mul4x4 m1(outa, firsta,firstb,clk), m2(outb, seconda,firstb,clk), m3(outc, firsta,secondb,clk), m4(outd,seconda,secondb,clk);

6-13

6-14

试编写一个实现3输入与非门的verilog程序;

module

wytest(a,o); a;

VerilogHDL设计进阶专题知识讲座

6.8 Verilog HDL旳RTL表述

6.8.2 数据流描述

6.8.3 构造描述

习题

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同措施,它们是什么,怎 样实现? 6-2 哪一种复位措施必须将复位信号放在敏感信号表中?给出这两种电路旳Verilog 描述。 6-3 用不同循环语句分别设计一种逻辑电路模块,用以统计一8位二进制数中含1旳 数量。 6-4 用循环语句设计一种7人投票表决器。 6-5 设计一种4位4输入最大数值检测电路。 6-6 从不完整旳条件语句产生时序模块旳原理看,例6-9和例6-10从表面上看都包括 不完整条件语句,试阐明,为何例6-9旳综合成果含锁存器,二例6-10却没有。 6-7 设计一种求补码旳程序,输入数据是一种有符号旳8位二进制数。 6-8 设计一种比较电路,当输入旳8421BCD码不小于5时输出1,不然输出0。 6-9 用原理图或Verilog输入方式分别设计一种周期性产生二进制序列01001011001 旳序列发生器,用移位寄存器或用同步时序电路实现,并用时序仿真器验证其功能。 6-10 基于原理图输入方式,用74194、74273、D触发器等器件构成8位串入并出旳 转换电路,要求在转换过程中数据不变,只有当8位一组数据全部转换结束后,输 出才变化一次。

试验与设计

6-3 VGA彩条信号显示控制电路设计

(1)试验目旳: (2)试验原理:

试验与设计

6-3 VGA彩条信号显示控制电路设计

(1)试验目旳:GA彩条信号显示控制电路设计

(1)试验目旳: (2)试验原理:

试验与设计

6-3 VGA彩条信号显示控制电路设计

第6章 Verilog HDL设计进阶

6.1 过程构造中旳赋值语句

第6章 Verilog HDL设计进阶习题

1CLK7476N 1K ~1Q ~1CLR 14

U3A 7400N

3

V1 100 Hz 5V J1

10 9 2 7 6 5 4 3

74194N

9 QD QC QB QA 12 13 14 15 11 13 14 15 16 17 18 19 20 21 22 23 1 2 3 4 5 6 7 8 G D C B A

//Verilog设计一个4位4输入最大数值检测电路 module Maximum_value_detection(Mostlarge,a,b,c,d);//4位 4输入最大数值检测电路 output [3:0] Mostlarge; input [3:0] a,b,c,d; wire[3:0]sum1,sum2,sum3;

习

CP 1 2 3 4 5 6 QD(A2) QC(D4、~D5) 0 0 0 1 1 1 1 1 1 0 ~0 0 QB(A1) 0 1 1 0 0 1

题

QA(A0、D7) 1 0 1 0 1 0 D D1 D2 D3 D4 D5 D6 F 0 1 0 0 1 0

7

8 9 10 11

1

1 1 1 1

U1

74150N

Key = Space

XSC1

Ext Trig + _ A + _ + B _

U5A 7404N

E15 E14 E13 E12 E11 E10 E9 E8 E7 E6 E5 E4 E3 E2 E1 E0

0

1 ~1 1 1

1

0 0 1 1

1

0 1 0 1

D7

D4 D5 D6 D7

1

1 0 0 1

VDD 5V U2 U1A 74S04D

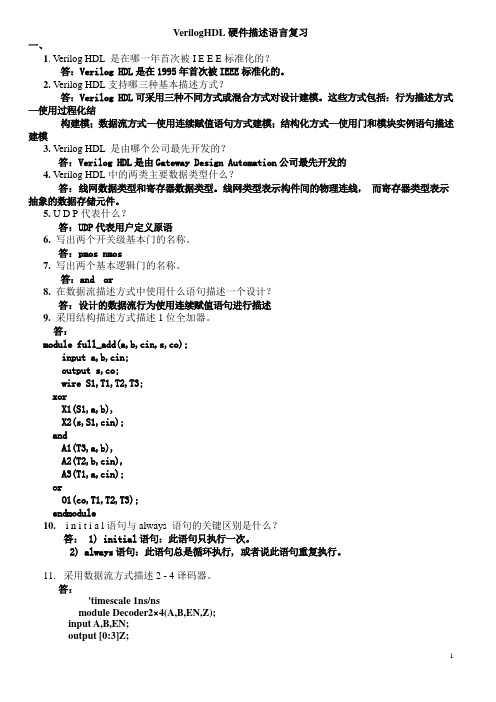

VerilogHDL复习题与答案

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的?答:Verilog HDL是在1995年首次被IEEE标准化的。

2. Verilog HDL支持哪三种基本描述方式?答:Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的?答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么?答:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

5. U D P代表什么?答:UDP代表用户定义原语6. 写出两个开关级基本门的名称。

答:pmos nmos7.写出两个基本逻辑门的名称。

答:and or8.在数据流描述方式中使用什么语句描述一个设计?答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器。

答:module full_add(a,b,cin,s,co);input a,b,cin;output s,co;wire S1,T1,T2,T3;xorX1(S1,a,b),X2(s,S1,cin);andA1(T3,a,b),A2(T2,b,cin),A3(T1,a,cin);orO1(co,T1,T2,T3);endmodule10. i n i t i a l语句与always 语句的关键区别是什么?答: 1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行, 或者说此语句重复执行。

11.采用数据流方式描述2 - 4译码器。

答:'timescale 1ns/nsmodule Decoder2×4(A,B,EN,Z);input A,B,EN;output [0:3]Z;wire abar,Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z[0]=~(Abar&Bbar&EN);assign #2 Z[1]=~(Abar&B&EN);assign #2 Z[2]=~(A&Bbar&EN);assign #2 Z[3]=~(A&B&EN);endmodule1 2. 找出下面连续赋值语句的错误。

第6章_Verilog_HDL设计进阶习题

0

习

题

6-9 用原理图或Verilog输入方式分别设计一个周期性产生二进制序列01001011001 的序列发生器,用移位寄存器或用同步时序电路实现,并用时序仿真器验证其功能。

习

CP 1 2 3 4 5 6 QD(A2) QC(D4、~D5) 0 0 0 1 1 1 1 1 1 0 ~0 0 QB(A1) 0 1 1 0 0 1

题

QA(A0、D7) 1 0 1 0 D D1 D2 D3 D4 F 0 1 0 0 1 0

6-9 用原理图或Verilog输入方式分别设计一个周期性产生二进制序列01001011001 的序列发生器,用移位寄存器或用同步时序电路实现,并用时序仿真器验证其功能。

6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的 数量。

6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制 数中含1的数量。

while循环语句

module Statistics8(sum,A); parameter S=8; output[3:0]sum; input[7:0] A; reg[S:1] AT; reg[3:0] sum; reg[S:0] CT; always @(A) begin AT={{S{1'b0}},A}; sum=0; CT=S; while(CT>0) begin if(AT[1])sum=sum+1;else sum=sum; begin CT= CT-1; AT=AT>>1; end end end endmodule

事实上,例6-9中,T在过程中出现了3次非阻塞赋值操作,即有3个赋值源对 同一信号T进行赋值--T<=0、T<=T+1和T<=T+2。但根据以上的讨论,对于非阻塞 式赋值,前两个语句中的赋值目标信号T都不可能得到任何数值,只有最后的 T<=T+2语句中的T的值能得到更新。然而,由于赋值符号右边的T始终未得到任何 确定的初始值,即语句T<=0并未完成赋值,所以最后的T始终是个未知值。结果 只能被综合成随S1和S0随机变动的时序电路,导致T成为一个不确定的信号。结 果在过程最后的case语句中,无法通过判断T的值来确定选通输入,即对OUT的赋 值。 例6-10就不一样了。程序首先执行了阻塞式赋值语句T=0,T即刻被更新,从 而使两个if语句中的T都能得到确定的初值。另一方面,当if语句不满足条件时, 即当S0或S1不等于1时,由于T已经在第一条赋值语句中被更新为确定的值0了, 所以尽管两个if语句从表面上看都属于不完整的条件语句,也不可能被综合成时 序电路了。显然也就有了图6-4所示正确的波形输出。

数字系统设计与verilog HDL 第6章

4.关系运算符(Relational operators) < 小于 <= 小于或等于 > 大于 >= 大于或等于

5.等式运算符(Equality Operators) == 等于 != 不等于 === 全等 !== 不全等

例:对于A=2'b1x和 B=2'b1x,则 A==B结果为x, A===B结果为1

关键字(Keywords)

Verilog语言内部已经使用的词称为关键字或

保留字,这些保留字用户不能作为变量或节点

名字使用。

关键字都是小写的。

6.2 常量

程序运行中,值不能被改变的量称为 常量(constants),Verilog中的常量主 要有如下3种类型:

◆ 整数 ◆ 实数

◆ 字符串

整数(integer)

字符串(Strings)

字符串是双引号内的字符序列。 字符串不能分成多行书写。例如:

"INTERNAL ERROR"

字符串的作用主要是用于仿真时,显示一些 相关的信息,或者指定显示的格式。

6.3 数据类型

数据类型(Data Type)是用来表示数字电路中的 物理连线、数据存储和传输单元等物理量的。

空白符和注释

空白符(White space) 空白符包括:空格、tab、换行和换页。空白符使 代码错落有致,阅读起来更方便。在综合时空白符 被忽略。 注释(Comment) ◆ 单行注释:以“//”开始到本行结束,不允许续 行 ◆ 多行注释:多行注释以“/*”开始,到“*/”结 束

标识符(Identifiers)

第6章 Verilog HDL语法与要素

主要内容

VerilogHDL复习题与答案

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的?答:Verilog HDL是在1995年首次被IEEE标准化的。

2. Verilog HDL支持哪三种基本描述方式?答:Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的?答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么?答:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

5. U D P代表什么?答:UDP代表用户定义原语6. 写出两个开关级基本门的名称。

答:pmos nmos7.写出两个基本逻辑门的名称。

答:and or8.在数据流描述方式中使用什么语句描述一个设计?答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器。

答:module full_add(a,b,cin,s,co);input a,b,cin;output s,co;wire S1,T1,T2,T3;xorX1(S1,a,b),X2(s,S1,cin);andA1(T3,a,b),A2(T2,b,cin),A3(T1,a,cin);orO1(co,T1,T2,T3);endmodule10. i n i t i a l语句与always 语句的关键区别是什么?答: 1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行, 或者说此语句重复执行。

11.采用数据流方式描述2 - 4译码器。

答:'timescale 1ns/nsmodule Decoder2×4(A,B,EN,Z);input A,B,EN;output [0:3]Z;wire abar,Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z[0]=~(Abar&Bbar&EN);assign #2 Z[1]=~(Abar&B&EN);assign #2 Z[2]=~(A&Bbar&EN);assign #2 Z[3]=~(A&B&EN);endmodule1 2. 找出下面连续赋值语句的错误。

数字集成电路设计入门(从HDL到版图)6-9

第六章Verilog的数据类型及逻辑系统学习内容:•学习Verilog逻辑值系统•学习Verilog中不同类的数据类型•理解每种数据类型的用途及用法•数据类型说明的语法Verilog采用的四值逻辑系统’0’, Low, False, Logic Low, Ground,VSS,Negative Assertion‘1’, High, True, Logic High, Power,VDD, VCC, Positive Assertion’X’ Unknown: Occurs at Logical Which Cannotbe Resolved ConflictHiZ, High Impedance, Tri-Stated,Disabled Driver (Unknown)主要数据类型Verilog主要有三类(class)数据类型:•net (线网): 表示器件之间的物理连接•register (寄存器):表示抽象存储元件•parameters(参数) : 运行时的常数(run-time constants)net(线网)net需要被持续的驱动,驱动它的可以是门和模块。

当net驱动器的值发生变化时,Verilog自动的将新值传送到net上。

在例子中,线网out由or门驱动。

当or门的输入信号置位时将传输到线网net上。

•有多种net 类型用于设计(design-specific)建模和工艺(technology-specific)建模•没有声明的net 的缺省类型为1 位(标量)wire 类型。

但这个缺省类型可由下面的编译指导改变:`default_nettype <nettype>net 类型功能wire, trisupply1, supply0wor, triorwand, triandtriregtri1, tri0标准内部连接线(缺省)电源和地多驱动源线或多驱动源线与能保存电荷的net 无驱动时上拉/下拉综合编译器不支持的net 类型•wire类型是最常用的类型,只有连接功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TQ=TQ>>1; end

end

endmodule

6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制

数中含1的数量。

while循环语句

module Statistics8(sum,A); parameter S=8; output[3:0]sum; input[7:0] A; reg[S:1] AT; reg[3:0] sum; reg[S:0] CT; always @(A) begin AT={{S{1'b0}},A}; sum=0; CT=S;

output OUT ;

output OUT ;

input D0,D1, D2,D3,S1, SO;

input DO,D1, D2,D3,S1, SO;

reg [2:0] T ; reg OUT;

reg [2:0] T ; reg OUT;

always @(D0, D1,D2,D3, S1,S0)

always @(D0, D1,D2,D3, S1,S0)

//Verilog设计一个4位4输入最大数值检测电路 module cnt55(max,a,b,c,d);//4位4输入最大数值检测电路 output [3:0] max; input [3:0] a,b,c,d; wire[3:0]sum1,sum2,sum3; assign sum1=(a>b)?a:b; assign sum2=(c>d)?c:d; assign max=(sum1>sum2)?sum1:sum2; endmodule

答:参见书P137

事实上,例6-9中,T在过程中出现了3次非阻塞赋值操作,即有3个赋值源对 同一信号T进行赋值--T<=0、T<=T+1和T<=T+2。但根据以上的讨论,对于非阻塞 式赋值,前两个语句中的赋值目标信号T都不可能得到任何数值,只有最后的 T<=T+2语句中的T的值能得到更新。然而,由于赋值符号右边的T始终未得到任何 确定的初始值,即语句T<=0并未完成赋值,所以最后的T始终是个未知值。结果 只能被综合成随S1和S0随机变动的时序电路,导致T成为一个不确定的信号。结 果在过程最后的case语句中,无法通过判断T的值来确定选通输入,即对OUT的赋 值。

begin sum=0;

for(i=0;i<=6;i=i+1) //for 语句 if(t[i]) sum=sum+1;

if(sum[2]) f=1; //若超过4 人赞成,则pass=1 else f=0; end endmodule

习题

6-5 Verilog设计一个4位4输入最大数值检测电路。

描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:

always @(posedge CLK) //CLK上升沿启动

Q<=D;

//当CLK有升沿时D被锁入Q

异步清零:

always @(posedge CLK or negedge RST) begin //块开始

if(!RST)Q<=0; //如果RST=0条件成立,Q被清0

else if(EN) Q<=D;

//在CLK上升沿处,EN=1,则执行赋值语句

end

//块结束

习题

6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的

数量。

for循环语句

repeat循环语句

module cnt53(a,Q);

module cnt53(a,Q); output[3:0]a; input[7:0] Q; reg[3:0] a; integer i; always @(Q)

1 : OUT= D1;

2 : OUT = D2 ;

2 : OUT =D2 ;

3 : OUT= D3;

3 : OUT= D3;

default : OUT D0;

default : OUT D0;

endcase end

endcase end

endmodule

endmodule

习题

6-6 从不完整的条件语句产生时序模块的原理看,例6-9和例6-10从表面上看都包含 不完整条件语句,试说明,为什么例6-9的综合结果含锁存器,二例6-10却没有。

begin T <= 0;

begin T = 0;

if (SO==1) T <= T+1

if (SO==1) T = T+1

if (S1==1) T <= T+2 ;

if (S1==1) T = T+2 ;

Hale Waihona Puke case (T)case (T)

0 : OUT = D0;

0 : OUT = D0;

1 : OUT = D1;

while(CT>0) begin

if(AT[1])sum=sum+1;else sum=sum; begin CT= CT-1; AT=AT>>1; end end end endmodule

习题

6-4 用循环语句设计一个7人投票表决器。

module cnt54(f,t); output f; input[6:0] t; reg[2:0] sum; integer i; reg f; always @(t)

begin a=0;

for(i=0;i<=7;i=i+1) //for 语句 if(Q[i]) a=a+1; else a=a;

end endmodule

parameter S=4; output[3:0]a; input[7:0] Q; reg[3:0] a; reg[2*S:1]TQ; integer i; always @(Q) begin TQ=Q; sum=0;

第6章

Verilog HDL设计进阶

习题 实验与设计

习题

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如 何实现? 答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明 正向跳变,或negedge用于指明负向跳变实现

6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog

习题

6-6 从不完整的条件语句产生时序模块的原理看,例6-9和例6-10从表面上看都包含 不完整条件语句,试说明,为什么例6-9的综合结果含锁存器,二例6-10却没有。

答:参见书P137

【例6-9】非阻塞赋初值导致错误

【例6-10】阻塞赋初值正确

module mux4_1(D0,D1,D2,D3,S1,S0,OUT); module mux4_1(DO,D1, D2,D3,S1, SO, OUT);