封装基本流程简介

封装工艺流程简介 (3)

设备:

封装工艺流程简介

Tape and reel 编带

设备:

描述:

使用卷带包装设备,将单 颗产品用编带材料(卷带+盖 带)进行打卷包装。

封装工艺流程简介

Packing 包装

描述:

通过捆绑/包装以确 保产品在操作,运输的过 程中不受湿气, ESD的侵 袭,同时也确保产品在运 输过程中不受损伤。

封装工艺流程简介

2016-Jan-1

封装工艺流程简介

FOL

IQA SMT Pre-bake

基板收取Βιβλιοθήκη 来料检验IQA表面贴装* 可选 基板烘烤

Taping BG W/M

De-tape

D/S

2/O Fail

QA Pass

DA

DAC

Plasma

圆片收取 来料检验 贴保护膜 背部研磨 圆片装载 去掉保护膜

芯片切割 第二次光学检查

封装工艺流程简介

Baking 烘烤

描述:

PCB需要在做DA之 前做一下烘烤,以去 除PCB中的水分,提高 产品的可靠性能。

设备:

N2以防止PCB氧化

N2 inlet

Carrier Carrier

Outlet

125oC

封装工艺流程简介

Die Attach 装片

描述:

利用银浆或Film的 粘性将切割好的好的 晶粒吸取并粘贴于基 板上,以便于后制程作 业。

等离子清洗示意图

封装工艺流程简介

MD 包封

描述:

将前道完成后的产品 ,使用塑封料把芯片 塑封起来,免受外力损 坏。同时加强器件的 物理特性便于使用。

设备:

封装工艺流程简介

PMC 包封后烘

第二章-电子封装的基本工艺-PDF全

点面积大,无方向性,可自动化焊接。

三种引线键合的焊接拉力比较

热压焊:<0.05N/点 超声焊:>0.1N/点(Al丝, 40µm) 热超声焊:0.07-0.09N/点(Au丝, 25µm)

引线键合可能产生的失效

脱焊(lift-off):原因是焊盘上存在有机沾污或是 表面氧化层太厚 疲劳断裂(fatigue break):原因是生成金属间化 合物,使接触电阻增大。金属间化合物形成的同 时,在焊接点产生空洞,在热冲击、温度循环过 程中,空洞越来越大,导致焊点断裂。 (金属间化合物的生成是二种金属键合的关键, 金属间化合物的剪切强度比纯金和纯铝高。)

TAB的应用

主要应用在低成本,大规模生产的电子产品。

TAB的引线在九十年代: 200—300根,内引线间距50—80um,外引线

间距<0.3mm 2000年:达到800—1000根引线

2.2.3 倒装焊

倒装焊(FCB)是芯片面朝下,芯片焊区直接与基板 焊区直接互连的一种方法。

优点: • 互连线短,互连电容、电阻、电感小,适合高频高速器件; • 占基板的面积小,安装密度高; • 芯片焊区可面分布,适合高I/O器件; • 芯片安装和互连可以同时进行,工艺简单、快速,适合

1.热压焊:

利用加热和加压力使金属丝与Al或Au金属焊区压焊在一 起。 原理:使焊区金属塑性形变,破坏压焊界面氧化层,使金属 丝和焊区金属接触面产生原子间吸引力,达到键合的目的。 此外,界面上、下金属在加热加压下相互镶嵌。 焊接压力:0.5-1.5N/点 焊头温度:150℃ 芯片温度:>200℃ 缺点:高温:氧化,生成金属间化合物;

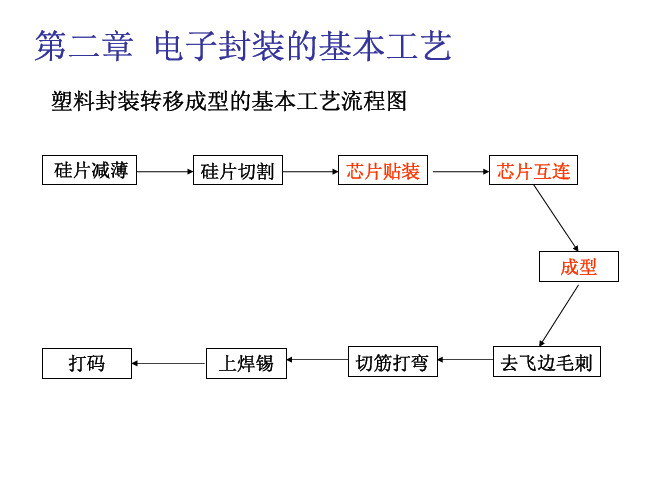

第二章 电子封装的基本工艺

PBGA封装制程简介

NITTO M-286N

A020 WAFER MOUNT

首頁

簡述 PBGA封裝製程 PBGA前段流程 PBGA後段流程

簡報地圖

A020 WAFER MOUNT簡介

W WAFER MOUNT

首頁

簡述 PBGA封裝製程 PBGA前段流程 PBGAAW

首頁

簡述 PBGA封裝製程 PBGA前段流程 PBGA後段流程

簡報地圖

W

A030 WAFER SAW

首頁

簡述 PBGA封裝製程 PBGA前段流程 PBGA後段流程

簡報地圖

A060 DICE ATTACH簡介

工作描述:將DICE黏至SUBSTRATE 上 機台型號:ESEC 2007

PANASONIC DA46L-H 銀膠型式:8355 ( 銀膠 )

QMI536 ( 白膠 )TACH 牛牛文档分享PBGA 後段流程

首頁

簡述 PBGA封裝製程 PBGA前段流程 PBGA後段流程

簡報地圖

PBGA 後段流程

A116 PLASMA

A120 MOLDING

A160

POST MOLD CURE

A216

BALL MOUNT

A218

CLEAR

A225

SINGULATION 牛牛文档分享A075PLASMA

首頁

簡述 PBGA封裝製程 PBGA前段流程 PBGA後段流程

簡報地圖

A075 PLASMA簡介

工作描述:將烘乾後之產品以離子轟擊方式 清洗DICE與SUBSTRATE表面

機台型號:鈦昇 PLASMAX-800 II 反應氣體:氬氣(MA

首頁

簡述 PBGA封裝製程 PBGA前段流程 PBGA後段流程

简述微电子封装基本工艺流程

简述微电子封装基本工艺流程微电子封装听起来是不是特别高大上呀?其实呀,它的基本工艺流程就像一场奇妙的旅行呢。

一、芯片制备。

这可是整个微电子封装旅程的起点哦。

芯片的制备就像是精心打造一颗超级微小又无比强大的“心脏”。

先从硅晶圆开始,这个硅晶圆就像是一块神奇的“地基”,要在上面进行超级精细的加工。

比如说光刻啦,光刻就像是在硅晶圆上画画,不过这个画笔超级精细,能画出只有纳米级别的图案呢。

然后还有蚀刻,蚀刻就像是把不需要的部分去掉,只留下我们想要的电路图案。

这一道道工序就像打造艺术品一样,每一步都得小心翼翼,稍微出点差错,这颗“心脏”可能就不那么完美啦。

二、芯片贴装。

芯片做好了,接下来就要把它安置到合适的地方啦,这就是芯片贴装环节。

这时候就像给芯片找一个温暖的“小窝”。

通常会用到一些特殊的材料,比如黏合剂之类的。

把芯片稳稳地粘在封装基板上,这个过程可不能马虎哦。

要保证芯片和基板之间的连接非常牢固,就像盖房子时把柱子稳稳地立在地基上一样。

如果贴装得不好,芯片在后续的使用过程中可能就会出问题,就像房子的柱子不稳,那房子可就危险啦。

三、引线键合。

这可是个很有趣的环节呢。

它就像是在芯片和封装基板之间搭建起一座座“小桥”。

通过金属丝,比如说金线之类的,把芯片上的电极和封装基板上的引脚连接起来。

这个过程就像绣花一样精细,要把每一根金属丝都准确无误地连接好。

想象一下,那么多微小的连接点,就像在微观世界里编织一张精密的网。

如果有一根金属丝连接错了或者没连接好,那信号可就不能正常传输啦,就像桥断了,路就不通了呀。

四、灌封。

灌封就像是给整个芯片和连接部分穿上一层保护“铠甲”。

会用一些特殊的封装材料,把芯片、金属丝这些都包裹起来。

这个封装材料就像一个温柔的“保护罩”,它能防止芯片受到外界的干扰,比如湿气啦、灰尘啦之类的。

就像给我们珍贵的东西放在一个密封的盒子里一样,让它在里面安安稳稳的。

而且这个保护罩还能起到一定的散热作用呢,芯片在工作的时候会发热,如果热量散不出去,就像人在一个闷热的房间里一样,会很不舒服,时间长了还会出问题呢。

芯片封装基本流程及失效分析处理方法

芯片封装基本流程及失效分析处理方法一、芯片封装芯片封装的目的在于对芯片进行保护与支撑作用、形成良好的散热与隔绝层、保证芯片的可靠性,使其在应用过程中高效稳定地发挥功效。

二、工艺流程流程一:硅片减薄分为两种操作手段。

一是物理手段,如磨削、研磨等;二是化学手段,如电化学腐蚀、湿法腐蚀等,使芯片的厚度达到要求。

薄的芯片更有利于散热,减小芯片封装体积,提高机械性能等。

其次是对硅片进行切割,用多线切割机或其它手段如激光,将整个大圆片分割成单个芯片。

流程二:将晶粒黏着在导线架上,也叫作晶粒座,预设有延伸IC晶粒电路的延伸脚,用银胶对晶粒进行黏着固定,这一步骤为芯片贴装。

流程三:芯片互联,将芯片焊区与基板上的金属布线焊区相连接,使用球焊的方式,把金线压焊在适当位置。

芯片互联常见的方法有,打线键合,载在自动键合(TAB)和倒装芯片键合。

流程四:用树脂体将装在引线框上的芯片封起来,对芯片起保护作用和支撑作用。

包封固化后,在引线条上所有部位镀上一层锡,保证产品管脚的易焊性,增加外引脚的导电性及抗氧化性。

流程五:在树脂上印制标记,包含产品的型号、生产厂家等信息。

将导线架上已封装完成的晶粒,剪切分离并将不需要的连接用材料切除,提高芯片的美观度,便于使用及存储。

流程六:通过测试筛选出符合功能要求的产品,保证芯片的质量可靠性;最后包装入库,将产品按要求包装好后进入成品库,编带投入市场。

三、芯片失效芯片失效分析是判断芯片失效性质、分析芯片失效原因、研究芯片失效的预防措施的技术工作。

对芯片进行失效分析的意义在于提高芯片品质,改善生产方案,保障产品品质。

四、测试方法1、外部目检对芯片进行外观检测,判断芯片外观是否有发现裂纹、破损等异常现象。

2、X-RAY对芯片进行X-Ray检测,通过无损的手段,利用X射线透视芯片内部,检测其封装情况,判断IC封装内部是否出现各种缺陷,如分层剥离、爆裂以及键合线错位断裂等。

3、声学扫描芯片声学扫描是利用超声波反射与传输的特性,判断器件内部材料的晶格结构,有无杂质颗粒以及发现器件中空洞、裂纹、晶元或填胶中的裂缝、IC封装材料内部的气孔、分层剥离等异常情况。

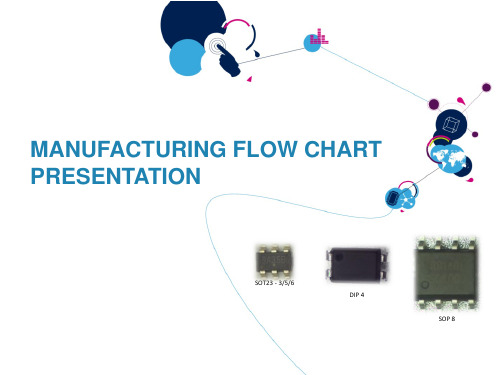

封装工艺流程简介(英文版)

Wire Bond

DB Glue Cure WB QC Visual MD PMC

8

Function

To bond wires on the die and on the package leads, in order to connect die and leads to realize electrically link.

Products Application Overview

Advance

- Powertrain (动力传动) - Safety (安全) - Car Multimedia (汽车) - Lighting (灯塔) - Alarm (报警) - Navigation System (逻辑系统)

4

Home Entertainment & Display (HED)

SOP

DIP

SOP

DIP

SOT

SOT

Unit with Wire bonding

Molding Compound

Machine Type: FUSHI SANJIA ( SKMP250) Machine Characteristic 1. Half-automated 2. High Capacity (Dip and Sot: 12 pcs / per mold; Sop: 8 pcs / per mold ) 3. Easier for in process control

Machine Type: ASM iHAWK Machine Characteristic: 1. Good flexibility: suitable for all dimension Cu and Ag on lead frame and die. 2. Bonding at room temperature. 3. Protect atmosphere not need.

IC芯片封装测试工艺流程

• 按封装材料划分为: 金属封装、陶瓷封装、塑料封装

• 按照和PCB板连接方式分为: PTH封装和SMT封装

• 按照封装外型可分为: SOT、SOIC、TSSOP、QFN、QFP、BGA、CSP等;

All right reserved © Shanghai Imart 360

Write Epoxy 点银浆

Die Attach 芯片粘接

Epoxy Cure 银浆固化

Epoxy Storage: 零下50度存放;

Epoxy Aging: 使用之前回温,除 去气泡;

Epoxy Writing: 点银浆于L/F的Pad 上,Pattern可选;

All right reserved © Shanghai Imart 360

➢主要功能为:在熔融状态下将Die和Lead Frame包裹起来, 提供物理和电气保护,防止外界干扰;

➢存放条件:零下5°保存,常温下需回温24小时;

All right reserved © Shanghai Imart 360

Raw Material in Assembly(封装原材料)

【Epoxy】银浆

FOL– Wire Bonding 引线焊接

※利用高纯度的金线(Au) 、铜线(Cu)或铝线(Al)把 Pad 和 Lead通过焊接的方法连接起来。Pad是芯片上电路的外接 点,Lead是 Lead Frame上的 连接点。

W/B是封装工艺中最为关键的一部工艺。

All right reserved © Shanghai Imart 360

De-Taping 去胶带

➢将从晶圆厂出来的Wafer进行背面研磨,来减薄晶圆达到 封装需要的厚度(8mils~10mils);

半导体封装简介

EOL– Molding(注塑)

L/F L/F

Cavity

Molding Tool(模具)

➢EMC(塑封料)为黑色块状,低温存储,使用前需先回温。其特 性为:在高温下先处于熔融状态,然后会逐渐硬化,最终成型。

➢Molding参数:

Molding Temp:175~185°C;Clamp Pressure:3000~4000N; Transfer Pressure:1000~1500Psi;Transfer Time:5~15s; Cure Time:60~120s;

半导体封装简介

一、半导体封装介绍 二、封装主要原材料 三、封装工艺流程—IC芯片 四、封装工艺流程—功率模块

一、半导体封装介绍

1.1 半导体工艺流程

目前半导体材料已经发展到第三代,第一代以硅(Si)为代表材料;第二代以砷化镓(GaAs)为代表材料; 第三代以碳化硅(SiC)和氮化镓(GaN)为主流材料。目前Si仍然是半导体行业使用最多的材料。

二、封装原材料简介 2.1 wafer(晶圆)

【Wafer】晶圆

2.2 【Lead Frame】引线框架

➢提供电路连接和Die的固定作用; ➢主要材料为铜,会在上面进行镀银、NiPdAu等材料; ➢L/F的制程有Etch和Stamp两种; ➢易氧化,存放于氮气柜中,湿度小 于40%RH; ➢除了BGA和CSP外,其他Package都会采用Lead Frame,BGA采用的是Substrate;

➢磨片时,需要在正面(Active Area)贴胶带保护电路区域, 同时 研磨背面。研磨之后,去除胶带,测量厚度;

FOL– Wafer Saw晶圆切割

Wafer Mount 晶圆安装

Wafer Saw 晶圆切割

SIP封装简介标准版文档

第八页,共11页。

三、SIP产品(chǎnpǐn)应用

• 近年来,SiP产品的市场需求迅猛增长。以前,SiP的产品通常主要应用相对较 小的PCB设计及低功耗产品应用中,如: ,数码摄像机, 汽车电子等。在 DDR存储器工作频率不断的提高,客户在使用高速DDR存储器设备进行相关设 计的时候,不断遇到成本,散热设计,研发时间不够等严重影响项目开发的风 险(fēngxiǎn)问题。因此,大部分客户,便在针对应用产品(如数字电视,数 码录像机)设计时,也主要考虑使用SiP的设计方式,从而进一步降低系统的成 本及提高可靠性。

指芯片(Die)和不同类型的基板和塑封料(EMC)形 成的不同外形的封装体。

IC Package种类很多,可以(kěyǐ)按以下标准分类:

按封装材料划分为: 金属封装、陶瓷封装、塑料封装 按照和PCB板连接方式分为: PTH封装和SMT封装 按照封装外型可分为: SOT、SOIC、TSSOP、QFN、QFP、BGA、CSP等2

二、SIP、SOC、SOB几方面(fāngmiàn)性 能对比

• SIP(System In a Package系统级封装)是将多种功能芯片,包括(bāokuò)处理 器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能. SiP的主 流封装形式是BGA.与SOC(System On a Chip系统级芯片)相对应,不同的是系 统级封装是采用不同芯片进行并排或叠加的封装方式,而SOC则是高度集成的芯片 产品.SOB( System On board)则是基于基板方式的封装.

第二页,共11页。

IC Package (IC的封装形式 (xíngshì))

• 按封装材料(cáiliào)划分为: •

塑料(sùliào) 封装

半导体流程介绍

去框成型~L/F

封胶

出货

正印 包装

稳定烘烤

钉架产品流向

外观

植球 去框成型

回焊 助焊剂清洗

将前制程整条产品经由本站作业成型为一颗的IC,并将IC置放于TRAY盘后 ,再给下制程。

1

2

去框

3

26

4

成型

去框成型~L/F—QFN、LF/TF BGA

封胶

出货

正印 包装

稳定烘烤

钉架产品流向

外观

植球 去框成型

二光检查(2/O)

钉架产品流向

电桨清洗

晶粒粘贴

银胶烘烤

基板产品流向

粘上晶粒的钉架(基板), 送至烤箱把银胶烤干, 使晶粒得以固定,在钉

架(基板)上

烤箱

Oven

13

电桨清洗

研磨

后段

晶圓黏貼 三光(3/O)

晶片切割 焊线站

二光检查(2/O)

钉架产品流向

电桨清洗

晶粒粘贴

银胶烘烤

基板产品流向

电浆清洗机:清洗基板(Substrate)与晶粒(Die)表面异物及污染

回焊 助焊剂清洗

QFN、LF BGA产品在完成前面各项制造流程后,需进行产品切割,如同将 晶圆切割开来取出晶片一般,透过机台切割基板取区成品IC

27

外观

封胶

出货

正印 包装

稳定烘烤

钉架产品流向

外观

植球 去框成型

回焊 助焊剂清洗

产品包装前利用Laser或CCD检测产品外观尺寸(平面度、脚弯、OFFSET)

2010/11/04

2010/11/05

31

加 强 做 责 任 心,责 任到人 ,责任 到位才 是长久 的发展 。20.11.1120.11.11Wednesday, November 11, 2020

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

秦天恒 王柳斌

粘晶(Die Attach)操作过程

1):使用高倍显微镜全面检查芯片,并确认粘晶方向。 2):①.使用涂抹棒均匀涂抹EPOXY。

②.再次确认芯片方向后,使用EFD吸取并将芯片放置到管壳中心。 ③.使用拨动棒调整位置到管壳正中心。

3):Epoxy

Curce Range:20-40) ③.十字线校正,High/Low高低倍各做两次。

④.点下Bond Heat Relearn.重新认识键合高度。

二>.根据方案要求制作程序。

①.创建Die : Teach new ref sys → Teach Die Ref →Add New Operator Points → Add Die Eye Points → Add New Bond Sites . ②. 创建Lead: Teach new ref sys → Teach Lead Ref →Add New Operator Points → Add Lead Eye Points → Add New Lead locates . ③.若方案有接地线,则需Teach Down Ref.

焊线(Wire Bond)操作过程

三>.根据芯片适应性编辑基本参数。 ①.load Bond 参数。 ②.编辑Ball参数,设置金线直径。 ③.编辑Loop参数,设置Loop类型。 四>.开始金线焊接。 ①.穿入金线,并去除线尾,烧球。 ②.按下键盘上的RUN开始生产一根线后,确认焊接情况。 ③.生产完成一颗后确认是否和方案相同。 ④.生产完成后,生产人员确认所有产品是否存在缺陷。 ⑤.更换另一名工程师确认所有产品是否存在缺陷。 ⑥.Double Confirm后,进行塑封/盖玻璃盖子/盖管壳/打包。

塑封(Molding)操作过程

①.将烤盘温度升至80℃。 ②.将要点胶的芯片放于烤盘上。 ③.使用无尘纸清洁胶头。 ④.调节合适的流量。 ⑤.脚踩EFD,流出黑胶,待黑胶缓慢的充满芯片后,取下胶体。 ⑥.等待十分钟后将温度升至120℃烘烤20分钟。 ⑦.观察胶体凝固后,取下芯片进行打包。

将粘晶后的芯片放于低倍显微镜确认后。

银胶放入烤箱恒温130℃烘烤45分钟后取出。 红胶、透明胶放到烤盘上 80 ℃烘烤10分钟后,再升温120 ℃烘烤30分钟后取 出。

焊线(Wire Bond)操作过程

一>:根据方案要求更换金线、更换劈刀、更换/调整加热. 更换劈刀方法:

①.使用扭力扳手取下/安装劈刀,安装时扭力扳手听到“啪啪”即可。

封装完成后作业步骤

封装完成后: ①.申请开单。 ②.封装好的产品和客户剩余芯片寄回客户/按客户要求转交其他部门。 ③.记录本次作业内容、时间、署名方便查找。

PS:各个流程时间计算 接单确定打线方案20min 黏晶作业40~50min 打线作业30~60min 封胶作业40min 打包结案作业15min