基本RS锁存器和D触发器-器件实验报告

触发器的功能转换

实验四触发器及其功能转换一、实验目的1、掌握基本RS、JK、D和T触发器的逻辑功能2、掌握集成触发器的逻辑功能及使用方法3、熟悉触发器之间相互转换的方法二、实验原理触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。

1、基本RS触发器图4-1为由两个与非门交叉耦合构成的基本RS触发器,它是无时钟控制低电平直接触发的触发器。

基本RS触发器具有置“0”、置“1”和“保持”三种功能。

通常称S为置“1”端,因为S=0(R=1)时触发器被置“1”;R为置“0”端,因为R=0(S=1)时触发器被置“0”,当S=R=1时状态保持;S=R=0时,触发器状态不定,应避免此种情况发生,表9-1为基本RS触发器的功能表。

基本RS触发器。

也可以用两个“或非门”组成,此时为高电平触发有效。

2、JK触发器在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。

本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。

引脚功能及逻辑符号如图4-2所示。

JK触发器的状态方程为Q n+1=J Q n+K Q nJ和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“与”的关系。

Q与Q为两个互补输出端。

通常把 Q=0、Q=1的状态定为触发器“0”状态;而把Q=1,Q=0定为“1”状态。

图4-2 74LS112双JK触发器引脚排列及逻辑符号下降沿触发JK触发器的功能如表4-2表4-2注:×— 任意态 ↓— 高到低电平跳变 ↑— 低到高电平跳变Q n (Q n )— 现态 Q n+1(Q n+1 )— 次态 φ— 不定态 JK 触发器常被用作缓冲存储器,移位寄存器和计数器。

3、D 触发器在输入信号为单端的情况下,D 触发器用起来最为方便,其状态方程为 Q n+1=D n,其输出状态的更新发生在CP 脉冲的上升沿,故又称为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前D 端的状态,D 触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生等。

实验八 触发器

1 0

1S C1 1R

Q主

1S C1

Q

CLK K

Q主

1R

Q

R主=0

,即Q*= 1 , Q* = 0

5.4 脉冲触发的触发器

④J=1,K=1 若Q=0, Q=1 S主=1,R主=0

在CLK=1时,主 触发器翻转为“1” 即 Q*主= 1 在CLK的 Q*= 1 若Q=1, Q=0 在CLK的

J

1 1

1S C1 1R

Q主

1S C1

Q

CLK K

Q主

1R

Q

,从触发器由“0 ”翻转为“1”,即 S主=0 在CLK=1时,主触 发器翻转为“0”, 即 Q*主= 0 Q*= Q

R主=1

,即Q*= 0, Q* = 1

5.4 脉冲触发的触发器

其功能表如表5.4.2所示 表5.4.2

CLK J

实验八 触发器

实验目的

1、掌握基本RS、JK、T和D触发器的逻辑功能

2、掌握集成触发器的功能和使用方法 3、熟悉触发器之间相互转换的方法

实验原理

触发器概述 定义:能够存储1位二值信号的基本单元电路。 特点:a.具有两个能自行保持的稳定状态,用来 表 示逻辑状态的0和1,或二进制数的0和1 ; b.根据不同的输入信号可以置1或0. 分类: a. 按触发方式:电平触发器、脉冲触发器和边沿 触发器 b. 按逻辑功能方式:SR锁存器、JK触发器、D触 发器、T触发器、T触发器 c. 按结构:基本SR锁存器、同步SR触发器、主 从触发器、维持阻塞触发器、边沿触发器等

Q 1 0 1

× 0 1

1

也称为D锁存器,其特点是 在CLK的有效电平期间输出 状态始终跟随输入状态变化, 即输出与输入状态相同。

基本RS触发器逻辑功能测试

实训九基本R-S触发器功能测试一、实训目的1.通过实训熟悉基本RS触发器的逻辑功能与特点;2.通过实训掌握基本RS触发器的测试方法;3.通过实训熟悉异步输入信号RD、SD、RD、SD的作用;4.通过实训掌握基本RS触发器的典型应用;二、实训原理基本RS触发器就是由两个与非门交叉耦合组成,它就是最基本的触发器,也就是构成其它复杂触发器电路的一个组成部分。

当R D=S D=1时,两个与非门的工作都尤如非门,Q接至与非门G2的输入,使G2输出为Q;Q接至与非门G1的输入,使G1的输出为Q。

从而使触发器维持输出状态不变。

三、实训仪器与设备S303-4型(或其它型号)数字电路实训箱一只;SR8(或其它型号)双踪示波器一只;直流稳压电源一台;74LS00 二输入四与非门1片。

四、实训内容与步骤1.两个TTL与非门首尾相接构成的基本R-S触发器的电路如图7-2-1所示逻辑电路。

为图9-1 基本R-S触发器功能测试2.按表9-1所示的顺序在Sd、Rd两端信号,观察并记录R-S触发器Q端的状态,并将结果填入表9-1中表9-13.Sd4.Sd端接高电平,Rd端加脉冲。

5.令Sd=Rd,在Sd端加脉冲。

6.记录并观察2、3、4三种情况下,Q,Q n+1端的状态。

从中总结基本R-S触发器的Q端的状态改变与输入端的关系。

五、实训思考题试根据基本R-S触发器给定的输入信号波形画出与之对应的输出端的波形;试写出基本R-S触发器的约束方程,并说明哪个就是复位端、哪个就是置位端?六、训注意事项接线时要注意电路图中各引脚的编号,连接时不要接错;手动施加0、1输入电平时要注意开关动作的稳定性与可靠性,要避免开关的抖动;用双踪示波器观察输出波形时,要注意选择一个较为合适的输入信号的频率。

实训十、计数器的功能测试一、实训目的1.掌握计数器的工作原理;2.通过实训熟悉计数器的功能特点与典型应用;3.通过实训掌握如何利用现有集成计数器来构成N进制计数器的方法。

实验四触发器

SD

Q SD RD

S R

Q Q

RD

Q

G2 (a) (b)

图2-6-1 基本RS触发器结构(a)和逻辑符号(b)

电气工程与自动化学院

College of Electrical Engineering and Automation

表2-6-1 基本与非RS锁存器真值表

输入端 输出端

SD R D

0 0

电气工程与自动化学院

College of Electrical Engineering and Automation

6.同步三分频电路 (1) 电路如图2-6-10所示,分析此电路的逻辑功能。 (2) 时钟脉冲由实验箱的单次脉冲源提供,记录和的显示情 况,判断是否正确。 (3) 时钟脉冲由实验箱的脉冲信号源提供,频率范围波段开 关拨至1kHz位置,用双踪示波器观察CLK脉冲、和的波形, 记录下来,判断时钟脉冲触发沿、计数状态等是否正确。

电气工程与自动化学院

College of Electrical Engineering and Automation

4、JK触发器转换成T触发器、触发器和D触发器 将JK触发器的J、K两端连在一起,作为T端,就得到T 触发器。如图2-6-4(a)所示,其状态方程为 。 Q n 1 TQ n TQ n T触发器的功能如表 2-6-4所示。

电气工程与自动化学院

College of Electrical Engineering and Automation

Qn

0

1 0 1 0 1

Q n 1

0 1 1 0 1 0 1 1 1 1

电气工程与自动化学院

College of Electrical Engineering and Automation

三态输出触发器和锁存器实验报告有数据

三态输出触发器和锁存器实验报告有数据1. 理解三态输出触发器和锁存器的工作原理;2. 掌握三态输出触发器和锁存器的实验方法;3. 熟悉使用示波器进行实验测量和数据分析。

实验器材:- 简易逻辑实验箱- 三态输出触发器芯片(例如74LS373)- 锁存器芯片(例如74LS175)- 计时器芯片(例如555)- 示波器- 电源和电线等其他辅助器材实验原理:1. 三态输出触发器(Tri-state Output Flip-Flop):三态输出触发器是一种特殊的双稳态触发器,其输出可以处于三种状态之一: 高电平、低电平和高阻态(High-Z)。

利用一个使能端(Enable)来控制输出状态,当使能端为低电平时,输出处于高阻态,此时输出不受触发器的状态控制;当使能端为高电平时,输出由触发器的状态决定。

74LS373是一种广泛使用的三态输出触发器芯片,其引脚功能如下(以16位为例):- D0 ~ D15: 数据输入端,用于输入要存储的数据;- OE:输出使能端,用于控制输出状态;- LE:锁存使能端,用于控制存储操作;- Q0 ~ Q15: 输出端,输出存储的数据。

实验中,我们将通过控制OE和LE端的电平来实现三态输出触发器的控制和数据存储。

2. 锁存器(Latch):锁存器是一种具有存储功能的触发器,可以通过控制使能端来实现数据的锁存和释放。

常见的锁存器有SR锁存器和D锁存器等。

74LS175是一种广泛使用的锁存器芯片,其引脚功能如下(以四位为例):- D0 ~ D3: 数据输入端,用于输入要存储的数据;- EN: 使能端,用于控制存储操作;- Q0 ~ Q3: 输出端,输出存储的数据。

实验中,我们将通过控制EN端的电平来实现锁存器的控制和数据存储。

实验步骤:实验一: 三态输出触发器实验1. 连接电路: 将74LS373芯片插入实验箱中,并按照引脚功能连接电路,包括数据输入端、输出端、输出使能端和锁存使能端等。

锁存器和D触发器

锁存器和D触发器锁存器和D触发器2010-10-05 09:34 D触发器是指由时钟边沿触发的存储器单元,锁存器指一个由信号而不是时钟控制的电平敏感的设备。

锁存器通过锁存信号控制,不锁存数据时,输出端的信号随输入信号变化,就像信号通过缓冲器一样,一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。

锁存器和D触发器实现的逻辑功能基本相同,都是暂存数据。

由与非门搭建的话,锁存器所耗用的逻辑资源比D触发器少,所以使用锁存器有更高的集成度,但锁存器有一下缺点:(1)对毛刺敏感,毛刺信号会传递下去,无异步复位端,不能在芯片上电时处在一个确定的状态;(2)会使静态时序分析变得复杂,可测性不好,不利于设计的可重用,所以当今的ASIC设计中除了CPU这种甚高速电路,一般不提倡使用锁存器;(3)FPGA器件中有大量的D触发器结构而没有锁存器这种现成的结构,使用锁存器会更耗资源,如何避免使用锁存器:(1)时序逻辑电路中,可用带使能端的D触发器实现;(2)在组合进程中赋默认值;(3)对所有输入条件赋输入值,以覆盖所有条件分支(特别是if.else.和case结构);(4)避免产生组合电路反馈,组合电路反馈会引起精确静态时序分析难以实现等一系列问题。

在有些设计中,不可避免的需要用到锁存器,如在PCI接口设计中要完成PCI规范中对Reset功能的定义。

可以通过多位选择器,有测试模式管脚做选择控制位来使设计是可测试的。

"触发器"泛指一类电路结构,它可以由触发信号(如:时钟,置位,复位等)改变输出状态,并保持这个状态直到下一个或另一个触发信号来到时,触发信号可以用电平或边沿操作.锁存器是触发器的一种应用类型.在CMOS电路中典型的锁存器(LATCH)是由两个反相器和两个数据开关组成,其中输入数据开关在闸门(GATE)电平操作下开启送入数据.当闸门关闭后,另一个数据开关开启,使两个反相器的串联闭合,形成RS触发器类型的正反馈电路,数据保持在这个RS触发器中,以达到锁存的目的,直到下一个闸门周期.由两个这样的锁存器可以级联成主从结构,并执行互补的操作.即前一个送入数据时,后一个保持先前的数据,而前一个锁存数据时,后一个送入这个新数据到输出端.形成一个边沿触发的D触发器,而闸门控制信号成为触发器的时钟.也可以认为D触发器是用时钟边沿锁存数据的,但习惯上不称其为锁存器LATCH.在CMOS芯片内部经常使用锁存器,但是在PCB板级结构上,建议用触发器在时钟边沿上锁存数据.这是因为在锁存器闸门开启期间数据的变化会直接反映到输出端,所以要注意控制闸门信号的脉冲宽度.而对于触发器,只考虑时钟的边沿latch和flip-flop都是时序逻辑,区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。

基本RS触发器逻辑功能测试

基本RS触发器逻辑功能测试实训九基本R-S触发器功能测试⼀、实训⽬的1.通过实训熟悉基本RS触发器的逻辑功能和特点;2.通过实训掌握基本RS触发器的测试⽅法;3.通过实训熟悉异步输⼊信号RD、SD、RD、SD的作⽤;4.通过实训掌握基本RS触发器的典型应⽤;⼆、实训原理基本RS触发器是由两个与⾮门交叉耦合组成,它是最基本的触发器,也是构成其它复杂触发器电路的⼀个组成部分。

当R D=S D=1时,两个与⾮门的⼯作都尤如⾮门,Q接⾄与⾮门G2的输⼊,使G2输出为Q;Q接⾄与⾮门G1的输⼊,使G1的输出为Q。

从⽽使触发器维持输出状态不变。

三、实训仪器和设备S303-4型(或其它型号)数字电路实训箱⼀只;SR8(或其它型号)双踪⽰波器⼀只;直流稳压电源⼀台;74LS00 ⼆输⼊四与⾮门 1⽚。

四、实训内容和步骤1.两个TTL与⾮门⾸尾相接构成的基本R-S触发器的电路如图7-2-1所⽰逻辑电路。

图 9-1 基本R-S触发器功能测试2.按表9-1所⽰的顺序在Sd、Rd两端信号,观察并记录R-S触发器Q端的状态,并将结果填⼊表9-1中表9-13.Sd4.Sd端接⾼电平,Rd端加脉冲。

5.令Sd=Rd,在 Sd端加脉冲。

6.记录并观察2、3、4三种情况下,Q,Q n+1端的状态。

从中总结基本R-S触发器的Q 端的状态改变和输⼊端的关系。

五、实训思考题试根据基本R-S触发器给定的输⼊信号波形画出与之对应的输出端的波形;试写出基本R-S触发器的约束⽅程,并说明哪个是复位端、哪个是置位端六、训注意事项接线时要注意电路图中各引脚的编号,连接时不要接错;⼿动施加0、1输⼊电平时要注意开关动作的稳定性和可靠性,要避免开关的抖动;⽤双踪⽰波器观察输出波形时,要注意选择⼀个较为合适的输⼊信号的频率。

实训⼗. 计数器的功能测试⼀、实训⽬的1.掌握计数器的⼯作原理;2.通过实训熟悉计数器的功能特点和典型应⽤;3.通过实训掌握如何利⽤现有集成计数器来构成N进制计数器的⽅法。

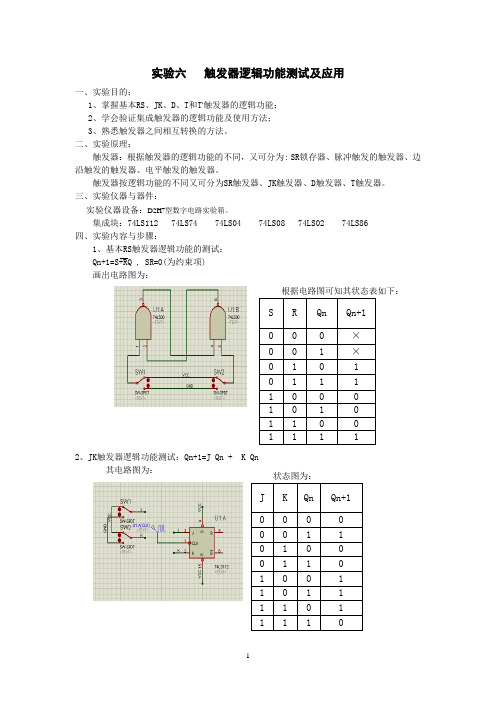

实验6 触发器逻辑功能测试及应用

实验六触发器逻辑功能测试及应用一、实验目的:1、掌握基本RS、JK、D、T和T′触发器的逻辑功能;2、学会验证集成触发器的逻辑功能及使用方法;3、熟悉触发器之间相互转换的方法。

二、实验原理:触发器:根据触发器的逻辑功能的不同,又可分为: SR锁存器、脉冲触发的触发器、边沿触发的触发器、电平触发的触发器。

触发器按逻辑功能的不同又可分为SR触发器、JK触发器、D触发器、T触发器。

三、实验仪器与器件:实验仪器设备:D2H+型数字电路实验箱。

集成块:74LS112 74LS74 74LS04 74LS08 74LS02 74LS86四、实验内容与步骤:1、基本RS触发器逻辑功能的测试:Qn+1=S+RQ , SR=0(为约束项) 画出电路图为:2、JK触发器逻辑功能测试:Qn+1=J Qn + K Qn其电路图为:根据电路图可知其状态表如下:S R Qn Qn+10 0 0 ×0 0 1 ×0 1 0 10 1 1 11 0 0 01 0 1 01 1 0 01 1 1 1状态图为:J K Qn Qn+10 0 0 0 0 0 1 1 0 1 0 00 1 1 01 0 0 1 1 0 1 1 1 1 0 1 1 1 1 03、D触发器逻辑功能测试:(1)异步输入端功能测试:S R Qn Qn+11 1 0 01 1 1 10 1 0 00 1 1 01 0 0 11 0 1 10 0 0 不定0 0 1 不定(2)D触发器逻辑功能测试:根据电路图列出状态表为:D Qn Qn+10 0 00 1 01 0 11 1 14、不同类型时钟触发器间的转换:JK转换为D触发器:D转换为JK 触发器:Qn+1=J Qn + K Qn=D(Qn=1时,K=D,J为任意数,Qn=0时,J=D,K任意数。

) JK转换为T触发器:T转换为JK触发器:Qn+1=J Qn + K Qn Qn+1=T Qn + T Qn 得到T=JJK转换为RS触发器:RS转换为JK触发器:Qn+1=J Qn + K Qn Qn+1=S + R Q 得到S= J Qn,R=K五、实验体会与要求:1、根据实验结果,写出各个触发器的真值表。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基本RS触发器和D触发器

一、实验目的:

熟悉几种常见触发器的逻辑功能,准确理解触发器特性描述和正确对其逻辑功能进行测试操作。

熟练使用示波器来观看触发器的时序图。

二、实验内容:

1.搭接一个基本RS触发器,对其功能进行测试,填写基本RS触发器特性表。

2.对边缘D触发器74 LS74的逻辑功能进行测试,填写D触发器的特性表。

3.用D触发器实现计数功能和分频功能。

4.用4个D触发器设计一个4位的环形计数器。

三、实验条件:

1、硬件基础电学实验箱、双踪示波器、电源。

2、元器件:74LS00、74LS74、74LS175。

四、实验过程:

1、搭接一个基本RS触发器,对其功能进行测试。

a)实验原理:

基本RS触发器是由二个与非门交叉藕合构成的。

基本RS触发器具有置"0"、置"1"

和"保持"三种功能。

通常称s为置"1"端,因为s=0时触发器被置"1";R为置"0"端,因为R=0时触发器被置"0",当s= R=1时状态保持。

基本RS触发器也可以用二个"或非门"组成,此时为高电平触发器。

b) 实验电路图:

c)RS触发器特性表:

S R Q n Q n+1

0 0 0 1

0 0 1 1

0 1 0 1

0 1 1 1

1 0 0 0

1 0 1 0

1 1 0 0

1 1 1 1

d)实验现象以及结论:

现象:当s=0时,r=1,结果置1。

当s=1时,r=0,结果置0。

当s=1时,r=1,次态与现态相同,即保持。

当s=0时,r=0,出现不稳定状态,如果连接Q'n+1,可以看到其与Qn+1的值相同,这个状态是要避免的。

结论:用74LS00搭接的基本RS触发器功能正确。

2、对边缘D触发器74 LS74的逻辑功能进行测试。

a)实验内容:

i.Clk—>Q的波形(500Khz的时钟信号)

ii.D—>Q的波形

iii.Clk—>D的波形(100Khz的时钟信号)

b)实验原理:

双上升沿D触发器(有预置端和清除端)的逻辑图:

c) 实验电路图:

d)实验现象以及结论:

i.Clk—>Q:ii.D—>Q: iii.Clk—>D:

Iiii.清零:Iiiii.置1

逻辑功能表:

PR CLR CLK D Q Q'

0 1 X X 1 0

1 0 X X 0 1

0 0 X X 1 1

1 1 ↑ 1 1 0

1 1 ↑0 0 1

1 1 ↑X Q0 Q'0

结论:74LS74逻辑功能测试正确。

3、用D触发器实现计数功能和分频功能。

a)实验原理:

用D触发器实现4分频电路:

(1)需要两个D触发器。

因为输出的改变只在时钟上升沿,所以1个触发器是2分频,2个触发器实现4分频。

(2)第一个D触发器的输入时钟为需要分频的系统时钟,将该D触发器的输出取反,做该触发器的输入。

这样才能保证每次遇到时钟上升沿,输出与上一次都是相反的,即频率减半。

(3)第二个触发器的时钟为第一个D触发器的输出,即Q。

将第2个D触发器的输出取反做其输入。

这一步与上相同,相当于将2个触发器串联,实现2分频再2分频。

b) 实验电路图:

c) 实验数据以及结论:

波形参

数最大值最小值峰峰值周期频率

脉冲宽

度

占空比

CH1 4.00v 0.00V 4.00V 2.000us 500000H

Z

1.000us 50%

CH2 4.00v 0.00V 4.00V 8.000us 125000H

Z

4.000us 50%

结论:用2个触发器实现了4分频的效果。

4、用4个D触发器设计一个4位的环形计数器。

a)实验原理:

环形计数器实现0000-0001-0010-0100-1000-0000的循环。

通过触发器将1一级级传下去,如果触发器输出全部都为0,则低位触发器置1。

当时钟处于上升沿时,D触发器如同透明,输出等于输入,相当于每一个触发器的次态等于上一级触发器的现态,所以1会一级级传上去。

但是最前面的或非门控制了当不全为0时,低位输入始终控制在0上。

这样保证电路上最多只有一个1。

b)实验电路:。