集成双向移位寄存器

双向移位寄存器 (2)

双向移位寄存器

双向移位寄存器是一种能够在输入数据串和输出数据串之间实现双向数据传输的寄存器。

它可以通过控制信号来实现数据的左右移位操作。

双向移位寄存器通常由多个触发器组成,每个触发器都能够存储一个比特位。

这些触发器之间通过电路连接,形成一个寄存器。

在双向移位寄存器中,有两个输入端和两个输出端。

一个输入端被称为数据输入端,用于将外部数据输入到寄存器中。

另一个输入端被称为控制输入端,用于控制数据的移位方向(左移或右移)。

当控制输入端接收到移位信号时,寄存器可以执行左移或右移操作。

左移操作将所有触发器中存储的数据向左移动一位,其中最左边的触发器的输出位被丢弃,最右边的触发器的输入位接收一个新的数据位。

类似地,右移操作将

所有触发器中存储的数据向右移动一位,其中最右边的触

发器的输出位被丢弃,最左边的触发器的输入位接收一个

新的数据位。

双向移位寄存器的输出端将从寄存器中读取数据,并将其

作为输出数据串输出。

输出端和输入端可以通过控制信号

来切换,实现双向数据传输。

双向移位寄存器在许多应用中都有用途,比如数据缓冲和

数据传输等。

它可以灵活地处理不同方向的数据移位操作,并且能够实现高效的数据传输。

VHDL实验双向移位寄存器(完整版)

VHDL实验双向移位寄存器(完整版)实验课名称:VHDL硬件描述语言实验项目名称:双向移位寄存器专业名称:电子科学与技术班级:电科二班学号:***** 学生姓名:****教师姓名:****__2010__年_11_月_14_日组别_____________________同组同学_______________________ 实验日期_____年___月___日实验室名称______________成绩_____一、实验名称:双向移位寄存器二、实验目的与要求:实验目的:设计一个双向移位寄存器,理解移位寄存器的工作原理,掌握串入\并出端口控制的描述方法。

实验要求:通过VHDL编程,实现双向移位寄存器,要求有1个方向控制端、1个时钟脉冲输入、1个异步清零端、1个数据输入端以及8位的并行数据输出端,具体接口说明如下图所示。

clk:移位寄存器时钟脉冲输入,上升沿有效;din:串行数据输入端;clr:异步清零信号,高电平有效;dir:方向控制端,要求低电平左移,高电平右移;dout[7..0]:8位数据并行输出端;首先在QuartusII上进行功能和时序仿真,之后通过器件及其端口配置下载程序到SOPC开发平台中。

在硬件实现中,要求:1. 用实验平台的按键实现时钟控制(clk)、方向控制(dir)、清零(clr)以及数据输入(din):端口名按键名功能clk 键7 时钟控制din 键8 数据输入clr 键1 异步清零dir 键5 方向控制2. 用实验平台的LED发光阵列的LED1,LED8显示并行数据的输出。

三、实验内容:, 新建工程:1、打开Quartus,新建工程,选择好路径,工程顶层名为d_reg ;2、新建工程,如果包含已编好的文件则可以添加,如果无则可以略过 ;3、选择我们的器件信息:型号为:EP2C36F484C84、单击Next>,指定第三方工具,这里我们不指定第三方EDA工具,单击Next>后结束工程建立。

d触发器构成的双向移位寄存器

d触发器构成的双向移位寄存器一、概述双向移位寄存器是一种能够实现数据在两个方向上移位的寄存器,其常用于串行通信、计数器等电路中。

其核心部件为d触发器构成的双向移位寄存器。

二、d触发器d触发器是一种基本的时序电路,其输入为数据输入端d和时钟输入端clk,输出为输出端q和反相输出端q'。

当clk上升沿到来时,其将输入端d的值传输到输出端q上,并保持该状态直到下一个时钟上升沿到来。

三、双向移位寄存器1. 正向移位当控制信号sel=0时,数据从右侧进入寄存器,并从左侧出去。

具体实现方式为:将右侧d触发器的数据输入端连接至外部数据线,左侧d触发器的数据输入端连接至右侧d触发器的输出端。

2. 反向移位当控制信号sel=1时,数据从左侧进入寄存器,并从右侧出去。

具体实现方式为:将左侧d触发器的数据输入端连接至外部数据线,右侧d触发器的数据输入端连接至左侧d触发器的输出端。

四、构成原理双向移位寄存器由两个d触发器构成,其中一个为正向移位的d触发器,另一个为反向移位的d触发器。

控制信号sel用于控制数据的进出方向。

1. 正向移位当sel=0时,右侧d触发器接收外部数据输入,左侧d触发器接收右侧d触发器的输出。

当时钟上升沿到来时,右侧d触发器将数据传递至左侧d触发器,并保持该状态直到下一个时钟上升沿到来。

此时,左侧d触发器将其输出端的值传递至外部输出线。

2. 反向移位当sel=1时,左侧d触发器接收外部数据输入,右侧d触发器接收左侧d触发器的输出。

当时钟上升沿到来时,左侧d触发器将数据传递至右侧d触发器,并保持该状态直到下一个时钟上升沿到来。

此时,右侧d触发器将其输出端的值传递至外部输出线。

五、应用场景双向移位寄存器常用于串行通信、计数器等电路中。

在串行通信中,双向移位寄存器可实现数据在串行通信线路中的进出操作;在计数器中,双向移位寄存器可实现计数器的正向和反向计数操作。

六、总结双向移位寄存器是一种能够实现数据在两个方向上移位的寄存器,其核心部件为d触发器构成的双向移位寄存器。

d触发器构成的双向移位寄存器

D触发器构成的双向移位寄存器引言在数字电路中,双向移位寄存器是一种常见的电路元件,它能够在两个方向上进行数据的移位操作。

而D触发器则是常用的触发器类型之一,它具有存储数据、数据输入和数据输出的功能。

本文将介绍如何使用D触发器构成一个双向移位寄存器,并详细解释其设计原理、原理图以及工作原理等相关内容。

设计原理双向移位寄存器可以实现向左或向右移位的功能。

为了实现这一功能,我们可以使用两个D触发器进行串联,然后通过控制信号来选择数据的方向。

首先,我们需要了解D触发器的工作原理。

D触发器是一种有两个稳定状态的触发器,它有一个数据输入端D,一个时钟输入端CLK和一个输出端Q。

当时钟输入端的时钟信号从低电平变为高电平时,D触发器会将D端的数据存储到内部的状态变量中,并通过输出端Q输出。

借助D触发器的这种特性,我们可以构成一个双向移位寄存器,通过串联两个D触发器。

其中一个D触发器用于存储数据(称为存储触发器),另一个D触发器用于将存储触发器的数据移位(称为移位触发器)。

原理图下图是一个双向移位寄存器的原理图:+-----------------------------------------+| |D ---->| || 存储触发器 |>| +----------------+ |>|D0 | D触发器 | |>| +----------------+ |>| +----------------------+ || | | |CLK --->| | | || | 移位触发器 | |>|Q0 | | |>| | +-----------+ | |>| | |输入选择器 |----+ |>| | +-----------+ | || +----------------------+ |>|D1 |>| |>| Q1 || |+-----------------------------------------+工作原理下面将详细解释双向移位寄存器的工作原理。

数字电路与逻辑设计2寄存器移位寄存器

并行读出脉冲必须在经过5个移存脉冲后出 现,而且和移存脉冲出现旳时间错开。

D5

D4

D3

D2

D1

&

&

&

&

&

并行读出指令

串行输 入 1D

11001

CI

1D Q1

CI

1D Q2

CI

1D Q3

CI

1D

Q4

Q5

CI

移存脉冲CP

分析:假设串行输入旳数码为10011(左边先入)

串—并行转换状态表

序号 Q1 Q2 Q3 Q4 Q5

工作过程: ①在开启脉冲和时钟CP作用下,执行并

行置入功能。片ⅡQ3=DI6。 ②开启脉冲消失,在CP作用下,因为标志位0

旳存在,使门G1输出为1,使得SH/LD =1,执行右移移位寄存功能。 ③后来在移存脉冲作用,并行输入数据由片Ⅱ旳 Q3逐位串行输出,同步又不断地将片Ⅰ旳串 行输入端J,K=1旳数据移位寄存到寄存器。

末级输出反相后,接到串行输入端。

Q3Q2Q1Q0

1

0000

0001

0011

0111

∧

Q0Q 1Q2Q 3

CP D SR

74194

S0

1

S1

0

RD D 0 D 1 D2 D 3 D SL

1000

1100

1110

1111

0010

0101

1011

0110

清零

1001 0100

1010

1101

移位寄存器构成旳移位计数器

异步清零 同步置数

高位向低位移动(左移) 低位向高位移动(右移)

保持

3 、用集成移位寄存器实现任意模值 旳计数分频

移位寄存器——精选推荐

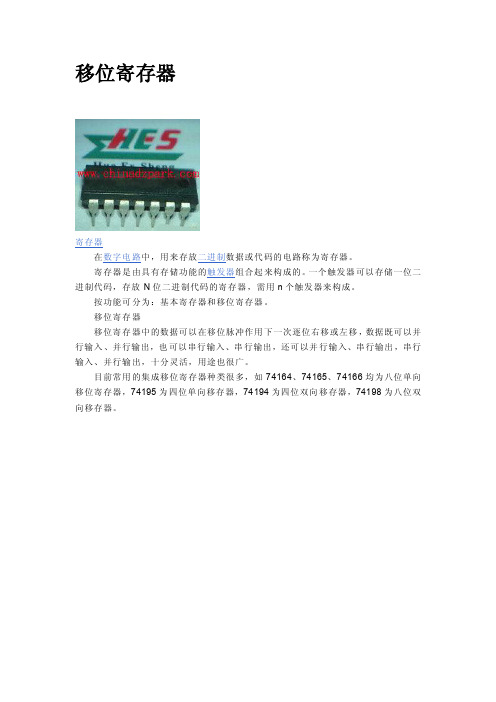

移位寄存器寄存器在数字电路中,用来存放二进制数据或代码的电路称为寄存器。

寄存器是由具有存储功能的触发器组合起来构成的。

一个触发器可以存储一位二进制代码,存放N位二进制代码的寄存器,需用n个触发器来构成。

按功能可分为:基本寄存器和移位寄存器。

移位寄存器移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

目前常用的集成移位寄存器种类很多,如74164、74165、74166均为八位单向移位寄存器,74195为四位单向移存器,74194为四位双向移存器,74198为八位双向移存器。

反馈移位寄存器(一)、反馈移位寄存器的介绍1. 什么是反馈移位寄存器ai表示二值(0,1)存储单元,ai的个数n成为反馈移位寄存器的级。

在某一时刻,这些级构成该反馈移位寄存器的一个状态,共有2n个可能状态,每一个状态对应于域GF(2)上的一个n维向量,用(a1,a2,a3,…an)表示。

在主时钟周期的周期区间上,每一级存储器ai都将内容向下一级ai-1传递,并根据寄存器的当前状态f(a1,a2,a3,…an)作为an的下一时间内容,即从一个状态转移到下一个状态。

其中函数f(a1,a2,a3,…an)称为该反馈移位寄存器的反馈函数。

2. 线性反馈移位寄存器和非线性反馈移位寄存器如果反馈函数f(a1,a2,a3,…an)是a1,a2,a3,…an 的线性函数函数,则该反馈移位寄存器是线性反馈移位寄存器用LFSR表示,比如:f(a1,a2,a3,…an)=kna1⊕kn-1a2⊕….⊕k2an-1⊕k1an,其中系数ki∈{0,1}(i=1,2,3,…,n)。

相应的如果反馈函数f(a1,a2,a3,…an)是a1,a2,a3,…an 的非线性函数函数,则该反馈移位寄存器是非线性反馈移位寄存器。

(二)、反馈移位寄存器的性质1.移位寄存器序列反馈函数f(a1,a2,a3,…an)为n元布尔函数。

寄存器和移位寄存器

Q0 Q1 Q2 Q3 CO

计数器

74LS138

STA

Y0

STB

Y1

STC

Y2

Y3

Y4

Y5

Y6

Y7

译码器

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

EXIT

本章小结

时序逻辑电路由触发器和组合逻辑电路构成, 其中触发器必不可少。时序逻辑电路旳输出 不但与输入有关,而且还与电路原来旳状态 有关。时序逻辑电路旳工作状态由触发器存 储和表达。

二、移位寄存器

Shift register 用于存储数码和使数码根据需要向左或向右移位。

单向移位 寄存器

左移 寄存器

右移 寄存器

每输入一种移位脉冲,移位寄存器 中旳数码依次向左移动 1 位。

每输入一种移位脉冲,移位寄存器 中旳数码依次向右移动 1 位。

双向移位 寄存器

在控制信号作用下,可实现右移 也可实现左移。

中规模集成计数器功能完善、使用以便灵活。 功能表是其正确使用旳根据。利用中规模集成 计数器可很以便地构成 N 进制(任意进制)计 数器。其主要措施为:

(1) 用同步置零端或置数端取得 N 进制计 数器。这时应根据 SN-1 相应旳二进制代码写 反馈函数。

(2) 用异步置零端或置数端取得 N 进制计 数器。这时应根据 SN 相应旳二进制代码写反 馈函数。

旳状态不变下,面即请寄看存置旳数数演码示保持不变。

寄存器旳构造特点

Q0 Q0

FF0 1D C1 R

Q1 Q1

FF1 1D C1 R

Q2 Q2

FF2 1D C1 R源自Q3 Q3FF3 1D C1 R

D0 CP CR D1

寄存器和移位寄存器

在输出端Q。 这样,在CP和RD两个控制信号的作用下电路完成寄存功能,原理图如图5-17。

一、寄存器

图5-15 D触发器构成的寄存器和集成芯片7477都只有一个控制脉冲,这样的寄存器 称为单拍工作方式的寄存器。如图5-17所示的寄存器有两个控制脉冲,称为双拍工作方式 的寄存器。

数字电子技术基础

寄存器和移位寄存器

小知识

构成寄存器的主要部分是触发器,由于触发器能够存 储一位二进制代码,所以N个触发器构成存储N位二 进制代码的寄存器。有时候寄存器中存放的数据要依 次向左移动或者向右移动,从而完成相应的数据处理, 这种具有移位功能的寄存器称为移位寄存器。

一、寄存器

寄存器可以由RS触发器、JK触发器、D触发器构成,各触发器通常在同一个时钟源的作用下工作。

三、寄存器应用举例

状态表如表5-9所示。其中,Q0~Q3是并行输出端;D0~D3是并行输入端;RD是直接

清零端;SI是串行输入端;LD是并行控制端;S是移位控制端。

表5-9 74LS179状态表

RD

S1

S0

CP

功能

1

1

X

右移

1

0

1

并行输入

1

0

0

保持

0

X

X

X

清零

数字电子技术基础

1、四位寄存器

由四个D触发器构成的四位寄存器,当CP为上升沿时,数码D0D1D2D3可以并行输入到各触发 器,这时,撤销CP信号,从D0D1D2D3送入的数码就可以存储在Q0Q1Q2Q3端,如图5-15所示。

图5-15 D触发器构成的寄存器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Q0

15

Q1 Q2 Q3

14 13 12

工作方式控制 CP M1 M0

11

10

9

CLR R

1 2 3

74LS194

S1 S0 L

4

5

6

7

8

RD DSR D0

右移 串行 输入

D3 DSL GND 左移 并行输入 串行 输入

D1 D2

74LS194功能表

74LS194集成电路可实现左移寄存器、右移寄 存器、并行寄存器三大功能。由M1M0操作模式 控制端的设置方式决定其功能。

4位扩展为8位

用 2个 4位移位寄存器串接,将右边寄存器的Q4接在其 左边寄存器的左移输入端DSL上;同样将左边寄存器的 Q3接在其右边寄存器的右பைடு நூலகம்输入端DSR上,可构成8位移 位寄存器。

并行—串行数据转换

脉冲分配器

RD

0 1 1 1 1 1 1(0) CP

M1 M0

功

能

直接清零

保 持 右移(从Q0向右移动) 左移(从Q3向左移动) 并行置数输入 保 持

0 0 1 1

0 1 0 1

74LS194应用举例

74LS194右移彩灯电路

74LS194左移彩灯电路

74LS194应用扩展

位数扩展 实现并行—串行数据转换 构成脉冲分配器

集成双向移位寄存器

北京铁路电气化学校 李凤玲

一、集成移位寄存器

集成移位寄存器有TTL和CMOS两大类集

成电路产品系列。

74LS194集成电路是TTL型常用的四位双向

移位寄存器。

二、集成双向移位寄存器74LS194

RD直接清零端,DSR为 右移串行输入端, DSL为左移串行输入端, D0D1D2D3 为四位并行 输入端, Q0 Q1 Q2 Q3为四位并 行输出端, CP为时钟脉冲输入端, M1M0为操作模式控制 端, GND接地端, VCC接电源+5V端。 VCC