EDA_DDS移相信号发生器

基于DDS的数字移相信号发生器

R G 4的高 1 E 3 O位输 出作为 P A路 R M与 P O B路 A D R 0的 D E 1

图 1 基 于 D S的数 字 移 相 信 号 发 生器 的原 理 图 D

输入 , 在此 , 将该输 出称为 D, D一方面作为一个 R M 的地址 O 端, 决定读取 R M的内容 , O 也就是 F U 。D另 一方 面与输人 OT

一

直 接 数 字 频 率 合 成 D S ( ic it r un y D Dr tDga Fe e c e il q Snhs e)是一种采用数字化技术、通过控制相位的变化速 yt ir ez

出, 完成一个周期性的动作 , 这个周期就是 D S合成信号 的一 D 个周期。

1 D S 相 的 实现 . 2 D 移 器 件 采 用 美 国 A T R 公 司 的 F G ( yl e LE A P A C c n o E 1 6 20 6 芯 片 来 实 现 。 于 A ea yl e P C Q 4 C PC Q 4C ) 对 h r c n I 6 2 0 6 C o E 的 应 用 开发 使 用 A e h r 司 的 E A开 发 软 件 ( ur s1 .) a公 D Q au一1 0 。 t 5

图 2:

1 基 于 D S的数 字移 相信 号发生 器 D

11 基 于 D S的数 字 移 相 信 号 发 生器 的工 作 原 理 . D

该 移相 信 号 发 生 器 是 基 于 D S技 术 而 实 现 的 ,其 原 理 框 D

图如 图 l 。 图 2 基 于 D S的 数 字移 相 信 号 发 生器 的 设 计 框 图 D 系 统 由一 个 3 加 法 器 ( D E 3 )一 个 3 寄 存 器 4位 A D R4、 4位

EDA课程设计--DDS信号发生器

电子课程设计电子课程设计------DDS信号发生器合成器信号发生器合成器学院:学院:专业班级:专业班级:专业班级:姓名:姓名:姓名:学号:学号:学号:指导老师:指导老师:指导老师:2012年12月直接数字频率合成器(直接数字频率合成器(DDS DDS DDS))一、 设计任务与要求直接数字频率综合技术,直接数字频率综合技术,即即DDS 技术,是一种新型的频率合成技术和信号产生方法。

利用EDA 技术和FPGA 实现直接数字频率合成器DDS 的设计。

的设计。

设计要求:设计要求:1、 利用QuartusII 软件实验箱实现DDS 的设计;的设计;2、 通过实验箱上的开关输入DDS 的频率和相位控制字,的频率和相位控制字,并能用示波器观并能用示波器观察加以验证;察加以验证;3、 系统具有清零和使能的功能;系统具有清零和使能的功能;4、DDS 中的波形存储器模块用Altera 公司的Cyclone 系列FPGA 芯片中的ROM 实现。

实现。

二、 总体框图N 位Mf图1 DDS 总体框图总体框图低通滤波器品累加器品频率控制字相位寄存器加法器品相位控制字品正弦查找表品数模转换器品时钟源品1、 模块的功能模块的功能(1) 频率预置和调节电路频率预置和调节电路不变量不变量K 称作相位增量,也叫频率控制字。

此模块实现频率控制量的输入。

入。

(2) 相位累加器相位累加器相位累加器是一个带有累加功能的N 位加法器,它以设定的N 位频率控制字K 作为步长进行线性累加,当其和满时,计数器清零,并进行重新运算,它使输出频率正比于时钟频率和相位增量之积。

它使输出频率正比于时钟频率和相位增量之积。

(3) 相位寄存器相位寄存器 相位寄存器是一个相位寄存器是一个N 位的寄存器,它对输入端输入的数据进行寄存,当下一个时钟到来时,输出寄存的数据。

下一个时钟到来时,输出寄存的数据。

相位相位 频率控频率控频率控f 量化量化制字K 序列序列 N 位 N 位N 位图图2 2 相位累加器相位累加器相位累加器相位累加器的组成相位累加器的组成相位累加器的组成=N =N 位加法器位加法器+N +N 位寄存器位寄存器相位累加器的作用:在时钟的作用下,进行相位累加相位累加器的作用:在时钟的作用下,进行相位累加注意:当相位累加器累加满量时就会产生一次溢出,完成一个周期当相位累加器累加满量时就会产生一次溢出,完成一个周期 的动作。

DDS信号发生器实验报告

DDS信号发生器一、实验目的:学习利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。

二、实验原理实验原理参考教材6.4节和6.11节相关内容。

三、实验内容1、实验原理参考教材6.4节相关内容。

根据6.4.2节和例6-10,在Quartus II上完成简易正弦信号发生器设计,进行编辑、编译、综合、适配、仿真;2、使用SignalTap II测试;3、硬件测试:进行引脚锁定及硬件测试。

信号输出的D/A使用DAC0832,注意其转换速率是1μs。

下载到实验系统上,接上D/A模块,用示波器测试输出波形;4、按照教材图6-72完成DDS信号发生器设计,进行编辑、编译、综合、适配、仿真,引脚锁定及硬件测试。

5、建立.mif格式文件。

四、实验步骤1、建立.mif文件:(1)设定全局参数:(2)设定波形:(3)文件保存:2、新建工程:3、LPM—ROM定制:(1)(2)(3)(4)(5)(6)(7)sinrom源程序:module SIN_CNT(RST,CLK,EN,Q,AR); output [7:0] Q;input [6:0] AR;input EN,CLK,RST;wire [6:0] TMP;reg[6:0] Q1;reg[7:0] F;reg C;always @(posedge CLK)if(F<AR) F<=F+1;elsebeginF=8'b00;C=~C;endalways @(posedge CLK or negedge RST)if(!RST) Q1<=7'b0000000;else if(EN) Q1<=Q1+1;else Q1<=Q1;assign TMP=Q1;sinrom IC1(.address(TMP),.clock(CLK),.q(Q)); endmodule4、锁相环:5、顶层文件:6、SignalTap II的使用7、锁定引脚8、下载。

DDS信号发生器设计和实现

DDS信号发生器设计和实现一、引言DDS(Direct Digital Synthesis)是一种基于数字信号处理技术的信号发生器设计方法。

DDS信号发生器是通过数字的方式直接生成模拟信号,相比传统的方法,具有频率稳定、调制灵活、抗干扰能力强等优势,广泛应用于频率合成、通信系统测试、医疗设备、雷达系统等领域。

本文将介绍DDS信号发生器的设计和实现。

二、DDS信号发生器的原理1.相位累加器:负责生成一个连续增加的相位角,通常以一个固定精度的二进制数表示。

2.频率控制器:用于控制相位累加器的相位角速度,从而控制信号的频率。

3.数字到模拟转换器:将相位累加器的输出转换为模拟信号。

4.系统时钟:提供时钟信号给相位累加器和频率控制器。

三、DDS信号发生器的设计步骤1.确定要生成的信号的频率范围和精度需求。

2. 选择适合的数字信号处理器或FPGA进行设计。

常用的DSP芯片有AD9910、AD9858等,FPGA则可选择Xilinx、Altera等厂商的产品。

3.根据需求设计相位累加器和频率控制器,相位累加器的位数和频率控制器的速度决定了信号的精度。

4.确定数字到模拟转换器的采样率和分辨率,选择合适的D/A转换芯片。

5. 编写控制程序和信号生成算法,包括相位累加器和频率控制器的控制。

可以使用C语言、Verilog HDL等进行编程。

6.进行硬件的布局和连线,将各个组件按照设计要求进行连接。

7.进行电源和接地的设计,确保稳定的供电和减少噪声干扰。

8.进行数字信号处理器或FPGA的编程,烧录控制程序。

9.进行信号输出测试,调整参数和算法,确保生成的信号符合要求。

10.编写使用说明书和性能测试报告,并对信号发生器进行完整性和可靠性测试。

四、DDS信号发生器的实现案例以实现一个简单的正弦信号发生器为例,介绍DDS信号发生器的实现过程。

1.确定生成的正弦信号范围为1Hz~10kHz,精度为0.1Hz。

2. 选择Xilinx的FPGA芯片,根据需要设计12位的相位累加器和24位的频率控制器。

DDS信号发生器原理

相位累加器(N比特)正弦查询表(ROM)数模转换(DAC)低通滤波器(LPF)时钟(fc )频率(f0)控制字(M)输出2 基本原理2.1 直接数字频率合成器直接数字合成(Direct Digital Synthesis,简称DDS)技术是从相位概念出发,直接对参考正弦信号进行抽样,得到不同的相位,通过数字计算技术产生对应的电压幅度,最后滤波平滑输出所需频率。

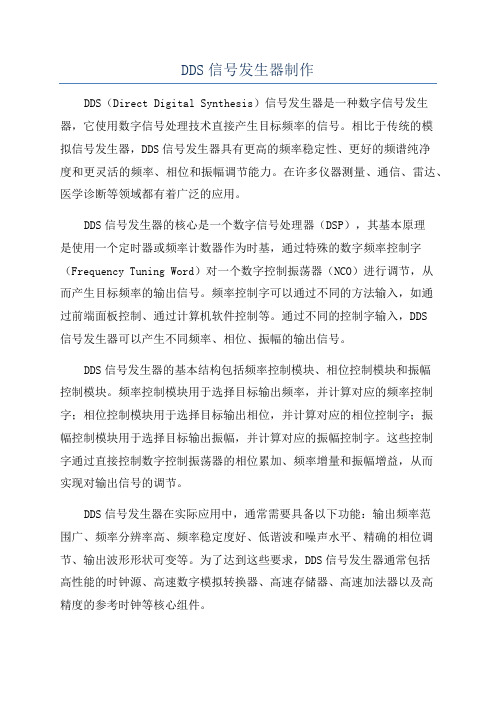

2.1.1 DDS工作原理下面,通过从相位出发的正弦函数产生描述DDS的概念。

图1表示了半径R为1的单位圆,半径R绕圆心旋转与X轴的正方向形成夹角θ(t),即相位角。

图1 单位圆表示正弦函数S= R sinθ(t)DDS的原理框图如图2所示。

图中相位累加器可在每一个时钟周期来临时将频率控制字(FTW)所决定的相位增量M累加一次,如果记数大于2N,则自动溢出,而只保留后面的N位数字于累加器中[9]。

图2 DDS原理框图DDS的数学模型可归结为:在每一个时钟周期Tc内,频率控制字M与N比特相位累加器累加一次,并同时对2N取模运算,得到的和(以N位二进制数表示)作为相位值,以二进制代码的形式去查询正弦函数表ROM,将相位信息转变成相应的数字量化正弦幅度值,ROM输出的数字正弦波序列再经数模转换器转变为阶梯模拟信号,最后通过低通滤波器平滑后得到一个纯净的正弦模拟信号。

由于ROM表的规模有限,相位累加器一般仅取高位作为寻址地址送入正弦查询表获得波形幅度值。

正弦查询表中以二进制数形式存入用系统时钟对正弦信号进行采样所得的样值点,可见只需改变查询表内容就可实现不同的波形输出。

2.1.2 DDS的结构DDS的基本结构包括相位累加器、正弦查询表(ROM)、数模转换器(DAC)和低通滤波器(LPF),其中从频率控制字到波形查询表实现由数字频率值输入生成相应频率的数字波形,其工作过程为:⑴确定频率控制字M;⑵在时钟脉冲fc的控制下,该频率控制字累加至相位累加器生成实时数字相位值;⑶将相位值寻址ROM转换成正弦表中相应的数字幅码。

DDS信号发生器制作

DDS信号发生器制作DDS(Direct Digital Synthesis)信号发生器是一种数字信号发生器,它使用数字信号处理技术直接产生目标频率的信号。

相比于传统的模拟信号发生器,DDS信号发生器具有更高的频率稳定性、更好的频谱纯净度和更灵活的频率、相位和振幅调节能力。

在许多仪器测量、通信、雷达、医学诊断等领域都有着广泛的应用。

DDS信号发生器的核心是一个数字信号处理器(DSP),其基本原理是使用一个定时器或频率计数器作为时基,通过特殊的数字频率控制字(Frequency Tuning Word)对一个数字控制振荡器(NCO)进行调节,从而产生目标频率的输出信号。

频率控制字可以通过不同的方法输入,如通过前端面板控制、通过计算机软件控制等。

通过不同的控制字输入,DDS信号发生器可以产生不同频率、相位、振幅的输出信号。

DDS信号发生器的基本结构包括频率控制模块、相位控制模块和振幅控制模块。

频率控制模块用于选择目标输出频率,并计算对应的频率控制字;相位控制模块用于选择目标输出相位,并计算对应的相位控制字;振幅控制模块用于选择目标输出振幅,并计算对应的振幅控制字。

这些控制字通过直接控制数字控制振荡器的相位累加、频率增量和振幅增益,从而实现对输出信号的调节。

DDS信号发生器在实际应用中,通常需要具备以下功能:输出频率范围广、频率分辨率高、频率稳定度好、低谐波和噪声水平、精确的相位调节、输出波形形状可变等。

为了达到这些要求,DDS信号发生器通常包括高性能的时钟源、高速数字模拟转换器、高速存储器、高速加法器以及高精度的参考时钟等核心组件。

1.硬件设计:包括选取合适的数字信号处理器和外围电路、设计时钟源和频率控制模块、选择和设计高速数字模拟转换器等。

2.软件设计:包括编写数字信号处理器的程序,实现频率、相位和振幅的控制、设置输出波形的形状和参数等功能。

3.系统调试:包括硬件的电路调试和软件的程序调试,确保整个DDS 信号发生器的运行稳定和输出信号的准确性。

FPGA基于DDS的移相调频调幅信号发生器

《EDA》课程设计报告实验题目:基于DDS的数字移相信号发生器基于DDS的数字移相信号发生器一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、信号发生器的原始数据存储在外部存储器里,由FPGA进行读取,经过D/A转换输出,由示波器观察最终结果。

三、基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

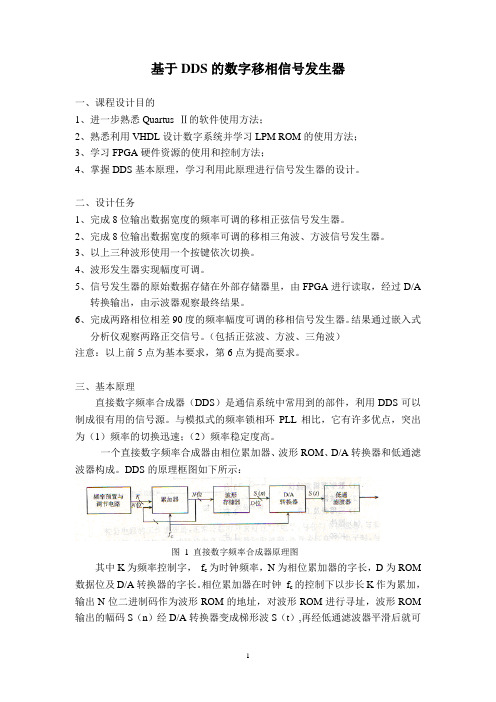

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图 1 直接数字频率合成器原理图其中K为频率控制字, fc为时钟频率,N为相位累加器的字长,D为ROM数据位及D/A 转换器的字长。

相位累加器在时钟 fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= fc K/2n,f0为输出频率,fc 为时钟频率。

当K=1时,DDS输出最低频率(也既频率分辩率)为fc /2nDDS的最大输出频率由 Nyguist 采样定理决定,即fc /2,也就是说K的最大值为2n-1.因此,只要N足够大,DDS可以得到很细的频率间隔。

EDA课程设计任务书-基于DDS的数字移相信号发生器

基于DDS的数字移相信号发生器一、课程设计目的1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、信号发生器的原始数据存储在外部存储器里,由FPGA进行读取,经过D/A转换输出,由示波器观察最终结果。

6、完成两路相位相差90度的频率幅度可调的移相信号发生器。

结果通过嵌入式分析仪观察两路正交信号。

(包括正弦波、方波、三角波)注意:以上前5点为基本要求,第6点为提高要求。

三、基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图1 直接数字频率合成器原理图其中K为频率控制字,f c为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。

相位累加器在时钟f c的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM 输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= f c K/2n,f0为输出频率,f c为时钟频率。