集成电路工艺流程

半导体集成电路工艺流程

半导体集成电路工艺流程

一、wafer切割

wafer切割是半导体集成电路(IC)生产过程中的第一步,也是半导体片材料的重要环节,它是把单晶和多晶片成型成多种尺寸的半导体片的重要工艺。

经过精密加工,工艺流程从一块单晶或多晶片,变形成多根小片,均匀分开,并实现精密切削,形成一定大小的半导体片材,用于后续的处理和加工。

此外,wafer切割还可以保证切割表面的质量和光洁度,减少片材表面的细孔和针孔,减少电路间的干扰和杂讯,提高电路的可靠性。

二、Lithography

Lithography是半导体IC晶圆工艺流程中的第二步,也是半导体片材料制造的重要环节。

它是利用光刻机在半导体片上按照设计绘制图案,利用光刻技术实现图案和电路的微米级加工的工艺。

Lithography在半导体工艺流程中,相当于画笔,利用不同的光刻设备,以不同的分辨率,把原始工艺设计按照比例缩小,然后在光刻机的放射束范围内,直接绘出晶圆上的基本芯片。

通常,在Lithography步骤中,光刻机会在未经曝光的晶圆上,使用蒙特卡洛照片精确测量曝光量,保证批处理的曝光精度,然后,使用激光对晶圆表面进行曝光,形成电路设计图案,从而实现芯片逻辑反馈。

三、Dicing

Dicing是晶圆工艺流程的第三步。

集成电路典型工艺流程

集成电路典型工艺流程(1)晶圆晶圆(Wafer)的生产由二氧化硅开始,经电弧炉提炼还原成冶炼级的硅,再经盐酸氯化,产生三氯化硅,经蒸馏纯化后,通过慢速分解过程,制成棒状或粒状的“多晶硅”。

一般晶圆制造厂,将多晶硅熔化后,再利用“籽晶”慢慢拉出单晶硅棒。

经研磨、拋光、切片后,即成为集成电路芯片生产的原料—晶圆片。

(2)光刻光刻是在光刻胶上经过曝光和显影的工序,把掩模版上的图形转换到光刻胶下面的薄膜层或硅晶上。

光刻主要包含了匀胶、烘烤、光罩对准、曝光和显影等工序。

由于光学上的需要,这段工序的照明采用偏黄色的可见光,因此俗称此区域为黄光区。

(3)干法刻蚀在半导体工艺中,刻蚀被用来将某种材质自晶圆表面上除去。

干法刻蚀是目前最常用的刻蚀方式,以气体作为主要的刻蚀媒介,并凭借等离子体能量来驱动反应。

(4)化学气相淀积(Chemical Vapor Deposition,CVD)化学气相淀积是制造微电子器件时用来淀积出某种薄膜(film)的技术,所淀积出的薄膜可能是介电材料(绝缘体,dielectrics)、导体或半导体。

(5)物理气相淀积(Physical Vapor Deposition,PVD)物理气相淀积主要包括蒸发和溅射。

如其名称所示,物理气相淀积主要是一种物理变化的工艺而非化学工艺。

这种技术一般使用氩气等惰性气体,凭借在高真空中將氩离子加速以撞击靶材后,可将靶材原子一个个溅射出来,并使被溅射出来的材质(通常为铝、钛或其合金)淀积在晶圆表面。

反应室內部的高温与高真空环境,可使这些金属原子结成晶粒,再通过光刻与刻蚀,来得到所要的导电电路。

(6)氧化利用热氧化法生长一层二氧化硅薄膜,目的是为了降低后续淀积氮化硅薄膜时产生的应力(stress),氮化硅具有很强的应力,会影响晶圆表面的结构,因此在这一层氮化硅及硅晶圆之间,生长一层二氧化硅薄膜来减缓氮化硅与规晶圆间的应力。

(7)离子注入离子注入工艺可将掺杂物质以离子形式注入半导体元件的特定区域上,以获得精确的电特性。

集成电路制造工艺流程

集成电路制造工艺流程集成电路是指将几个或者几十个电子器件(例如晶体管、电阻器、电容器等)以薄膜结构整合在一块小小的硅晶片上,并连接成电子功能电路。

其制造工艺流程是一个复杂而精密的过程,下面将对其进行详细介绍。

首先,整个工艺流程可以分为前端工艺和后端工艺两个主要阶段。

前端工艺是指IC芯片中最基本的晶体管、电阻器等器件的制作,而后端工艺则是将这些器件通过金属线材和电介质材料连接起来,形成电子功能电路。

在前端工艺阶段,首先需要准备好硅晶片。

硅晶片通过切割和抛光等工艺进行精细处理,形成平整的硅表面。

然后,通过光刻工艺将掩模上的图形投射到硅表面,形成各种不同的器件结构。

接下来,通过注入掺杂剂和热退火工艺来调节硅晶片的电特性,从而形成晶体管等元器件。

在后端工艺阶段,首先需要在硅晶片上进行电路层间绝缘处理,即通过沉积电介质材料形成绝缘层,以防止电气短路。

接下来,通过刻蚀和蚀刻等工艺将电介质材料开口,并注入金属线材,形成连接器件的导线结构。

随后,通过电镀工艺给金属线材镀上一层保护层,以保护导线不受外界环境的影响。

除了这些基本的工艺步骤外,集成电路制造还需要进行许多附加工艺,如薄膜制备、掩膜、清洗等。

其中,薄膜制备是指通过物理蒸发、溅射等工艺在硅表面形成一层非常薄的材料,用于改变器件的表面特性。

掩膜则是通过光刻工艺在硅表面形成一层光刻胶,以便进行后续的刻蚀工艺。

清洗则是在集成电路制造过程中,通过溶液等方法将硅表面的杂质去除,以保证器件的电特性。

在整个制造工艺的过程中,需要严格控制各个工艺步骤的条件和参数,以确保最终制得的集成电路具有良好的性能和稳定性。

诸如工艺参数、工艺流程等的微小变化都可能影响到整个工艺的成功与否。

综上所述,集成电路的制造工艺流程是一个复杂而精密的过程,涉及到多个工艺步骤和参数的控制。

通过前端工艺和后端工艺的协同作用,可以将晶体管、电阻器等元器件整合在一片硅晶片上,并形成电子功能电路。

这些制备出的集成电路,被广泛应用于计算机、通信、嵌入式等各个领域,推动了现代科技的发展。

集成电路工艺流程

集成电路工艺流程1 光刻工艺流程1.1 光刻前准备光刻前准备主要包括三个部分:模板准备、洗片准备、光刻胶准备,以下介绍各个部分的准备:(1)模板准备:在确定好电路设计的图纸后,首先把图纸给光刻模板工序,由工艺师对给定的模板进行适当的调整,确保模板上的每个线宽精度与电路图纸相符。

(2)洗片准备:这一步是洗片电路前的准备工序,根据集成电路的不同,有不同的洗片流程,为保证集成电路后续工步的品质,在洗片的物理性能上要有较高的要求,在溶液的洗片中,要求洗片工艺到位,洗片时间要精确,洗片液不能有杂质,质量要稳定,特别是洗片液和洗片时间的选择要适当。

(3)光刻胶准备:光刻胶涉及到光刻料及曝光系统,特别是光刻料要求高,不同型号的光刻料的性能差异较大,所以要求采用正确型号的光刻料,选择性能稳定的光刻料。

1.2 光刻工艺流程(1)模板清洗:模板清洗主要是指洗涤模板,模板清洗时要选择合适的清洗剂,并用规定的时间进行清洗,以保证模板的清洁度,并及时进行润滑,以保证模板的耐用度,防止模板划伤。

(2)洗片:洗片分为新片洗片和再洗片,新片洗片要注意去除隐藏性杂质,并将原料珊瑚片清洗干净。

再洗片时要求去除上一步残留的杂质和外界污染物,保证集成电路元件的耐用性,再洗片也可以用来清洗模板。

(3)蒸汽消毒:蒸汽消毒要求使用洁净蒸汽,以防止杂质和微生物污染,确保集成电路的质量。

(4)光刻制程:光刻制程要求在图案和图形绘制操作之前,要经过模板检测,以保证模板的质量,其次要核对图纸和模板,并进行曝光时间设定,最后要进行曝光机操作,以及检查曝光图案的质量,确保曝光结果的完美。

(5)洗涤:洗涤是指精确洗涤光刻后的集成电路图案,可以去除曝光过程中残留的光刻胶,确保电路图案的光洁度和精细度。

此外,还可以使用高级的洗涤工艺,如超声波洗涤、活性弱酸洗涤、高纯水洗涤等,以满足特殊的应用要求。

集成电路制造工艺流程介绍

集成电路制造工艺流程介绍1. 晶圆生长:制造过程的第一步是晶圆生长。

晶圆通常是由硅材料制成,通过化学气相沉积(CVD)或单晶硅引入熔融法来生长。

2. 晶圆清洗:晶圆表面需要进行清洗,以去除可能存在的污染物和杂质,以确保后续工艺步骤的成功进行。

3. 光刻:光刻是制造过程中非常关键的一步。

在光刻过程中,先将一层光刻胶涂覆在晶圆表面,然后使用光刻机将芯片的设计图案投影在晶圆上。

接着,进行光刻胶显影,将未受光的部分去除,留下所需的图案。

4. 沉积:接下来是沉积步骤,通过CVD或物理气相沉积(PVD)将金属、氧化物或多晶硅等材料沉积在晶圆表面上,以形成导线、电极或其他部件。

5. 刻蚀:对沉积的材料进行刻蚀,将不需要的部分去除,只留下所需的图案。

6. 接触孔开孔:在晶圆上钻孔,形成电极和导线之间的接触孔,以便进行电连接。

7. 清洗和检验:最后,对晶圆进行再次清洗,以去除可能残留的污染物。

同时进行严格的检验和测试,确保芯片质量符合要求。

以上是一个典型的集成电路制造工艺流程的简要介绍,实际的制造过程可能还包括许多其他细节和步骤,但总的来说,集成电路制造是一个综合了多种工艺和技术的高精度制造过程。

集成电路(Integrated Circuit,IC)制造是一项非常复杂的工艺,涉及到材料科学、化学、物理、工程学和电子学等多个领域的知识。

在这个过程中,每一个步骤都至关重要,任何一个环节出错都可能导致整个芯片的质量不达标甚至无法正常工作。

以下将深入介绍集成电路的制造工艺流程及相关的技术细节。

8. 电镀:在一些特定的工艺步骤中,需要使用电镀技术来给芯片的表面涂覆一层导电材料,如金、铜或锡等。

这些导电层对于芯片的整体性能和稳定性非常重要。

9. 封装:制造芯片后,需要封装芯片,以保护芯片不受外部环境的影响。

封装通常包括把芯片封装在塑料、陶瓷或金属外壳内,并且接上金线用以连接外部电路。

10. 测试:芯片制造完成后,需要进行严格的测试。

集成电路制造工艺

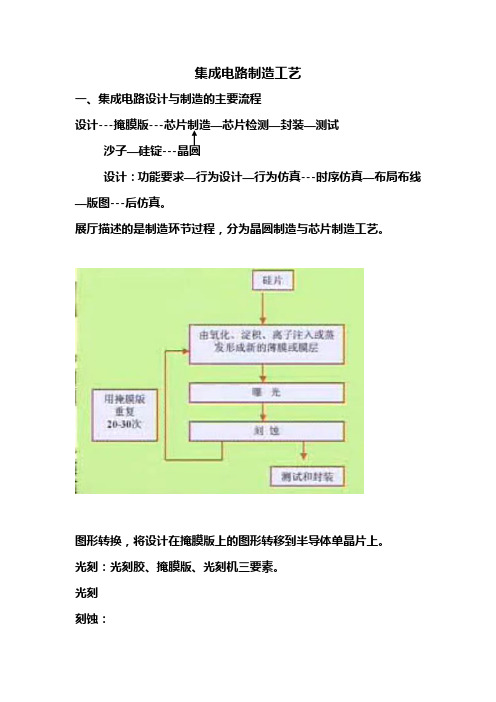

集成电路制造工艺一、集成电路设计与制造的主要流程设计---掩膜版---芯片制造—芯片检测—封装—测试沙子—硅锭---晶圆设计:功能要求—行为设计—行为仿真---时序仿真—布局布线—版图---后仿真。

展厅描述的是制造环节过程,分为晶圆制造与芯片制造工艺。

图形转换,将设计在掩膜版上的图形转移到半导体单晶片上。

光刻:光刻胶、掩膜版、光刻机三要素。

光刻刻蚀:参杂,根据设计需要,将各种杂质掺杂在需要的位置上,形成晶体管接触等制作各种材料的薄膜二、晶圆制造1. 沙子:硅是地壳内第二丰富的元素,脱氧后的沙子(尤其是石英)最多包含25%的硅元素,主要以二氧化硅(SiO2)的形式存在。

2. 硅熔炼:通过多步净化得到可用于半导体制造质量的硅,学名电子级硅(EGS),平均每一百万个硅原子中最多只有一个杂质原子。

(本文指12英寸/300毫米晶圆级,下同。

)3.单晶硅锭:整体基本呈圆柱形,重约100千克,硅纯度99.9999%。

4. 硅锭切割:横向切割成圆形的单个硅片,也就是我们常说的晶圆(Wafer)。

5. 晶圆:切割出的晶圆经过抛光后变得几乎完美无瑕,表面甚至可以当镜子。

Intel自己并不生产这种晶圆,而是从第三方半导体企业那里直接购买成品,然后利用自己的生产线进一步加工,比如现在主流的45nm HKMG(高K金属栅极)。

Intel公司创立之初使用的晶圆尺寸只有2英寸/50毫米。

三、芯片制造过程6. 光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过程中浇上去的光刻胶液体,类似制作传统胶片的那种。

晶圆旋转可以让光刻胶铺的非常薄、非常平。

光刻一:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得可溶,期间发生的化学反应类似按下机械相机快门那一刻胶片的变化。

掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上,就会形成微处理器的每一层电路图案。

一般来说,在晶圆上得到的电路图案是掩模上图案的四分之一。

集成电路加工工艺流程

集成电路加工工艺流程一、引言集成电路(Integrated Circuit,简称IC)是现代电子技术的基础,广泛应用于计算机、通信、消费电子等领域。

其中,集成电路的加工工艺流程对于最终产品的性能和品质至关重要。

本文将深入探讨集成电路加工工艺流程,包括制备晶圆、光刻技术、沉积过程、蚀刻过程等内容。

二、制备晶圆2.1 材料选择集成电路加工的第一步是选择合适的晶圆材料。

常用的晶圆材料包括硅、砷化镓、氮化镓等。

根据不同应用的需求,选择适当的晶圆材料非常重要。

2.2 晶圆生长晶圆生长是制备晶圆的关键过程。

通过熔化材料并缓慢冷却,可以获得高质量的单晶材料。

晶圆的直径通常为4英寸、6英寸、8英寸等。

2.3 晶圆切割晶圆切割是将生长好的大块单晶材料切割成薄片的过程。

切割后的晶圆表面需要进行抛光处理,以获得光滑的表面。

三、光刻技术光刻技术是集成电路制造中最常用的工艺之一,用于制作电路图案。

下面介绍光刻技术的主要步骤:3.1 涂覆光刻胶首先,在晶圆表面涂覆一层光刻胶。

光刻胶起到隔离和保护的作用,能够防止后续步骤中化学溶液侵蚀晶圆表面。

3.2 制作掩膜根据设计需要,制作相应的掩膜。

掩膜是光刻胶中需要透过的区域,用于形成电路图案。

3.3 曝光将掩膜对准晶圆,通过紫外线照射,使光刻胶中的敏化剂发生化学反应。

掩膜中的透明区域会使光刻胶发生改变,而不透明区域则保持不变。

3.4 显影在曝光后,使用显影液将未曝光区域的光刻胶溶解掉,形成电路图案。

显影后的晶圆需要经过清洗和干燥等处理。

四、沉积过程沉积是在晶圆上加上薄膜层的过程。

薄膜的材料和厚度根据实际需求而定。

4.1 化学气相沉积(CVD)化学气相沉积是一种常用的沉积方法。

通过在加热的晶圆上将气体分子分解并沉积在表面上,形成一层均匀的薄膜。

4.2 物理气相沉积(PVD)物理气相沉积是另一种常用的沉积方法。

使用高能粒子轰击靶材,将靶材上的原子或分子沉积在晶圆表面。

4.3 电化学沉积电化学沉积是利用电流驱动金属离子沉积在晶圆上的方法。

集成电路制造工艺流程

集成电路制造工艺流程引言:集成电路(IC)作为现代电子技术的核心,被广泛应用于计算机、通信、消费电子等领域。

集成电路制造工艺是将原始材料经过一系列加工步骤,将电路图案和其他组件集成到单片硅芯片上的过程。

本文将详细介绍集成电路制造的工艺流程。

一、晶圆制备1.材料准备:通常采用硅作为晶圆基底材料。

硅材料需经过多次高温处理来去除杂质。

2.切割:将硅原料切割成圆片形状,厚度约为0.4毫米。

3.晶圆清洗:通过化学和物理方法清洗硅片表面。

二、晶圆表面处理1.清洗:使用化学物质去除晶圆表面的有机和无机污染物。

2.二氧化硅沉积:在晶圆表面形成一层绝缘层,以保护电路。

3.光刻:通过对光敏材料进行曝光、显影和刻蚀等步骤,将电路图案转移到晶圆表面。

三、激活剂注入1.清洗:清洗晶圆表面以去除光刻过程产生的残留物。

2.掺杂:使用离子注入设备将所需的杂质注入晶圆表面,以改变材料的导电性。

四、金属化1.金属沉积:在晶圆上沉积一层金属,通常是铝或铜,以用作导电线。

2.蚀刻:使用化学溶液去除多余的金属,只保留所需的电路。

3.封装:将晶圆裁剪成多个小片,然后分别进行封装,以提供保护和连接接口。

五、测试1.功能测试:确保电路功能正常。

2.可靠性测试:对电路进行长时间运行测试,以验证其性能和可靠性。

3.封装测试:测试封装后的芯片性能是否正常。

六、成品测试和封装1.最终测试:对芯片进行全面测试,以确保其达到预期的性能指标。

2.封装:在芯片表面添加保护层,并提供引脚用于连接到其他电子设备。

结论:本文详细介绍了集成电路制造的工艺流程,包括晶圆制备、晶圆表面处理、激活剂注入、金属化、测试和封装等环节。

每一步都是为了保证集成电路的性能和可靠性。

随着科技的不断发展,集成电路制造工艺也在不断创新,以提高集成电路的性能和功能。

集成电路制造工艺流程

*

磷穿透扩散:减小串联电阻 离子注入:精确控制参杂浓度和结深

B

P-Sub

N+埋层

SiO2

光刻胶

P+

P+

P+

P

P

N+

P-Sub

1.2.2 N阱硅栅CMOS工艺主要流程 2. 氧化、光刻N-阱(nwell)

*

1.2.2 N阱硅栅CMOS工艺主要流程 3. N-阱注入,N-阱推进,退火,清洁表面

P-Sub

N阱

*

1.2.2 N阱硅栅CMOS工艺主要流程 4.长薄氧、长氮化硅、光刻场区(active反版)

N阱

P-Sub

*

集成电路(Integrated Circuit) 制造工艺是集成电路实现的手段,也是集成电路设计的基础。

单击添加副标题

第一章 集成电路制造工艺流程

*

无生产线集成电路设计技术

引言

随着集成电路发展的过程,其发展的总趋势是革新工艺、提高集成度和速度。 设计工作由有生产线集成电路设计到无生产线集成电路设计的发展过程。 无生产线(Fabless)集成电路设计公司。如美国有200多家、台湾有100多家这样的设计公司。

*

P-Sub

1.2.2 N阱硅栅CMOS工艺主要流程 13. 钝化层淀积,平整化,光刻钝化窗孔(pad)

*

N阱

有源区

多晶

Pplus

Nplus

接触孔

金属1

通孔

金属2

PAD

1.2.3 N阱硅栅CMOS工艺 光刻掩膜版汇总简图

*

2. 减缓表面台阶

3. 减小表面漏电流

P-Sub

N-阱

集成电路的制作工艺与流程

集成电路的制作工艺与流程

1. 晶圆制备:晶圆是集成电路的基础材料,一般采用硅(Silicon)材料制作。

晶圆的制备工艺包括晶体生长、切割和

抛光等步骤。

2. 晶圆清洗:晶圆清洗是为了去除晶圆表面的污染物,保证后续工艺步骤的顺利进行。

3. 沉积:沉积是指在晶圆表面上沉积一层薄膜,常用的沉积方法包括物理气相沉积(Physical Vapor Deposition, PVD)和化

学气相沉积(Chemical Vapor Deposition, CVD)等。

4. 光刻:光刻是将设计好的电路图案转移到晶圆表面的工艺步骤。

首先在薄膜表面涂覆一层光刻胶,然后使用光学投影机将电路图案投影在光刻胶上。

最后通过显影和蚀刻等步骤,在光刻胶上形成所需的电路图案。

5. 清洗:清洗是为了去除光刻胶和表面污染物,保证后续工艺步骤的顺利进行。

6. 金属化:金属化是在晶圆表面上沉积一层金属,常用的金属有铝(Aluminum)等。

金属化的目的是连接不同部分的电路,形成完整的电路连接网络。

7. 划线:划线是将金属化层上的金属切割成所需的电路连线。

8. 封装测试:最后一步是将制作好的芯片进行封装和测试。

封

装是将芯片封装在塑料、陶瓷或金属等材料中,以保护芯片和实现引脚的外接。

测试是通过一系列测试方法和设备来验证芯片的功能和可靠性。

以上是集成电路的制作工艺与流程的基本步骤,不同类型的集成电路可能会有些差异,但整体的工艺流程大致相同。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路中双极性和CMOS工艺流程

摘要:本文首先介绍了集成电路的发展,对集成电路制作过程中的主要操作进行了简要

讲述。

双极性电路和MOS电路时集成电路发展的基础,双极型集成电路器件具有速度高、驱动能力强、模拟精度高的特点,但是随着集成电路发展到系统级的集成,其规模越来越大,却要求电路的功耗减少,而双极型器件在功耗和集成度方面无法满足这些方面的要求。

CMOS电路具有功耗低、集成度高和抗干扰能力强的特点。

文章主要介绍了双极性电路和CMOS电路的主要工艺流程,最后对集成电路发展过程中出现的新技术新工艺以及一些阻

碍集成电路发展的因素做了阐述。

关键词:集成电路,双极性工艺,CMOS工艺

ABSTRACT This paper first introduces the development of integrated circuits, mainly operating in the process of production for integrated circuits were briefly reviewed. Bipolar and MOS circuit Sas the basis for the development of integrated circuit. Bipolar integrated circuits with high speed, driving ability, simulated the characteristics of high precision, but with the development of integrated circuit to the system level integration, its scale is more and more big.So, reducing the power consumption of the circuit is in need, but bipolar devices in power consumption and integration can't meet these requirements. CMOS circuit with low power consumption, high integration and the characteristics of strong anti-interference ability. This paper mainly introduces the bipolar circuit and CMOS circuit the main technological process.finally, the integrated circuit appeared in the process of development of new technology and new technology as well as some factors hindering the development of the integrated circuit are done in this paper.

KEY WORDS integrated circuit, Bipolar process, CMOS process

引言

集成电路(IC)是把多个器件(如晶体管、电阻、电容等)及其间的连线同时制作在一个芯片上,形成的一块独立的、具有一定功能的整体电路。

从1947年12月美国贝尔实验室的巴丁和布拉顿制作出第一只点接触的半导体晶体管至今只有40多年的历史,但其发展速度十分迅速,现在已经应用于我们生活的方方面面,国家的建设和国防更是离不,开集成电路。

集成电路的出现使电子设备向着微型化、高速度、低功耗和智能化发展,加快了人类进入信息时代的步伐。

双极型集成电路器件具有速度高、驱动能力强、模拟精度高的特点,在集成电路发展初期得到了广泛应用,双极性工艺是集成电路制作的基础,因此掌握基本的双极性工艺流程的制作过程是掌握集成电路工艺过程的基础。

但是随着集成电路发展到系统级的集成,其规模越来越大,却要求电路的功耗减少,而双极型器件在功耗和集成度方面无法满足这些方面的要求。

CMOS电路具有功耗低、集成度高和抗干扰能力强的特点。

因此CMOS在现在的集成电路中被广泛应用,掌握基本的CMOS的工艺流程也是集成电路学习设计与制作过程中所必须的。

下面首先对集成电路制作过程作简要讲述,然后对双极性工艺和CMOS工艺进行主要讲解。

最后对集成电路发展过程中出现的新技术以及阻碍集成电路发展的一些因素做了概述。

一、集成电路简介

Intel 公司的创始人摩尔在1956年预测了集成电路发展趋势,指出集成度随时间指数增长的规律。

1975年又进一步预测了未来的发展,指出集成度每18个月翻一番的增长规律。

集成电路迅速发展的原因主要是:1、特征尺寸不断缩小,大约每三年缩小2倍。

2、芯片面积不断增大,大约每三年增大1.5倍。

3、器件和电路结构不断改进。

集成电路器件制作过程中的主要操作有三种(1)、形成某种材料的薄膜:在集成电路的制作过程中要形成二氧化硅膜、多晶硅膜、氮化硅膜、一些金属的硅化物膜以及作为连线的金属膜,等等。

形成这些薄膜的方法主要是化学汽相沉积(Chemical Vapor Deposition, 简称CVD)或物理汽相沉积(Physical Vapor Deposition, 简称PVD)。

CVD:气态反应原料在固态基体表面反应并淀积成薄膜。

PVD:真空条件下,用蒸发、溅射、离子轰击等方法产生原子或原子团,并最终使材料淀积在基片上。

(2)、在各种薄膜材料上形成需要的图形:图形的加工是通过光刻和刻蚀来完成的。

光刻和刻蚀的作用就是把设计好的集成电路版图上的图形复制到硅片上。

目前的光刻主要是光学光刻,是把掩膜板上的图形转移到硅片上。

具体包括甩胶(正胶和负胶)、曝光、显影、刻蚀、去胶五个步骤。

具体的操作过程如下:

图(1)光学光刻示意图

●甩胶—在硅片上均匀涂敷一层光刻胶

● 曝光—把涂胶的硅片放在掩膜板下,经过光照(一般为紫外光),使掩膜板上亮的区域对应的光刻胶被曝光,而掩膜板上暗的区域对应的光刻胶不能被曝光。

●显影—通过物理或化学方法把没曝光的胶(针对负胶)去掉。

显影后掩膜板上的图形就转移到光刻胶上。

●刻蚀—把没有光刻胶保护的那部分SiO2去掉。

刻蚀后掩膜板上的图形就转移到了SiO2膜上,以前采用化学溶液进行刻蚀,称为湿法刻蚀。

但因湿法刻蚀不能精确控制刻蚀速率,难以实现精细图形。

目前集成电路加工都采用干法刻蚀,如反应离子(Reaction Ion Etching,简称RIE)刻蚀。

●去胶—最后去除残留在硅片上的所有光刻胶,就得到了完成某种图形加工的硅片。

(3)通过掺杂改变材料的电阻率或类型:在集成电路的制作过程中可以通过扩。