1、VerilogHDL设计流程

VerilogHDL实验报告

VerilogHDL实验报告实验一Modelsim仿真软件的使用一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真3、方法moduleyihuo (a,b,c);inputa,b;output c;assign c=a^b;endmodule测试程序:module t_yihuo;reg a,b; wire c;initial begin a=0; forever #20 a=~a; end initial begin b=0; forever #30 b=~b; endyihuou1(a,b,c);endmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim软件,掌握了Modelsim软件的编译、仿真方法。

同时在编写程序的过程中,加深了我对课上所讲的HDL的语法的认识。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim的数字电路设计方法(2)熟练掌握HDL 程序的不同实现方法二、实验内容1、实验要求设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真。

2、方法module test(a,b,c,s);inputa,b,c;output s;assign s=c|(b&a);endmodulemodulet_test;rega,b,c;wire s;initialbegina=0;forever#10 a=~a;endinitialbeginb=0;forever #20 b=~b;endinitialbeginc=0;forever#40 c=~c;endtest u1(a,b,c,s);endmodule三、实验结果四、分析和心得通过本次实验,我掌握基于Modelsim的简单数字电路设计方法,且尝试了用不同方法实现功能,三人表决器可以通过testbench测试程序实现,也可以利用always模块实现,可见程序的设计思想是很重要的。

verilog hdl程序设计与实践

verilog hdl程序设计与实践

本书为VerilogHDL程序设计的入门教材,旨在帮助读者了解Verilog HDL的基础知识,掌握Verilog HDL的编写方法和使用技巧,以及实践中可能遇到的问题和解决方法。

本书主要包括以下内容:

1. Verilog HDL的基础知识:介绍Verilog HDL的语法、数据

类型、模块化设计等基础概念,为后续的学习和实践打下基础。

2. Verilog HDL的编写方法:详细讲解Verilog HDL的编写方法,包括模块的定义、端口的定义、内部信号的定义和使用等,以及如何利用Verilog HDL实现时序逻辑和组合逻辑。

3. Verilog HDL的使用技巧:介绍如何利用Verilog HDL实现

各种数字电路,包括门电路、时序电路、存储器等,同时讲解如何利用仿真工具进行验证和调试。

4. Verilog HDL的实践案例:通过多个实例,包括计数器、移

位寄存器、加法器等,帮助读者掌握Verilog HDL的应用技巧和实践经验。

本书适合电子信息工程、计算机科学与技术等相关专业的本科生、研究生及工程师学习和参考,也可作为相关课程的教材。

- 1 -。

veriloghdl程序大全

1.简单门电路的设计二输入与非门module nand_2(y,a,b);output y;input a,b;nand(y,a,b);endmodule二输入异或门module nand_2(y,a,b);output y;input a,b;reg y;always @(a,b)begincase({a,b})2’b00:y=1;2’b01:y=1;2’b10:y=1;2’b11:y=0;default:y=’bx;endcaseendendmodule二输入三态门module eda_santai(dout,din,en); output dout;input din,en;reg dout;alwaysif (en) dout<=din;else dout<=’bz;endmodule3-8译码器的设计module yimaqi(S1,S2,S3,A,Y); input S1;wire S1;input S2;wire S2;input S3;wire S3;input [2:0]A;wire [2:0]A;output[7:0]Y;reg [7:0]Y;reg s;always@(S,S1,S2,S3)begins<=S2|S3;Y <=8'b1111_1111;else if(S)Y <=8'b1111_1111;elsecase(A)3'b000:Y<=11111110;3'b001:Y<=11111101;3'b010:Y<=11111011;3'b011:Y<=11110111;3'b100:Y<=11101111;3'b101:Y<=11011111;3'b110:Y<=10111111;3'b111:Y<=01111111;endcaseendendmodule2.8-3编码器的设计module banjiaqi(a,b,count,sum);input a;wire a;input b;wire b;output count;wire count;output sum;wire sum;assign {count,sum}=a+b;endmodule4. D触发器的设计module Dchufaqi ( Q ,CLK ,RESET ,SET ,D ,Qn ); input CLK ;wire CLK ;input RESET ;wire RESET ;input SET ;wire SET ;input D ;wire D ;output Q ;reg Q ;output Qn ;wire Qn ;assign Qn = ~Q ;always @ ( posedge CLK or negedge SET or negedge RESET ) beginif ( !RESET)Q <= 0 ;else if ( ! SET)Q <= 1;else Q <= D;endendmodule5. 1位半加法器的设计module banjiafaqi(a,b,sum,count);input a;wire a;input b;wire b;output sum;wire sum;output count;wire count;assign {count,sum}=a+b;endmodule6. 4位计数器的设计module sihisjishuqi(CLK,RESET,out);input CLK;wire CLK;input RESET;wire RESET;output[3:0] out;reg[3:0] out;always @ ( posedge CLK or negedge RESET )beginif(!RESET)out<=4'b0000;elsebeginout<=out+1;if(out==4'b1010)out<=4'b0000;endendendmodule7.分频时序逻辑电路的设计module eda_fp_even(clk_out,clk_in,rst); input clk_in;input rst;wire rst;output clk_out;reg clk_out;reg [1:0]cnt;parameter N=6;always @(posedge clk_in or negedge rst) beginif(!rst)beginclk_out<=0;cnt<=0;endelsebegincnt<=cnt+1;if(cnt==N/2-1)beginclk_out=!clk_out;cnt<=0;endendendendmodule8.7段显示译码器的设计module eda_scan_seven(clk,dig,y,rst); input clk;wire clk;input rst;wire rst;output[7:0] dig;wire[7:0] dig;output [7:0]y;wire [7:0]y;reg clkout;reg [19:0]cnt;reg [2:0]wei;reg [3:0]duan;reg [6:0]Y_r;reg [7:0]dig_r;assign y = {1'b1,(~Y_r[6:0])};assign dig =~dig_r;parameter period= 1000000;always@(posedge clk or negedge rst) beginif(!rst)cnt<=0;else begincnt<=cnt+1;if(cnt==(period>>1)-1)clkout<=#1 1'b1;else if(cnt==period-1)beginclkout<=#1 1'b0;cnt<=#1 1'b0;endendendalways@(posedge clkout or negedge rst ) beginif(!rst)wei<=0;elsewei<=wei+1;endalways @(wei) //数码管选择begincase ( wei )3'b000 :begindig_r <= 8'b0000_0001;duan <= 1;end3'b001 :begindig_r <= 8'b0000_0010;duan<= 3;end3'b010 :begindig_r <= 8'b0000_0100;duan<= 5;end3'b011 :begindig_r <= 8'b0000_1000;duan <= 7;end3'b100 :begindig_r <= 8'b0001_0000;duan<= 9;end3'b101 :begindig_r <= 8'b0010_0000;duan<= 11;end3'b110 :begindig_r <= 8'b0100_0000;duan <= 13;end3'b111 :begindig_r <= 8'b1000_0000;duan<= 15;endendcaseendalways @ ( duan ) //译码begincase ( duan )0: Y_r = 7'b0111111; // 01: Y_r = 7'b0000110; // 12: Y_r = 7'b1011011; // 23: Y_r = 7'b1001111; // 34: Y_r = 7'b1100110; // 45: Y_r = 7'b1101101; // 56: Y_r = 7'b1111101; // 67: Y_r = 7'b0100111; // 78: Y_r = 7'b1111111; // 89: Y_r = 7'b1100111; // 910: Y_r = 7'b1110111; // A11: Y_r = 7'b1111100; // b12: Y_r = 7'b0111001; // c13: Y_r = 7'b1011110; // d14: Y_r = 7'b1111001; // E15: Y_r = 7'b1110001; // Fdefault: Y_r = 7'b0000000;endcaseendendmodule9.数据选择器的设计module eda_8xuanyi (A,D0,D1,D2,D3,D4,D5,D6,D7,G,Y); input D0,D1,D2,D3,D4,D5,D6,D7,G;input [2:0]A;wire [2:0]A;output Y;reg Y;always @(A, G)beginif (G==0)Y<=0;elsecase(A)3'b000:Y=D0;3'b001:Y=D1;3'b010:Y=D2;3'b011:Y=D3;3'b100:Y=D4;3'b101:Y=D5;3'b110:Y=D6;3'b111:Y=D7;endcaseendendmodule10.数据锁存器的设计module e da_suocunqi(q,d,oen,g); output[7:0] q;//数据输出端input[7:0] d;//数据输入端input oen,g;//三态控制端reg[7:0] q;always @(*)beginif (oen)beginq<="z";endelsebeginif(g)q<=d;elseq<=q;endendendmodule11.数据寄存器的设计module eda_jicunqi(r,clk,d,y); input r,clk;input [7:0]d;wire [7:0]d;output [7:0]y;reg [7:0]y;always @ (posedge clk or negedge r) beginif(!r)y<=8'b00000000;elsey<=d;endendmodule12.顺序脉冲发生器的设计module eda_shunxu(clk,clr,q);input clk,clr;output [7:0]q;reg [7:0]q;always @ ( posedge clk or posedge clr ) beginif ( clr==1)beginq<=8'b00000000; //赋初值endelsebeginif(q==0)q<=8'b00000001;elseq<=q<<1; //给初值进行移位endendendmodule13.1位全加法器的设计module quanjiaqi(a,b,sum,count,cin); input a;wire a;input b;wire b;input cin;wire cin;output sum;wire sum;output count;wire count;assign{sum,count}=a+b+cin; endmodule15.键控Led灯的设计module eda_led(led,key);input key;output led;reg led_out;assign led<=led_out;always@(key)beginif(key)led_out<=1;else if(!key)led_out<=0;endendmodule16.双向移位寄存器的设计module eda_yiweijicunqi( left_right ,load ,clr ,clk ,DIN ,DOUT );input left_right ;wire left_right ;input load ;wire load ;input clr ;wire clr ;input clk ;wire clk ;input [3:0] DIN ;wire [3:0] DIN ;output [3:0] DOUT ;wire [3:0] DOUT ;reg [3:0] data_r;assign DOUT = data_r ;always @ (posedge clk or posedge clr or posedge load)//敏感变量,看真值表beginif(clr==1)data_r <= 0;//判断是否清零else if (load )data_r<=DIN;//判断是否装载数据//判断进行左移位还是右移位elsebeginif(left_right)data_r<=DIN<<1;elsedata_r<=DIN>>1;endendendmodule17.8-3优先编码器的设计module youxianbianma( A ,I ,GS ,EO ,EI ); input [7:0] I ;wire [7:0] I ;input EI ;wire EI ;output [2:0] A ;reg [2:0] A ;output GS ;reg GS ;output EO ;reg EO ;always @ ( I or EI )if ( EI )beginA <= 3'b111;GS <= 1;EO <= 1;endelse if (I==8'b11111111)beginA <= 3'b111;GS <= 1;EO <= 0;endelse if ( I==8'b11111110 )beginA <= 3'b111;GS <= 0;EO <= 1;endelse if ( I==8'b1111110x )beginA <= 3'b110;GS <= 0;EO <= 1;endelse if ( I==8'b111110xx )beginA <= 3'b101;GS <= 0;EO <= 1;endelse if ( I==8'b11110xxx )beginA <= 3'b100;GS <= 0;EO <= 1;endelse if ( I==8'b1110xxxx )beginA <= 3'b011;GS <= 0;EO <= 1;endelse if ( I==8'b110xxxxx )beginA <= 3'b010;GS <= 0;EO <= 1;endelse if ( I==8'b10xxxxxx )beginA <= 3'b001;GS <= 0;EO <= 1;endelse if ( I==8'b0xxxxxxx )beginA <= 3'b000;GS <= 0;EO <= 1;endendmodule18.数据分配器的设计module shujufenpeiqi(y0,y1,y2,y3,din,a); output y0,y1,y2,y3;//4??êy?Yí¨μàinput din;//êy?Yê?è?input [1:0] a;reg y0,y1,y2,y3;always @(din,a)beginy0=0;y1=0;y2=0;y3=0; //3?ê??ˉ£á?case(a)00:y0=din;01:y1=din;02:y2=din;03:y3=din;endcase end endmodule。

华为fpga设计规范(Verilog Hdl)

FPGA设计流程指南前言本部门所承担的FPGA设计任务主要是两方面的作用:系统的原型实现和ASIC的原型验证。

编写本流程的目的是:●在于规范整个设计流程,实现开发的合理性、一致性、高效性。

●形成风格良好和完整的文档。

●实现在FPGA不同厂家之间以及从FPGA到ASIC的顺利移植。

●便于新员工快速掌握本部门FPGA的设计流程。

由于目前所用到的FPGA器件以Altera的为主,所以下面的例子也以Altera为例,工具组合为modelsim + LeonardoSpectrum/FPGACompilerII + Quartus,但原则和方法对于其他厂家和工具也是基本适用的。

目录1. 基于HDL的FPGA设计流程概述 (1)1.1 设计流程图 (1)1.2 关键步骤的实现 (2)1.2.1 功能仿真 (2)1.2.2 逻辑综合 (2)1.2.3 前仿真 (3)1.2.4 布局布线 (3)1.2.5 后仿真(时序仿真) (4)2. Verilog HDL设计 (4)2.1 编程风格(Coding Style)要求 (4)2.1.1 文件 (4)2.1.2 大小写 (5)2.1.3 标识符 (5)2.1.4 参数化设计 (5)2.1.5 空行和空格 (5)2.1.6 对齐和缩进 (5)2.1.7 注释 (5)2.1.8 参考C语言的资料 (5)2.1.9 可视化设计方法 (6)2.2 可综合设计 (6)2.3 设计目录 (6)3. 逻辑仿真 (6)3.1 测试程序(test bench) (7)3.2 使用预编译库 (7)4. 逻辑综合 (8)4.1 逻辑综合的一些原则 (8)4.1.1 关于LeonardoSpectrum (8)4.1.1 大规模设计的综合 (8)4.1.3 必须重视工具产生的警告信息 (8)4.2 调用模块的黑盒子(Black box)方法 (8)参考 (10)修订纪录 (10)1. 基于HDL的FPGA设计流程概述1.1 设计流程图说明:●逻辑仿真器主要指modelsim,Verilog-XL等。

Verilog_HDL复杂数字系统设计-2_[1]...

![Verilog_HDL复杂数字系统设计-2_[1]...](https://img.taocdn.com/s3/m/3f4f2f7ba26925c52cc5bff2.png)

2013-8-4

南通大学电子信息学院

7

1.3复杂数字系统的设计方法

1.3.1 复杂数字逻辑系统

• 嵌入式微处理机系统

• 数字信号处理系统 • 高速并行计算逻辑

• 高速通信协议电路

• 高速编码/解码、加密/解密电路 • 复杂的多功能智能接口

• 门逻辑总数超过几万门达到几百甚至达几千万门的数

字系统

2013-8-4 南通大学电子信息学院 8

1990 Verilog HDL 公开发表

1995 Verilog IEEE1364 标准公开发表

1990有关Verilog HDL的 全部权利都移交给OVI(Open Verilog International)组织

2013-8-4 南通大学电子信息学院 6

1.2.3 Verilog HDL的优点

2013-8-4

南通大学电子信息学院

24

例2-2b 4选1多路选择器

module mux4_to_1 (out, i0, i1, i2, i3, s1, s0); output out; input i0, i1, i2, i3; input s1, s0; wire s1n, s0n; wire y0, y1, y2, y3; not not0(s1n, s1); not not1(s0n, s0); and and0(y0, i0, s1n, s0n); and and1(y1, i1, s1n, s0); and and2(y2, i2, s1, s0n); and and3(y3, i3, s1, s0); or or0(out, y0, y1, y2, y3); endmodule

2013-8-4 南通大学电子信息学院 3

Verilog HDL数字设计教程(贺敬凯)第1章

路网表。

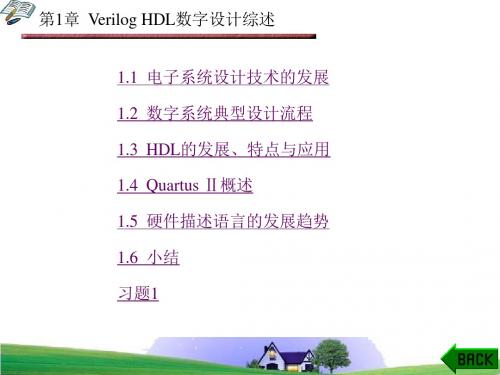

第1章 Verilog HDL数字设计综述

波形图输入方法则是将待设计的电路看成是一个黑盒子,

只需告诉EDA工具该黑盒子电路的输入和输出时序波形图,

EDA工具就可以完成黑盒子电路的设计。 原理图输入方法是一种类似于传统电子设计方法的原理 图编辑输入方式,即在EDA软件的图形编辑界面上绘制能完 成特定功能的电路原理图。原理图由逻辑器件(符号)和连接

理图和信号的连接表,如果是一个大的系统,将是一大摞图

纸,以后系统若出现问题,查找、修改起来都很麻烦。

第1章 Verilog HDL数字设计综述

上述过程是从底层开始,或在已有的功能模块的基础上 来搭建高层次的模块直至整个系统的。因此这种传统的电子 系统的设计过程是一种自底向上(Bottom-Up)的设计,设计 过程必须从存在的基本单元模块出发,基本单元模块必须是 已经设计成熟的标准单元模块或其他项目已开发好的单元模 块。

第1章 Verilog HDL数字设计综述

本书所有设计最终的实现目标主要定位于FPGA,因此下

面重点介绍FPGA的开发流程。FPGA的EDA开发流程如图1-3

所示。

第1章 Verilog HDL数字设计综述

图1-3 FPGA的EDA开发流程

第1章 Verilog HDL数字设计综述

从图1-3可以看出,FPGA的开发流程与图1-2所示的用 EDA工具设计数字系统的流程基本相同,都需要设计输入、 功能仿真、逻辑综合、布局布线(适配)、时序仿真、物理实 现等几个步骤。下面将分别介绍主要设计模块的功能特点。

第1章 Verilog HDL数字设计综述

1. 设计输入 在EDA软件平台上开发FPGA/CPLD时,首先要将电路系 统以一定的表达方式输入计算机。通常,EDA工具的设计输 入可分为以下两种类型:

数字系统设计与Verilog HDL

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

Verilog HDL简明教程中文版

中文版Verilog HDL简明教程Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口PLI,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。

但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。

当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

第1章简介Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、Verilog HDL 设计流程:1、文本编辑:文件保存为.v的文件;2、功能仿真:将.v文件调入HDL仿真软件,逻辑功能是否正确(前仿真);3、逻辑综合:将源文件调入逻辑综合软件进行综合,把语言综合成最简的布尔表达式,生成.edf的EDA工业标准文件;矚慫润厲钐瘗睞枥庑赖。

4、布局布线;5、时序仿真:验证电路的时序(后仿真)。

2、Verilog 程序包括四部分:1、端口定义2、I/O口说明3、内部信号声明4、功能定义3、逻辑功能定义:三种方法在模块中产生逻辑:(1)用assign 声明语句;如assign a = b & c;(描述组合逻辑)(2)用实例元件;如and #2 u1(q,a,b);(3)用always块;如(既可描述组合逻辑也可描述时序逻辑)always @ (posedge clk or posedge clr)beginif(clr) q <= 0;else if(en) q <= d;end4、网络类型变量两种:wire triWire型变量:用来表示单个门驱动或连续赋值语句驱动的网络类型数据。

Tri 型变量:用来表示多驱动器驱动的网络型数据。

线网类型两种:wire triTri 主要用于定义三态的线网;Wire型:代表的是物理连接,不存储逻辑值,要由器件驱动,通常用assign进行赋值Wire类型的信号没被驱动,缺省值为Z(高阻);信号没有定义数据类型时,缺省为wire 类型。

(缺省==默认)聞創沟燴鐺險爱氇谴净。

Reg型:默认初始值为x,通常用always模块内的指定信号,常代表触发器;always模块内被赋值的每一个信号都必须定义为reg型。

(寄存器类型)Verilog HDL 有5种寄存器类型:reg、integer、time、real、realtime5、运算符号所带操作数单目运算符:可带一个操作数,操作数放在运算符右边双目运算符:可带两个操作数,操作数放在运算符两边三目运算符:可带3个操作数,用三目运算符分隔开6、底层模块的调用:底层模块(被测试模块)可由测试模块调用如:(位置关联方式) :AND_G2 AND_G2(A,B,F);第一个AND_G2 为底层模块名,第二个为实例名,(A,B,F)为参数定义。

语法结构为:底层模块名实例名参数定义参数定义重要;A,B,F 相应的在底层模块也有A,B,F参数顺序也要注意,与测试模块一一对应,不一定要同名。

(名称关联方式):AND_G2 AND_G2(.A(Cin),.B(Sum),.F(S1));排列顺序不重要。

在模块实例化语句中,允许端口出现悬空,可将端口表达式表示为空白来指定悬空端口。

7、测试模块(testbench)模块的定义和调用(实例化)类似于软件中函数的定义和调用,但二者有本质的区别:软件的函数调用只是对同一段程序的使用,不管调用多少次,这个函数在程序中只有这么一段;模块的定义和调用是硬件的实现,每一次调用(实例化)都将产生实现这个模块功能的一组电路。

若调用两次NAND模块,就在AND模块中产生两块实实在在的NAND电路。

残骛楼諍锩瀨濟溆塹籟。

8、监测功能,仿真可显示变量的值;$monitor如:$monitor("Time=%0d a=%b b=%b out1=%b out2=%b",$time,a,b,out1,out2);酽锕极額閉镇桧猪訣锥。

仿真显示:# Time=0 a=0 b=0 out1=1 out2=0# Time=1 a=1 b=0 out1=1 out2=0# Time=2 a=1 b=1 out1=0 out2=1# Time=3 a=0 b=1 out1=1 out2=09、在Verilog HDL程序中,语句空格没有任何意义。

只有出现在字符串中的空格才有意义;在Verilog HDL程序中,区分大小写,sum与SUM代表的意义不同。

彈贸摄尔霁毙攬砖卤庑。

10、预处理指令`define 、`undef、`ifdef、`else、`endif、`include、`timescale謀荞抟箧飆鐸怼类蒋薔。

(1)`define 与C中#define功能相同,`undef 取消前面`define 指令所作的定义;厦礴恳蹒骈時盡继價骚。

(2)`ifdef、`else、`endif 与if-else结构类似,条件编译;`ifdef WINDOWSparameter WORD_SIZE = 16`elseparameter WORD_SIZE = 12`endif(3)`include 用于嵌入“内嵌文件”的内容`include "../../halfadder.v" //双引号是要内嵌的文件的路径和文件名module adder;........endmodule(4)`timescale 编译器指令定义时延单位和时延精度在Vreilog HDL中,所有时延都用单位时间表示,格式为:`timescale time_unit/time_precision 时延单位/时延精度条件语句if 使用注意事项:(1)条件表达式需用括号括起来;(2)if-if-else....else与if搭配问题,else与最近的一个if搭配;(3)if-if语句,要使用块语句begin...end:(4)具有优先级,排在前面某个分支的条件满足就会执行那个分支,然后跳出整个if结构。

if(CLK)beginif(Reset)Q = 0;else Q = D;end(4)锁存器:若无缺省语句,则将产生一个锁存器if(T)Q = D;Case语句条件表达式、分支表达式case()............default: ......end case注意:case的缺省项(default: ......)必须写,以防止产生锁存器;While语句While (表达式) 语句或While(表达式) begin 多余语句end如:对reg1 8位二进制数中值为1 的位进行计数;beginreg[7:0] regtempcount = 0;regtemp = reg1;while(regtemp)beginif(regtemp[0]) count = count + 1; //若第一位为1进行count计数茕桢广鳓鯡选块网羈泪。

regtemp = regtemp >> 1; //右移运算endendfor语句一般形式:for (表达式1;表达式2;表达式3)11、结构说明语句Verilog HDL 语言中过程模块从属于4种结构说明语句:initial、always、task、function 说明语句(1)、intitial只执行一次,always语句则不断重复执行,initial用于对各变量的初始化。

每个initial 和always 说明语句在仿真开始时同时进行。

鹅娅尽損鹌惨歷茏鴛賴。

initialbegin语句1;语句2;......语句n;end(2)、always 声明格式如下:always<时序控制><语句>always需与一定的时序控制结和才有用;always 时序控制可以是:沿触发、电平触发、单个信号、多个信号(or)(3)、task 定义任务(4)、function 定义函数可简化程序的结构,编写大型模块。

注意task 与function 的不同点;?13、V erilog HDL 系统功能调用:以字符"$"开头的标识符(1)任务型的功能调用,系统任务(2)函数型的功能调用,系统函数标准输出任务:$display、$write $display("d=%0h a=%0h",data,addr);籟丛妈羥为贍偾蛏练淨。

仿真控制任务:$monitor $monitoron///$monitoroff 控制$monitor 的启动与停止預頌圣鉉儐歲龈讶骅籴。

时间系统度量函数:$time、$realtime 得到当前的仿真时间文件管理任务:$fopen 打开文件<file_handle>= $fopen("file_name");file_name为被打开的文件名及其路径14、事件控制(1)边沿触发事件:@@ event procedural_statement ;event 为边沿事件@(posede Clock) Curr_State = Next_State; /在CLK的上升沿执行赋值语句渗釤呛俨匀谔鱉调硯錦。

(2)电平敏感事件:waitwait (Condition) procedural_statement ;Condition为电平敏感事件铙誅卧泻噦圣骋贶頂廡。

15、initial语句和always语句,所有过程语句都必须封装成语句块(只有一条语句除外)(1)顺序语句块(begin-end) 按书写顺序依次执行(2)并行语句块(fork-join) 块中语句并行执行(与书写顺序无关)语句块可有一个标识符作为其名称,带有名称的语句块可以在其内部声明局部寄存器变量,而且带名称的语句块可被引用。

擁締凤袜备訊顎轮烂蔷。

16、过程性赋值两种:阻塞(=)、非阻塞(<=)(1)只出现在initlial语句和always语句内;(2)过程性赋值只能给寄存器变量赋值;(3)赋值表达式的右端可以是任何表达式。

阻塞(=)在执行时,处于其后的其他赋值语句都不能执行;对同一个变量做连续阻塞赋值,其值由最后一个赋值语句决定。

贓熱俣阃歲匱阊邺镓騷。

非阻塞(<=)只能用于给寄存器赋值,处于其后的其他赋值语句可以执行。

在执行过程中有一个微小的时间间隔。

17、过程连续性赋值assign-deassign(赋值-重新赋值)用于对寄存器赋值;force-release(强制-释放)对寄存器与线网都能赋值。

18、Verilog HDL 两种建模方法:行为建模、结构建模行为建模:数据流行为建模(assign)assign只能用于对线网类型赋值;(连续赋值语句)顺序行为建模(initial语句、always语句)驱动寄存器;(过程赋值语句)不同点连续赋值过程赋值assign 有无坛摶乡囂忏蒌鍥铃氈淚。

符号= = 或<=蜡變黲癟報伥铉锚鈰赘。

位置不在always、initial出现在always或initial出现買鲷鴯譖昙膚遙闫撷凄。

执行条件与等号右端操作数的值发生变化有关与周围其他语句有关用途驱动线网驱动寄存器綾镝鯛駕櫬鹕踪韦辚糴。

结构建模:内置基元实例化语句,模块实例化语句,UDP实例化语句19、循环语句四类:forever、repeat、while、for循环语句forever语句:过程语句必须要有某种形式的时序控制,否则forever会再0时延后永远重复执行过程语句;(用于产生周期性的波形作为仿真测试信号)repeat语句:repeat(loop_count)procedural_statement ;loop_count为控制循环的常数或变量repeat(Count)@(posedge Clk) Sum = Sum + 1;与Sum = repeat(Count)@(posedge Clk) Sum + 1;的区别???20、前仿真与后仿真(重要)前仿真也称为功能仿真,主要在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟,主要是验证电路与理想情况是否一致。