版图寄生效应

版图设计中的寄生参数分析

版图设计中的寄生参数分析1.引言正如我们了解的,工艺层是芯片设计的重要组成部分。

一层金属搭在另一层金属上面,一个晶体管靠近另一个晶体管放置,而且这些晶体管全部都是在衬底上制作的。

只要在工艺制造中引入了两种不同的工艺层,就会产生相应的寄生器件,这些寄生器件广泛地分布在芯片各处,更糟糕的是我们无法摆脱它们。

寄生器件是我们非常不希望出现的,它会降低电路的速度,改变频率响应或者一些意想不到的事情发生。

既然寄生是无法避免的,那么电路设计者就要充分将这些因素考虑进去,尽量留一些余量以便把寄生参数带来的影响降至最低。

2.寄生参数的种类寄生参数主要包括了电容寄生、电阻寄生,和电感寄生。

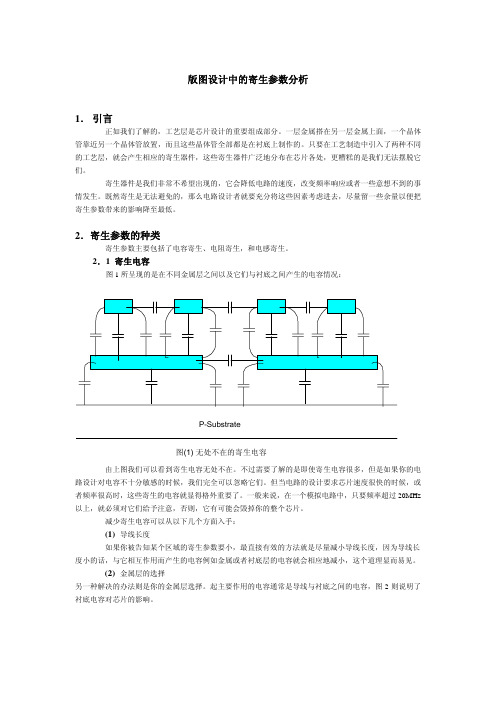

2.1 寄生电容图1所呈现的是在不同金属层之间以及它们与衬底之间产生的电容情况:图(1) 无处不在的寄生电容由上图我们可以看到寄生电容无处不在。

不过需要了解的是即使寄生电容很多,但是如果你的电路设计对电容不十分敏感的时候,我们完全可以忽略它们。

但当电路的设计要求芯片速度很快的时候,或者频率很高时,这些寄生的电容就显得格外重要了。

一般来说,在一个模拟电路中,只要频率超过20MHz 以上,就必须对它们给予注意,否则,它有可能会毁掉你的整个芯片。

减少寄生电容可以从以下几个方面入手:(1)导线长度如果你被告知某个区域的寄生参数要小,最直接有效的方法就是尽量减小导线长度,因为导线长度小的话,与它相互作用而产生的电容例如金属或者衬底层的电容就会相应地减小,这个道理显而易见。

(2)金属层的选择另一种解决的办法则是你的金属层选择。

起主要作用的电容通常是导线与衬底之间的电容,图2则说明了衬底电容对芯片的影响。

Noisy Quiet图(2) 衬底电容产生的噪声影响如上所示,电路1和电路2都对地产生了一个衬底电容,衬底本身又有一个寄生电阻,这样一来电路1的噪声就通过衬底耦合到电路2上面,这是我们不希望看到的。

(设法使所有的噪声都远离衬底)因此我们改变一下金属层,通常情况下,最高金属层所形成的电容总是最小的。

版图设计规则

精选ppt

12

设Байду номын сангаас规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension),

如图 (b)

精选ppt

13

TSMC_0.35μm CMOS工艺版图 各层图形之间最小交叠

精选ppt

14

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

精选ppt

15

设计规则举例

精选ppt

16

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

•Sizing Commands(尺寸命令)

把整个图形扩展

扩展边沿

线扩精选展ppt

26

Layer Processing(层处理命令)

•Selection Commands(选择命令)

顶点

octagon

图形

精选ppt

27

Layer Processing(层处理命令)

(NM OMS/1P-MM5O(7S8防m止O穿h通m/注sq入) T)hickVTN/VtoPpN-m=eNta/l P(1C8hmaOnhnmel/sq)

Threshold Voltage Adjust

(NMOS阈值电压调节注入)

精选ppt

6

设计规则(design rule)

eetop[1].cn_05nCalibre xRC

![eetop[1].cn_05nCalibre xRC](https://img.taocdn.com/s3/m/32308bf59e31433239689340.png)

应用Calibre xRC 辅助模拟电路版图纠错威盛电子(中国)有限公司 蔡光杰[摘要]在模拟电路设计中,在版图完成之后进行带寄生参数仿真是必要的,该仿真能够检查实际的版图在多大程度上符合我们的设计要求。

Calibre xRC是一款优秀的版图寄生电阻电容抽取工具,它能提供非常详细的寄生参数信息。

但是,越是详细的寄生参数网表就必然导致越长的仿真时间,这往往给电路的后仿真带来一些不方便,增加电路纠错的周期。

本文将根据实际工作的经验,介绍如何使用Calibre xRC的RC-Reduction和Lumped C功能来简化寄生参数网表,以缩短电路纠错的周期,以及在实际中的应用效果。

1.寄生电阻电容对模拟电路的影响在模拟电路设计中,电路中的各种寄生效应对性能影响很大。

一般来说,寄生电阻和寄生电容对电路的影响最为明显。

如果忽略寄生效应的影响,会导致仿真结果偏离了真实情况,甚至会出现错误的结果。

如果能抽取出这些寄生效应的数据,结合电路进行仿真,就能够比较准确的模拟真实电路的特性。

Calibre xRC 为我们提供了抽取电路寄生参数的解决方案。

通过对电路版图的分析,Calibre xRC能够抽取对电路性能影响最为重要的寄生电阻和寄生电容。

然而随着电路的复杂度上升,我们抽取出来的带有寄生电容和寄生电阻的网表变得巨大而且复杂,使用这样的网表进行仿真需要的时间也变得非常长。

如果我们通过仿真发现电路存在问题,需要寻找问题所在并要进行多次仿真,则可以通过Calibre xRC 的一些选项来简化网表,并且使得问题更容易被发现。

下面两个例子分别使用RC-Reduction和Lumped C来简化后仿真网表,并且使我们能迅速找到问题所在。

2.快速定位影响电路性能的主要寄生电阻下面举的例子是应用在Audio方面的电路,如图1所示,相对应的版图如图2所示。

图1图2这是一个单声道功率放大器,带音量调节功能和静音功能。

电路由三部分组成,功率放大器,可调电阻单元,数字逻辑控制单元。

版图寄生参数提取技术的研究

4.学位论文李宁深亚微米集成电路互连RC网络约简算法分析2005

随着半导体工艺特征尺寸的迅速减小,电路的性能越来越多地取决于互连线而不是器件。互连寄生延迟将大大超过器件延迟而成为制约系统时钟频率的关键因素。就是说,大部分时钟周期将被消耗在数据传输过程当中,而不是像过去那样,是消耗在数据的运算和生成过程中。全局互连线的寄生效应仍将是制约电路性能的瓶颈。不断提高互连质量,准确快速分析互连寄生效应将始终是一个具有挑战性的重要课题。由于寄生参数对电路性能的影响十分重要,设计人员一般把寄生参数的分析分作两个阶段:寄生参数提取和寄生参数分析。寄生参数提取是指将版图中的互连线经过抽象形成寄生的电阻和电容器件,而寄生参数分析是指针对提取的RC电路进行模拟和运算,分析这些RC对电路的影响。经过寄生参数提取形成的电路网表在规模上远远大于没有经过寄生参数提取的网表,这对后续的RC分析效率带来了极大困难。寄生参数提取之后网表规模急剧增长的主要原因是:版图中的互连线长度较长,并且通过通孔连接到不同的布线层上,在参数提取时,对这类互连线要切割为许多小的线段形成多个寄生电阻,此外,由于耦合寄生电容的存在,寄生电容个数也很大。为了提高后续RC分析的效率,在寄生参数提取和寄生参数分析两个阶段之间往往需要加入一个RC约简的步骤。它的基本出发点是:在保持电路近似等价的前提下,通过一定的等价变换,大大减小寄生参数网表的规模。一般来说,RC约简后的网表规模会比约简前减少一个数量级以上。本文针对互连RC约简的技术难点,对经典的RC网络约简算法PACT算法改进计算环节提出了若干解决方法,明显提高了计算的精度与速度。采用了RCM预处理技术来对矩阵的变量重新编号,对经过RCM预处理的矩阵进行Cholesky分解,其分解结果的非零元素比不经过预处理分解的非零元素减少20%以上,大大提高了程序效率。提出一种十分简便的Lanczos计算方法,有效地解决稠密矩阵特征值分解的问题。采用了特殊的Lanczos初始向量设置方法,保证了恶性中断不会发生。克服了经典PACT算法的局限性,使之可以适用于实际应用的各种电路的网络约简,如纯电阻网络,纯电容网络,没有直流通路到端口的特殊电路等,从而提高了该算法的适用性。基于上述算法开发了互连RC网络约简软件ZeniRCR,通过大量来自VLSI实际版图算例的测试结果表明,ZeniRCR具有优越的性能和很强的竞争能力。

电容器的寄生效应

pedestrian初级会员注册日期: Sep 2001 来自:发帖数量: 3电容的介质吸收的图示pedestrian 上传了这个图片:向版主反映这个帖子| < a>09-18-2001 09:09 PMpedestrian初级会员注册日期: Sep 2001 来自:发帖数量: 3电容器的寄生效应我们都希望我们所用的电容器是一个理想的电容器,但事实并非如我们所愿。

实际电容器存在一些寄生效应:电容泄漏电阻Rp、串联损耗电阻Rs、串联电感Ls、介质损耗Rda+Cda 等。

各种实际电容器的不同,一是在于容量大小不同,二则是这些寄生效应的大小不同。

电容器主要用于耦合(通交流隔直流)、去耦(滤除叠加在直流中的交流分量)、滤波器、选频网络、取样保持电路等等。

不同的用途,对于电容的要求各不相同,所以在电路设计中对电容器的选用很重要。

那么首先就要了解这些寄生效应对各应用的影响,以及各种电容器在这些寄生效应上的比较。

泄漏电流电容泄漏电流大小在等效电路中表示为泄漏电阻Rp的大小,Rp越大,电容泄漏则越小;在电容技术指标中常用漏电流或绝缘电阻来衡量;在耦合和取样保持电路中,低电容泄漏(高Rp)非常重要;电解电容具有相对较高的泄漏电流,而且在刚上电开始工作的几分钟内会有更高的泄漏电流;钽电解电容比铝电解电容有更小的泄漏电流,但价格较高。

钽电解电容的泄漏电流大约为5nA/µF,而铝电解电容的泄漏电流大约为20nA/µF;其它类型的电容,泄漏电阻一般都大于几百GΩ,所以在大多数应用场合对它们的泄漏电流忽略不计。

损耗电阻(等效串联电阻ESR)电容损耗电阻Rs越大,损耗越大;在电容技术指标中常用损耗角正切来衡量;当较大交流电流流过电容时,Rs就消耗一部分功率,所以在RF电路和带高电流纹波去耦中,低损耗电阻就显得非常重要,但在高精度模拟电路中损耗电阻并不会带来什么影响。

串联电感(等效串联电感ESL)串联电感Ls的大小,决定了电容的工作频率,Ls越大,工作频率就越低;电容器的一常见结构是两片金属箔夹着一片纸质或是塑料介质,卷成卷,这种结构的电容本身就有相当大的电感,这就使得在频率大于几MHz的时候,其电感量大过电容量,所以不能用电解电容或是薄膜电容来作高频去耦;片状瓷介电容有比较低的串联电感(取决于它的层叠式结构),但它会产生颤噪声,有的会因高Q值而自谐振,而圆片瓷介电容由于引线会有较高的串联电感;钽电解电容和片状瓷介电容并联,可以保证模拟电路足够的去耦(连接片状瓷介电容印制板走线要短!)。

北大集成电路版图设计课件_第5章 电容和电感精选全文

一. 电 容

3. 金属-多晶硅电容

如果利用多晶硅作为电容的下极板,金属作为电容的上极板,

就可形成金属-多晶硅电容。如图5.9所示,金属-多晶硅电容

与多晶硅-多晶硅电容相似,只不过上极板是金属而不是多晶

硅。

多晶硅

金属

C1

C2

C1

衬底

场氧化层

图 5.9 金属-多晶硅电容示意图

一. 电 容

4. 金属-金属电容 如果电容的上下极板都用金属来构成,就会形成金属-金属电

一. 电 容

Bad

Good

电容匹配规则

一. 电 容

3. 匹配电容的大小要适当。 电容的随机失配与电容面积的平方根成反比,但并不是

面积远大匹配就越好。总是存在一个最佳电容尺寸,超过 这个尺寸,梯度效应就会非常明显,从而影响匹配。

某些CMOS集成电路工艺中,正方形电容的尺寸应该介 于20μm×20μm至50μm×50μm之间。超过该尺寸的电 容应该被划分成多个单位电容,利用适当的交叉耦合减小 梯度影响,改善电容整体的匹配性。 4. 匹配电容要邻近摆放。

一. 电 容

多晶硅-多晶硅电容通常制作在场区处,由场氧化层把电容 和衬底隔开。由于场氧化层较厚,所以多晶硅-多晶硅电容的 寄生参数小,而且无横向扩散影响。通过精确控制两层多晶 硅的面积以及两层多晶硅之间的氧化层的厚度,可得到精确 的电容值。

由于多晶硅-多晶硅电容制作在场氧化层上,所以电容结构 的下方不能有氧化层台阶,因为台阶会引起电容下极板的表 面不规则,将造成介质层局部减薄和电场集中,从而破坏电 容的完整性。

金属2

(厚)电介质

金属1

一. 电 容

为了减小金属-金属电容所占用的面积,在多层金属互连系统中 可以制备叠层金属电容。多层金属平板垂直地堆叠在一起,从 上至下,每两层金属之间都存在电容。通过将奇数层金属连接 在一起作为一个电极,而将偶数层金属连接在一起作为另一个 电极。从剖面图来看,金属-金属电容是梳状交叉结构。

版图设计期末复习

第一章绪论1、什么是Scaling-down,它对集成电路的发展有什么重要作用?在器件按比例缩小过程中需要遵守哪些规则(CE,CV,QCE),这些规则的具体实现方式(1)为了保证器件性能不变差,衬底掺杂浓度要相应增大。

通过Scaling-down使集成电路的集成度不断提高,电路速度也不断提高,因此Scaling-down是推动集成电路发展的重要理论。

(2)在CE规则中,所有几何尺寸,包括横向和纵向尺寸,都缩小k倍;衬底掺杂浓度增大k倍;电源电压下降k倍。

(3)在CV规则中,所有几何尺寸都缩小k倍;电源电压保持不变;衬底掺杂浓度增大k2倍。

(4)在QCE规则中,器件尺寸k倍缩小,电源电压α/k倍(1<α<k)变化,衬底掺杂浓度增大αk倍2、什么是摩尔定律?集成电路容量每18个月增加一倍。

3、什么是版图设计?包含哪两个要素?(1)版图设计就是按照线路的要求和一定的工艺参数,设计出元件的图形并进行排列互连,以设计出一套供IC制造工艺中使用的光刻掩膜版的图形,称为版图或工艺复合图(2)一定功能的电路结构;一定的工艺规则4、集成电路全定制和半定制设计的过程,及区别自动化技术:半定制,标准单元技术手工技术:全定制,一般用于高性能数字电路或者模拟电路第二章电路基础知识1、管子的串并联,电阻模型分析。

串联:两个宽长比为W/L的管子串联,若等价为一个管子,其宽长比为多少?并联:两个宽长比为W/L的管子并联,若等价为一个管子,其宽长比为多少?2、管子的尺寸标注3、复杂逻辑门的功能分析(写出逻辑表达式),或根据逻辑表达式,画出CMOS电路图4、传输门结构,原理(1)由两个增强型MOS管(一个P沟道,一个N沟道)组成。

(2)C=0,!C=1时,两个管子都夹断,传输门截止,不能传输数据。

(3)C=1,!C=0时,传输门导通。

(4)双向传输门:数据可以从左边传输到右边,也可以从右边传输到左边,因此是一个双向传输门。

第五章 寄生参数

双极型晶体管的例子

匹配

匹配规则: 1.把匹配器件相互靠近放臵。 2.注意周围器件; 3.保持器件的方向一致;

根器件方法 第一种策略:保持在同一方向上; 第二种策略:采用跟部件;

根部件:采用库中的一个器件,用这同一器件 来设计所有其它器件;

不足之处:较大的电阻上的接触电阻会成为整 个电阻很显著的一部分;

四方交叉

如果只有两个器件,可以把每一个器件分为两半, 然后把它们成对角线放臵,称为四方交叉技术 四方交叉技术非常适合于“高度匹配”的要求

四方交叉技术只能应用于两个被一分为二 的器件;

四方交叉可以是任意一对器件;

图中,在集电极和基极的布线之间存在不必要 的额外重叠,这些额外的重叠是为了均衡某些 交叉寄生参数。 匹配规则:使布线上的寄生参数匹配

经济四方交叉

匹配规则:使每个器件都对称 对称性是版图中主要考虑的问题

匹配信号路径

差分逻辑要求高度匹配的电路。 在CMOS逻辑中,0和1分别代表高电平和低电 平。每个信号中只有一条导线。一条导线可以 传送低或高电平。 在差分逻辑中每个信号有两条导线,确定在两 条导线上两个信号之间的差别就知道了逻辑状 态。可以通过一个电压减去另一个电压的差来 决定逻辑状态。

使器件宽度一致; 采用尺寸较大的器件; 与电路设计者交流; 注意邻近的器件;

计算IR压降

布线方案 当对IR压降的限制和电路中电路的大小了解后, 就会意识到必须把电源线分成多条导线才能满 足这些条件。

不足的是功率大的电路离压焊块最远。

根据总共19毫安的总电流来确定整条导线的宽度

有各种方案,具体采用哪种方案取决于 电路的要求

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

– Used 120µmwide device – Trouble accurately fitting y-parameters using traditional small signal model – Instead used measured y-parameters from 120µm device

→ Degradation of large device performance!

SSC San Diego

HIGH SPEED DEVICE GROUP

SOS Technology

Device gg(µm) Device L L (µm) NMOS 0.5 NMOS 0.5 PMOS 0.5 PMOS 0.5 ft (GHz) F (dB) Ga (dB) max MIN ft(GHz) (GHz) ff F max (GHz) MIN (dB) G a (dB) 25 66 0.9 21 25 66 0.9 21 14 41 0.9 13 14 41 0.9 13

High S peed High Power

Lower Sp eed

• Microwave gain drops

– Technology to increase breakdown – Use of many fingers in parallel

SSC San Diego

HIGH SPEED DEVICE GROUP

SSC San Diego

Model Verification (Wg=432µm)

0.12 0.10 0.08 0.06 0.04 0.02 0.00 -0.02 0 5 10

Frequency (GHz) Model: Model: Meas: Meas: Real Y11 Imaginary Y11 Real Y11 Imaginary Y11

Model: Model: Meas: Meas:

Real Y21 Imaginary Y21 Real Y21 Imaginary Y11

0.02 0.01 0.01 0.00 0 5 10 Frequency (GHz) 15 20

SSC San Diego

HIGH SPEED DEVICE GROUP

Real Y12 Imaginary Y12 Real Y12 Imaginary Y12

0.20

0.00 -0.05

0.00

-0.10 -0.15 -0.20

-0.20

-0.40 0 5 10 Frequency (GHz) 15 20

SSC San Diego

HIGH SPEED DEVICE GROUP

f max (GHz)

f t (GHz)

Transmission Line Model

• Elements are distributed • Usually used to model gate finger • Small signal model used for unit gate finger

Large FET RF Performance

20 18 16 14 12 10 8 6 4 2 0 0 1000 2000 3000 4000 5000 Gate Width ( µm)

45 40 35 30 25 20 15 10 5 0 0 1000 2000 3000 4000 Gate Width (µ m) 5000

in So ur Dr a ce

Rg Cgs Ri Cgd Rd

g m e jτ

Cds

Rout

Rs

SSC San Diego

HIGH SPEED DEVICE GROUP

Problem Setup

Id Ig Is Gate Source

vg ′( x) = − Zg ⋅ ig ( x) + jω ⋅ [ Mgd ⋅ id ( x) − Mgs ⋅ is ( x)] vd ′( x) = Zd ⋅ id ( x) + jω ⋅ [− Mgd ⋅ ig ( x) − Mds ⋅ is ( x)] vs ′( x) = − Zs ⋅ is ( x) + jω ⋅ [ Mds ⋅ id ( x) − Mgs ⋅ ig ( x)]

Outline

• Introduction • Large FET Performance • Transmission Line Model • Verify Model • Summary

SSC San Diego

HIGH SPEED DEVICE GROUP

Device Scaling

gm ft = 2πCin

Model Verification (Wg=1296µm)

0.80

0.25

0.60

Model: Model: Meas: Meas:

Real Y11 Imaginary Y11 Real Y11 Imaginary Y11

0.20 0.15 0.10 0.05

0.40

Model: Model: Meas: Meas:

• Need many fingers connected in parallel

– Interconnects introduce extra resistance, capacitance, and delay → ft and fmax decrease with width

Drain Gate

vgs ′′( x) = α ⋅ vgs ( x) + β ⋅ vds( x) vds ′′( x) = δ ⋅ vgs( x) + γ ⋅ vds( x)

Drain

• Derive expressions for change in voltage and current along the lines

2160µm

Gate

• Simple devices design so that analytical solution would be good representation • Drain/Gate/Source bus lines straight transmission lines

HIGH SPEED DEVICE GROUP

Rg Cgs Ri Cgd Rd

g m e jτω

Cds

Rout

g d e jτ 2ω

Rs

SSC San Diego

HIGH SPEED DEVICE GROUP

Experiment

Drain x1 x3 x5

Drain

Drain Drain

Source Gate

Gate

432µm

Gate

1296µm

– Ig(0)=Ig, – Id(0)=0, Ig(L)=0 Id(L)=Id

– Vgs(0)=Vgs Vds(0)=Vds

jω 2 2 − α − jω M β − M β + M 2 2 r+ gd ds gs r+ −α Z g r− −α − Z M gd β + M ds β − M gs r− −α Zg g − Z11 = 2 −r 2 r+ Tanh( r+ L ) r− Tanh( r− L ) r− + Z gδ 2 2 r− − r+

Layout Parasitic Effects on Microwave Characteristics of Large Periphery Transistors

M. Wetzel, P. R. de la Houssaye*, P.M. Asbeck, I. Lagnado*

Department of Electrical and Computer Engineering, UCSD * Space and Naval Warfare Systems Center, San Diego

(

(

))

(

(

))

• Currents used in solution of Vgs(x) and Vds(x) • Z-parameters

– Z dij

= Vi Ij

Z 21 =

jω M gd β − M ds β jω M gd β − M gsδ + M gs 1− + M gs 1− Z 2 −α 2 −α Zg g r+ r− − r− Sinh( r− L ) r+ Sinh( r + L )

Inductance (nH), Quality Factor

25

• Leff=0.35µm, Si thickness=1000Å, metal T-gate • Interconnect modeling can be applied to any technology

Aluminum T-Gate Al TiSi2 SiO2 Al TiSi2

f max ft = 2 2πf t Rg C gd + G o [Rg + Rs ]

Source • Parameter scaling – Conductances and capacitances scale linearly with width – Resistances scale inversely with width → ft and fmax ideally do not change with width

0.05 0.05 0.04 0.04 0.03 0.03