2章-晶体管的寄生效应

《半导体集成电路》考试题目及参考答案

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性 开门/关门电平 逻辑摆幅 过渡区宽度 输入短路电流 输入漏电流静态功耗 瞬态延迟时间 瞬态存储时间 瞬态上升时间 瞬态下降时间瞬时导通时间2. 分析四管标准TTL 与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

工程技术基础-热插拔知识详解及案例分析

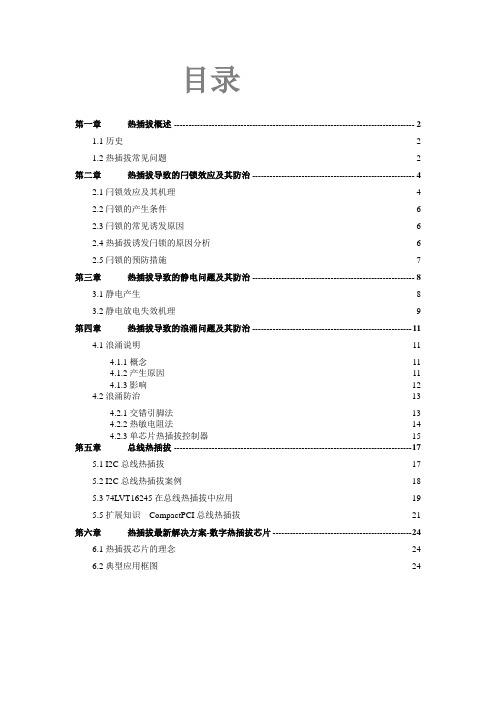

目录第一章热插拔概述 ----------------------------------------------------------------------------------- 21.1历史-------------------------------------------------------------------------------------------------------- 21.2热插拔常见问题 ---------------------------------------------------------------------------------------- 2第二章热插拔导致的闩锁效应及其防治 -------------------------------------------------------- 42.1闩锁效应及其机理------------------------------------------------------------------------------------- 42.2闩锁的产生条件 ---------------------------------------------------------------------------------------- 62.3闩锁的常见诱发原因---------------------------------------------------------------------------------- 62.4热插拔诱发闩锁的原因分析 ------------------------------------------------------------------------ 62.5闩锁的预防措施 ---------------------------------------------------------------------------------------- 7第三章热插拔导致的静电问题及其防治 -------------------------------------------------------- 83.1静电产生 ------------------------------------------------------------------------------------------------- 83.2静电放电失效机理------------------------------------------------------------------------------------- 9第四章热插拔导致的浪涌问题及其防治 ------------------------------------------------------- 114.1浪涌说明 ------------------------------------------------------------------------------------------------ 114.1.1概念 ---------------------------------------------------------------------------------------------- 114.1.2产生原因---------------------------------------------------------------------------------------- 114.1.3影响 ---------------------------------------------------------------------------------------------- 124.2浪涌防治 ------------------------------------------------------------------------------------------------ 134.2.1交错引脚法------------------------------------------------------------------------------------- 134.2.2热敏电阻法------------------------------------------------------------------------------------- 144.2.3单芯片热插拔控制器 ------------------------------------------------------------------------ 15第五章总线热插拔 ---------------------------------------------------------------------------------- 175.1 I2C总线热插拔---------------------------------------------------------------------------------------- 175.2 I2C总线热插拔案例 --------------------------------------------------------------------------------- 185.3 74LVT16245在总线热插拔中应用 --------------------------------------------------------------- 195.5扩展知识CompactPCI总线热插拔------------------------------------------------------------- 21第六章热插拔最新解决方案-数字热插拔芯片 ------------------------------------------------ 246.1热插拔芯片的理念------------------------------------------------------------------------------------ 246.2典型应用框图 ------------------------------------------------------------------------------------------ 24第一章热插拔概述1.1历史热插拔(hot-plugging或Hot Swap)即带电插拔,是指将设备板卡或模块等带电接入或移出正在工作的系统,而不影响系统工作的技术。

集成电路试题库

半导体集成电路典型试题绪论1、什么叫半导体集成电路?【答案:】通过一系列的加工工艺,将晶体管,二极管等有源器件和电阻,电容等无源元件,按一定电路互连。

集成在一块半导体基片上。

封装在一个外壳内,执行特定的电路或系统功能。

2、按照半导体集成电路的集成度来分,分为哪些类型,请同时写岀它们对应的英文缩写【答案:】小规模集成电路(SSI),中规模集成电路(MSI ),大规模集成电路(VSI),超大规模集成电路(VLSI ),特大规模集成电路(ULSI ),巨大规模集成电路(GSI)3、按照器件类型分,半导体集成电路分为哪几类?【答案:】双极型(BJT)集成电路,单极型(MOS)集成电路,Bi-CMOS型集成电路。

4、按电路功能或信号类型分,半导体集成电路分为哪几类?【答案:】数字集成电路,模拟集成电路,数模混合集成电路。

5、什么是特征尺寸?它对集成电路工艺有何影响?【答案:】集成电路中半导体器件的最小尺寸如MOSFET的最小沟道长度。

是衡量集成电路加工和设计水平的重要标志。

它的减小使得芯片集成度的直接提高。

6、名词解释:集成度、wafer size、die size、摩尔定律?【答案:】集成蔭--牛芯片上容帥的晶体莒的数目*辭畑:指包含我千上百于芯片的大圆硅片的玄径丄竝S1S4 :指段有封装的单个集成唱路“摩尔定律:集成电路的芯片的集咸度三年毎三年提四倍而加工尺寸缩屮远除分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,分析它的工作原7、理。

【答案:1T 二 CLJj 吗 MjkA —ir —该电路可以完成 NAND 逻辑。

与一般动态组合逻辑电路相比,它增加了一个MOS 管M kp ,它可以解决一般动态组合逻辑电路存在的电荷分配的问题。

对于一般的动态组合逻辑电路,在评估阶段, A= “ H B= “ L ”荷被OUT 处和A 处的电荷分配,整体的阈值下降,可能导致OUT 的输出错误。

抑制晶体管有源寄生效应研究

第 l 9卷 第 2期 20 0 7年 6月

甘 肃 科 学 学 报

J u n lo n u S in e o r a fGa s ce c s

Vo . 9 I1

No .2

J .07 un 2 0

抑 制 晶体 管 有源 寄 生效 应 研 究

The Re e r h t s r i tv f c s o r s t a i t r s a c o Re t a n Ac i e Ef e t f Pa a i e Tr nss o s

W U e ,S W i UN n,M A o g q a Qi Z n —un

c a a t rz i i li t g a e r n it r h t h v o r l y r s r c u e h r c e ie d g t n e r t d t a ss o s t a a e a f u —a e t u t r .Th a a o a e d t fEM d li t e mo e s o b

d at e l wih wihou p o ma i t t t a pr xi ton. By c omp rng t a i to f t r e l a i he v ra i ns o he cu r nt fowi hr u a h PN ng t o gh e c

述 出来 . 望这 些研 究 、 算 可作 为改 善 寄生晶 体管 希 计 影 响 的理 论 根 据 , 为集 成 电 路 的继 续 发展 做 出 自己

Ke r s Eb r — o l y wo d : e s M l mo e ;p r st r n it r ;wih u p r x ma i n d l a a ie t a ss o s t o t a p o i 中 , 于其 衬底 影 响 导 由

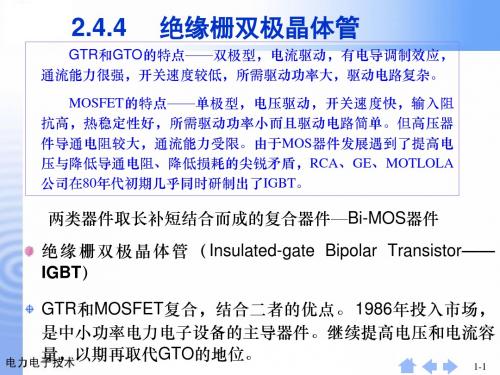

电力电子技术_第2章_器件5_IGBT

IGBT的转移特性和输出特性

a) 转移特性 b) 输出特性

• 当UCE<0时,IGBT处于方向阻断工作状态,在系统运行 中,IGBT处于开关状态,因而在正向阻断区和饱和区之 间来回转换。

1-8

IGBT的动态特性:开通特性

IGBT 的开通过程:与 MOSFET 的相似。

开 通 延 迟 时 间 td(on) : 10% uGE 到 10% iC幅值时间。 电流上升时间tr:10% iC幅值上升到 90% iC幅值时间。 集射电压下降时间 tfv : uCE 的下降 过程分为tfv1和tfv2两段。

1-5

集电极 C

N 沟道I G B T

IGBT实用等效电路

• Q1截止时IGBT的实 用等效电路 R d iD + • Uce<0,P N 反偏,反 VF 向阻断。Uce>0,N-P反 P u ds G 偏,正向阻断。正反 u ge N + 阻断能力近似相等。

C N

ic

P+

V u ce

iT

E

IGBT实用等效电路

栅极 Rd P G Q1 Q2 Rd N+ Q3 Q1 - + N PN 发射极 N+ P RB

C

N Q 2

P

+

P

RB

结构与电力 MOSFET区别 于N+层被P+ 层替换形成 IGBT的集电极

寄生三极管

Q2的出现使工作时产 生电导调制效应, NC C E 克服了高耐压与导 通电阻的矛盾。

P+ G G E E 图形符号

t 21 0.27ns Vceon 2.5V

tdoff

+ u g Vceon t -

寄生效应

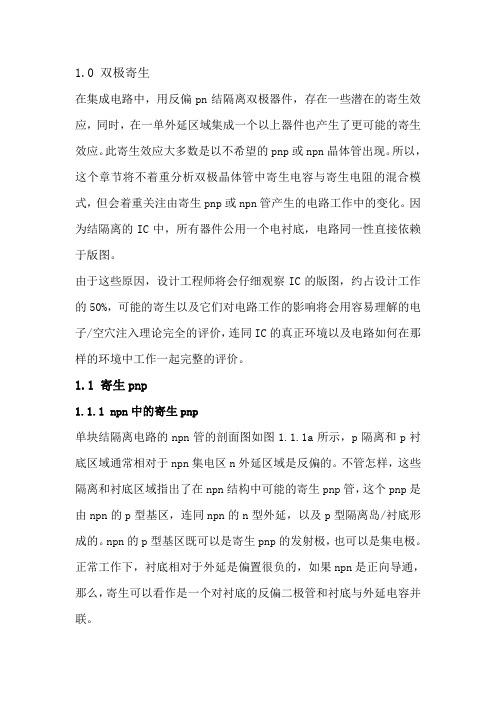

1.0 双极寄生在集成电路中,用反偏pn结隔离双极器件,存在一些潜在的寄生效应,同时,在一单外延区域集成一个以上器件也产生了更可能的寄生效应。

此寄生效应大多数是以不希望的pnp或npn晶体管出现。

所以,这个章节将不着重分析双极晶体管中寄生电容与寄生电阻的混合模式,但会着重关注由寄生pnp或npn管产生的电路工作中的变化。

因为结隔离的IC中,所有器件公用一个电衬底,电路同一性直接依赖于版图。

由于这些原因,设计工程师将会仔细观察IC的版图,约占设计工作的50%,可能的寄生以及它们对电路工作的影响将会用容易理解的电子/空穴注入理论完全的评价,连同IC的真正环境以及电路如何在那样的环境中工作一起完整的评价。

1.1 寄生pnp1.1.1 npn中的寄生pnp单块结隔离电路的npn管的剖面图如图1.1.1a所示,p隔离和p衬底区域通常相对于npn集电区n外延区域是反偏的。

不管怎样,这些隔离和衬底区域指出了在npn结构中可能的寄生pnp管,这个pnp是由npn的p型基区,连同npn的n型外延,以及p型隔离岛/衬底形成的。

npn的p型基区既可以是寄生pnp的发射极,也可以是集电极。

正常工作下,衬底相对于外延是偏置很负的,如果npn是正向导通,那么,寄生可以看作是一个对衬底的反偏二极管和衬底与外延电容并联。

npn的饱和将会允许寄生pnp管开始工作,当npn饱和,bc结正偏,这也会使两个可能的寄生pnp中的其中一个的be结正偏,如图1.1.1b。

npn的基区现在也是衬底pnp的发射极,npn的外延是pnp 的基极,衬底是pnp的集电极。

在这种工作模式下,npn基区向外延注入空穴,这个空穴电流的一部分将会在外延复合掉。

不管怎样,相当多的空穴将会被衬底/隔离收集。

这些空穴来源于npn的正向基极电流,这个结果在npn饱和区Ie<Ic+Ib。

这个能被看作是将基极电流的一部分直接分流到衬底。

如果npn被在基极的一个低阻源驱动进入饱和区,寄生pnp将会引导大量的空穴电流到衬底。

半导体集成电路部分习题答案(朱正涌)

(1)当 时,欲使 =0.3V,驱动管应取何尺寸?

答:

7.2有一E/D NMOS反相器,若 =2V, =-2V, =25, =5V。

(1)求此反相器的逻辑电平是多少?

答:

第8章MOS基本逻辑单元

复习思考题

8.2图题8.2为一E/D NMOS电路。

(1)试问此电路可实现何种逻辑运算?

第13章集成运算放大器

13.2对于图题13.2所示差分对,设 =100, =0.7V,试求其 和 。

答:

9.5

13.4图题13.4为一个级联射耦对放大器,设 时, , , 。求:

(1) , 及 ;

(2) 和 (若 , )。

答:(1)

(2)

13.5已知射耦对差分放大器电路如图题13.5所示,晶体管的 , ,试求当 =130mV时的 值。

所示。

提示:先求截锥体的高度

-

然后利用公式: ,

注意:在计算W、L时,应考虑横向扩散。

2.3伴随一个情况下,哪一种偏置会使得寄生晶体管的影响最大?

答:当横向PNP管处于饱和状态时,会使得寄生晶体管的影响最大。

2.8试设计一个单基极、单发射极和单集电极的输出晶体管,要求其在20mA的电流负载下

由 画出隔离槽的四周;

验证所画晶体管的 是否满足 的条件,若不满足,则要对所作

的图进行修正,直至满足 的条件。( 及己知

)

第3章集成电路中的无源元件

复习思考题

3.3设计一个4kΩ的基区扩散电阻及其版图。

试求:(1)可取的电阻最小线宽 =?你取多少?

答:12μm

(2)粗估一下电阻长度,根据隔离框面积该电阻至少要几个弯头?

第二章集成电路中的晶体管及其寄生效应

耗尽层势垒电容Cj

(1)利用劳伦斯-沃纳曲线(该曲线是在耗尽 层近似和恒定衬底浓度的条件下获得的, 只能用来计算反偏的pn结)

劳伦斯-沃纳曲线

10

5

10 5 2 10 14

13

10 5 2 2 10 5 5 10 5 2

15 14

10 13 5

2 5 5

pF/2

pF/2

5

10

图形是窄条型);尽可能使集电区包围发射区 2、在工艺上采用增大结深及采用埋层工艺的办法

(1.1)横向PNP管的直流电流放大倍数

横向PNP本身结构上的限制

1、横向平均基区宽度不可能做得太小

2、发射极的注入效率低 3、表面复合影响大

(1.2)横向PNP管的特征频率fT

横向PNP管的有效基区宽度大 埋层的抑制作用,使折回集电极的少子路径增加 空穴的扩散系数只有电子扩散系数的1/3左右

尽可能使集电区包围发射区2在工艺上采用增大结深及采用埋层工艺的办法11横向pnp管的直流电流放大倍数11横向pnp管的直流电流放大倍数?横向pnp本身结构上的限制1横向平均基区宽度不可能做得太小2发射极的注入效率低3表面复合影响大12横向pnp管的特征频率ft?横向pnp管的有效基区宽度大?埋层的抑制作用使折回集电极的少子路径增加?空穴的扩散系数只有电子扩散系数的13左右提高横向pnp管的特征频率ft措施?增加结深xjc是否与工艺兼容?减小发射区尺寸?提高工艺精度减小等效基区宽度?降低外延层掺杂浓度提高横向pnp管发射区掺杂浓度是否与工艺兼容13横向pnp管开始发生大注入时的临界电流icr由晶体管原理

消除自锁现象的措施

消除自锁现象的版图设计; 消除自锁现象的工艺考虑; 其他措施:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

当发射结反偏(VBE<0),集电结也反偏(VBC<0) 时,为截止区。

当VBC>0 , VBE<0时,为反向工作区。工作 原理类似于正向工作区,但是由于集电区 的掺杂浓度低,因此其发射效率低, R 很小(约0.02)。

C

E N P N

B

反向工作区

共发射极的直流特性曲线

三个区域: 饱和区 放大区 截止区

V1 VT

S

IS

p I3 n I2

IB

V3 IC V2 V1

C

根据基尔霍夫定律,有:

IE IB I C I S 1 1 0 0 0 1 1 0 0 I1 0 I 2 1 I3 1

集成双极晶体管的有源寄生效应

NPN管工作于反向工作区的情况

几个假设:

晶体管参数

F 0 . 99 R 0 . 20 SF 0 . 70 SR 0 . 10

I ES 10 I CS 10

16 15 13

EM模型简化

A A A

PN 结正偏工作时, PN 结反偏工作时, V SC (V 3 ) 0 , I SS ( e V F 0, (e V R 0, (e

V1 VT

V2 VT

1) 1)

I 2 BI ES (e

B

1) I CS (e

V2 VT

IB

E

I

E

I1

N

P

N

IC

I2

C

V1

V2

A B

I1 I2 I2 I1

V 20 V 1 0

NPN管反向运用时 共基极短路电流增 益 I

E

IC IC IE

V 1 0

R

V 20

p n

I1 IE

E

理想本征集成双极晶体管的EM模型

三结四层结构(多结晶体管)

IE IB I C I S

1 1 F F 0

R 1R (1 SF ) SF

V1 VT I ES ( e 1) V2 SR I ( e VT 1 ) CS V 3 (1 SR ) I ( e VT 1 ) SS 1

正方向

V

二极管的等效电路模型

+ VD -

I I so (e

VD VT

1)

-

+

正向偏置

反向偏置

两结三层三极管(双结晶体管) 假设p区很宽,忽略两个PN结的相互作用,则:

B

IB

E

I DE I ES (e

IDC

N

V1 VT

1)

I

E

IDE

N

P

IC

C

V1

V2

I DC I CS (e

V2 VT

F

NPN管正向运用时 共基极短路电流增 益 理想本征集成双极晶体管的EM模型

BJT的三种组态

三结四层结构(多结晶体管) S

IS

V1 VT V2 VT

I1 I ES (e

V3 IC V2 V1

a

1) aI CS (e

V1 VT

1) 1) cI SS (e 1)

1

电子流

Ie=Ic+Ib 令 则

I c I e I cbo I e

空穴流

共射极短路电 流增益

Ic Ib

I e I p ( X 1 ) I n ( X 2 ) I b I p ( X 1 ) I rb I cbo

I c I n ( X 4 ) I cbo

b

I 2 V2 0 I1 V3 0

F SF

E

c

d

I 3 V2 0 I 2 V3 0

理想本征集成双极晶体管的EM模型

三结四层结构(多结晶体管)

I1 1 I2 R I 0 3 R 1 R I ES ( e 1) 0 V2 V R I CS ( e T 1) V 3 VT 1 I SS ( e 1)

集成双极晶体管的有源寄生效应

§2.4

集成双极晶体管的无源寄生效应

C

N+

B

N+

E

P+

P+

P

N-epi

N+-BL

E 发射极串联电阻rES rES=rE,c+ rE,b

接触电阻 体电阻

rE,c rE,b

发射区为N+扩散,杂质浓度在1020cm-3以上, 所以发射区的体电阻很小,串联电阻主要由 金属与硅的接触电阻决定

npn管

集成双极晶体管的有源寄生效应

NPN管工作于反向工作区的情况

E(n+) B(p) pnp S(p)

VBC (正偏) (反偏) 反向工作区 饱和区

npn

C(n)

(反偏) 截止区

(正偏) VBE 正向工作区

VBC>0 VBE<0 反向工作区 npn管

VEB_pnp=VBC_npn>0 VS=0 VCB_pnp<0 正向工作区 pnp管 寄生晶体管对电路产生影响

rC 1

T ln( a / b )

WL ab

集电极串联电阻rCS rCS=rC1+ rC2+rC3

C

E

rC2 LE-C

rC 2 R S BL

LE C W BL

集成双极晶体管的无源寄生效应

集电极串联电阻rCS rCS=rC1+ rC2+rC3

I E R I CS e

VBC VT

R I R

VBC VT

减小了集电极电流 作为无用电流流入衬底

减小 SF

I B (1 R ) I CS e

(1 R ) I R

VBC VT

I C (1 SF ) I CS e I S ' SF I CS e

V SC / V T

V F / VT

1) e

V F / VT

I SS 10

V R / VT

1) 1

1) I SS 0

集成双极晶体管的有源寄生效应

NPN管工作于反向工作区的EM方程(VBE(V1)<0,VBC(V2)>0)

IE IB I C I S 1 1 F F 0 R 1R (1 SF ) SF

VBC VT

(1 SF ) I R

SF I R

采用埋层和掺金工艺

集成双极晶体管的有源寄生效应

NPN管工作于饱和工作区的情况

E(n+) B(p) pnp S(p)

VBC (正偏) (反偏) 反向工作区 饱和区

npn

C(n)

(反偏) 截止区

(正偏) VBE 正向工作区

VBC>0 VBE>0 饱和工作区

V1 VT I ES ( e 1) V2 SR I ( e VT 1 ) CS V 3 (1 SR ) I ( e VT 1 ) SS 1

0

IE IB I C I S

1 1 F F 0

VEB_pnp=VBC_npn>0 VS=0 VCB_pnp<0

正向工作区

pnp管 寄生晶体管对电路产生影响

npn管

集成双极晶体管的有源寄生效应

NPN管工作于饱和工作区的EM方程

IE IF RIR I B (1 F ) I F (1 R ) I R I C F I F (1 SF ) I R I S ' SF I R

R 1R (1 SF ) SF

I ES V BC SR V I CS e T (1 SR ) I SS 1 0

集成双极晶体管的有源寄生效应

NPN管工作于反向工作区的EM方程

IE IB I C I S 1 1 F F 0 R 1R (1 SF ) SF I ES V BC SR V I CS e T (1 SR ) I SS 1 0

V1

(反偏)

截止区

E

正向工作区

NPN管工作于正向工作区和截止区的情况

E(n+) B(p) pnp S(p)

VBC (正偏) (反偏) 反向工作区 饱和区

npn

C(n)

(反偏) 截止区

(正偏) VBE 正向工作区

VBC<0 正向工作区和截止区

VEB_pnp<0 VS=0 VCB_pnp<0

截止

pnp管 寄生晶体管的影响可以忽略

1)

理想本征集成双极晶体管的EM模型

实际双极晶体管的结构 由两个相距很近的PN结组成:

发 射 极 发 射 基区 结 收 集 结 集 电 极

发射区

集电区

基极

基区宽度远远小于少子扩散长度,相邻PN结 之间存在着相互作用

两结三层三极管(双结晶体管)

I1 I ES (e

V1 VT

1) AI CS (e

2.2

理想本征集成双极晶体管的EM模型

一结两层二极管(单结晶体管)

P-Si