32位除法器的设计

电路中的除法器设计

电路中的除法器设计在电路设计中,除法器是一种十分重要的组件。

它可以将输入的数字进行除法运算,将商和余数输出。

除法器在计算机和数字信号处理器等电子设备中被广泛使用,因此其设计和优化具有重要意义。

一、除法器的基本原理除法运算是一种复杂的运算,要实现除法器的设计,首先需要了解其基本原理。

除法器的基本原理是通过移位和减法实现的。

在将被除数和除数输入除法器后,除法器将被除数和除数进行比较,并开始迭代过程。

在每一次迭代中,被除数的位数向左移动,直到其高位与除数相等或超过除数。

然后,除法器进行减法操作,将除数减去被除数,结果作为商的一位。

此后,商持续左移,被减数保持不变,重复上述过程,直到所有的商位都得出。

二、除法器的设计策略在除法器的设计中,有几种常见的策略可以考虑。

1. 组合逻辑除法器:这种类型的除法器使用组合逻辑电路实现,通过减法器、比较器和移位器等组件的组合来实现除法运算。

组合逻辑除法器的优点是速度较快,但缺点是占用较多的电路资源。

2. 串行逻辑除法器:与组合逻辑除法器相反,串行逻辑除法器使用顺序逻辑电路实现。

它通过一个时钟信号,逐位地进行计算,因此典型的串行逻辑除法器速度较慢。

但串行逻辑除法器更节省电路资源,因此在一些资源有限的场景中得到了广泛应用。

3. 重复系列除法器:这种除法器通过多个并行的子除法器实现,并行计算多个位的商。

重复系列除法器具有较高的性能,但需要更多的电路资源和功耗。

三、除法器的优化方法为了提高除法器的性能和效率,可以采用一些优化方法。

1. 位级并行思路:通过将除法器分解为多位的子除法器,并行计算多个子除法器,可以大幅提高除法器的速度。

这种方法在重复系列除法器中得到了广泛应用。

2. 乘法相关技巧:利用乘法器计算除法运算,可以加速除法器的运算速度。

通过将除数进行逆运算,转化为乘法操作,可以利用乘法器的高速性能,提升除法器的效率。

3. 进制转换思想:将数字进行二进制到十进制的转换,然后进行简单的除法运算,可以减少运算的复杂程度,提高除法器的运算速度。

32位算术逻辑运算单元

32位算术逻辑运算单元32位算术逻辑运算单元(ALU)是计算机体系结构中的一个关键组件,它执行计算机中的算术和逻辑运算。

它通常由多个逻辑门和寄存器组成,用于执行加法、减法、逻辑与、逻辑或等运算。

在本文中,我将详细介绍32位ALU的工作原理和设计。

首先,让我们了解一下什么是32位ALU。

它是一种具有32个位的数据运算单元,用于处理32位的二进制数据。

每个位都可以表示0或1,并且可以进行各种二进制运算。

这些运算可以是算术运算,如加法和减法,也可以是逻辑运算,如逻辑与、逻辑或和逻辑非等。

32位ALU的核心部分是一组逻辑门,包括与门、或门、非门等。

这些逻辑门通过电路连接在一起,实现了不同的运算。

例如,对于算术加法运算,ALU使用一组全加器电路来执行。

每个全加器将输入的两个位和进位位相加,并生成和位和进位位。

这些和位和进位位将传递给下一个全加器,直到所有位都被加起来。

最后,将得到的和位作为结果输出。

除了算术运算,32位ALU还可以执行逻辑运算。

例如,对于逻辑与运算,ALU使用一组与门来执行。

它将输入的两个位分别与对应的两个位进行逻辑与运算,并得到一个结果位。

这些结果位将传递给下一个与门,直到所有位都被运算。

最后,得到的结果位将作为运算结果输出。

在32位ALU中,还有一些其他重要的组件。

其中之一是寄存器,用于存储运算结果和其他中间结果。

寄存器是一种能够存储和读取数据的高速存储器。

它通常由触发器组成,可以在时钟信号的作用下保持数据的稳定性。

寄存器在ALU中用于存储运算结果,并将其传递给其他部分进行处理。

另一个重要的组件是控制单元。

控制单元负责控制ALU的操作和流程。

它接收指令和数据,并根据指令的类型和操作码来决定执行何种运算。

控制单元还可以控制ALU的时钟信号和寄存器的读写操作。

它基于计算机指令的解码和执行机制来实现这些功能。

在设计32位ALU时,需要考虑的因素有很多。

首先是电路的优化和性能。

ALU需要在非常短的时间内完成运算,并且需要具有高的稳定性和可靠性。

32位加减法器设计2010012107季涛

带有溢出标志的32位加减法器的设计2010012107 季涛加法器是一个非常基本的数字运算电路,经常出现在数字电路的关键路径中。

本次作业实现的加减法器一共要实现五个基本功能:1)求补2)无符号数的加法3)无符号数的减法4)有符号数的加法5)有符号数的减法,同时对应每种功能还要给出对应的溢出标志。

虽然看起来功能有五种,但是核心的模块还是一个32位的加法器。

现在比较流行的加法器结构有很多,从最基本的一位半加器、全加器,到多位的行波进位加法器,曼彻斯特进位链加法器,旁路进位加法器,超前进位加法器,选择进位加法器,到更复杂的更多位的树结构表示的加法器,如Brent-Kung树、Kogge-Stone树等等。

由于想要实现一个速度较快的加法器,所以一般会选择后几种类型的结构,然后我之前的课程里已经实现过了超前进位加法器、Brent-Kung树结构前置进位加法器,所以本次作业我选择了Kogge-Stone树。

它的主要特点是:能获得log2N的级数,每级的扇出为2,代价是级间布线有很多的长线,PG单元更多。

Kogge-Stone树结构图如下:结构框图如下:设计的思路是这样的,求补的话就是对操作数进行取反然后+1,令加法器的一个输入为1,另一个输入为~a即可;无符号数和有符号数的加法的输入是一样的;减法的时候只要对第二个操作数求补即可。

然后溢出标志的获取我是对四种功能分别考虑,无符号数的加法,只有在最高位的进位信号为1的时候表示超过了数的表示范围,溢出信号为1,其余情况都为0;无符号数的减法只有在第一个操作数比第二个操作数小的时候溢出信号为1,其余为0;有符号数的加法只有在两个操作数的符号相同而和的最高位符号与他们不同时为1.其余为0;有符号数的减法只有在两个操作数的符号位不同而差的最高位和第二个操作数符号位相同时为1,其余为0。

这样就基本实现了功能。

总结:第一次作业主要让我又回顾了modelsom、DC等软件的使用方法,时隔一年没用有些东西确实都生疏了,甚至安装modelsim软件、DC综合的过程中也产生了不少问题,好在在同学和助教姐姐的帮助下都克服了困难。

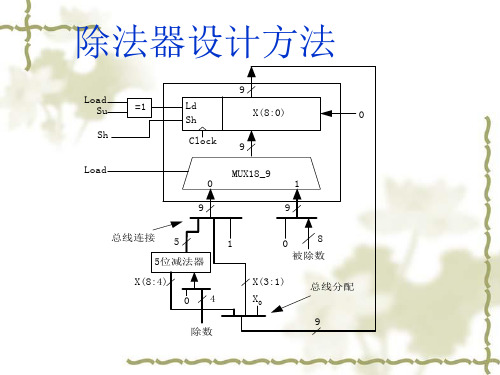

除法器设计方法

controlsignals:process(T,I,X,Y)

--状态控制进程

begin

Extern<='0';Done<='0';Ain<='0';Gin<='0';

Gout<='0';AddSub<='0';Rin<="0000";Rout<="0000";

case T is

when "00"=>

update:process(clk)

--同步数据更新进程

begin

if(clk='1'and clk'event) then

state<=nextstate;

if load='1' then

dividend<='0'÷nd_in;

end if;

if su='1' then

dividend(8 downto 4)<=subout;

end proc;

architecture Behavioral of proc is

component upcount

--计数器元件声明

Port ( Clear,Clock : in std_logic;

Q : buffer std_logic_vector(1 downto 0));

end component;

signal subout:std_logic_vector(4 downto 0);

signal dividend:std_logic_vector(8 downto 0);

基于 FPGA的32位除法器设计

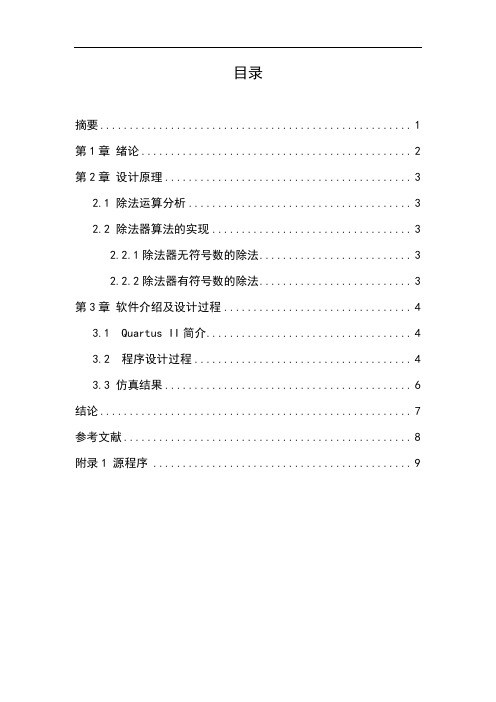

目录摘要 (1)第1章绪论 (2)第2章设计原理 (3)2.1 除法运算分析 (3)2.2 除法器算法的实现 (3)2.2.1除法器无符号数的除法 (3)2.2.2除法器有符号数的除法 (3)第3章软件介绍及设计过程 (4)3.1 Quartus II简介 (4)3.2 程序设计过程 (4)3.3 仿真结果 (6)结论 (7)参考文献 (8)附录1 源程序 (9)摘要介绍了一种使用可编程逻辑器件FPGA和VHDL语言实现32位除法器的设计方法。

该除法器不仅可以实现有符号数运算,也可以实现无符号数的运算。

除法器采用节省FPGA逻辑资源的时序方式设计,主要由移位、比较和减法三种操作构成。

由于优化了程序结构,因此程序浅显易懂,算法简单,不需要分层次分模块进行。

并使用Altera公司的QuartusⅡ软件对该除法器进行编译、仿真,得到了完全正确的结果。

关键词:FPGA;VHDL;除法器;减法;移位第1章绪论EDA 技术就是以计算机为工具,设计者在 EDA 软件平台上,用硬件描述语言 VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA 技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

VHDL是一种全方位的硬件描述语言,包括系统行为级、寄存器传输级和逻辑门级多个设计层次,支持结构、数据流和行为 3 种描述形式的混合描述,因此 VHDL几乎覆盖了以往各种硬件描述语言的功能,整个自顶向下或自底向上的电路设计过程都可以用 VHDL来完成。

另外,VHDL还有以下优点:VHDL的宽范围描述能力使它成为高层次设计的核心,将设计人员的工作重心转移到了系统功能的实现和调试上,只需要花较少的精力用于物理实现;VHDL可以用简洁明确的代码描述来进行复杂控制逻辑的设计,灵活且方便,而且也便于设计结果的交流、保存和重用;VHDL的设计不依赖于特定的器件,方便了工艺的转换。

数字系统设计32位进位选择加法器设计

1、12进位选择加法器原理图32位进位选择加法器原理图仅仅是将12位进位选择加法器原理图中虚线框内的模块再向后重复5次,这就构成了32位进位选择加法器原理图。

2、Verilog模块根据上图可以将进位选择加法器在结构上分为四个模块:①四位先行进位加法器adder_4bits②四位数据选择器mux_2to1③高四位选择加法器(虚线框内部分)adder_high_4bits④顶层设计32位进位选择加法器adder_32_bits3、Verilog代码# 四位先行进位加法器module adder_4bits(a,b,s,ci,co);parameter N=4;input[N-1:0] a;input[N-1:0] b;input ci;output[N-1:0] s;output co;wire [N-1:0] c;wire [N-1:0] g;wire [N-1:0] p;assign g=a&b;assign p=a|b;assign c[0]=g[0]||(p[0]&&ci);assign c[1]=g[1]||(p[1]&&g[0])||(p[1]&&p[0]&&ci);assign c[2]=g[2]||(p[2]&&g[1])||(p[2]&&p[1]&&g[0])||(p[2]&&p[1]&&p[0]&&ci);assignc[3]=g[3]||(p[3]&&g[2])||(p[3]&&p[2]&&g[1])||(p[3]&&p[2]&&p[1]&&g[0])||(p[3]&&p[2]&&p[1]&&p[0]&&ci);assign s[0]=p[0]&~g[0]^ci;assign s[1]=p[1]&~g[1]^c[0];assign s[2]=p[2]&~g[2]^c[1];assign s[3]=p[3]&~g[3]^c[2];assign co=c[3];endmodule# 四位数据选择器module mux_2to1 (out,in0,in1,sel);parameter N=4;output[N:1] out;input[N:1] in0,in1;input sel;assign out=sel?in1:in0;endmodule# 高四位选择加法器module adder_high_4bits(a,b,ci,co,s);parameter N=4;input[N-1:0] a;input[N-1:0] b;input ci;output[N-1:0] s;output co;wire [N-1:0] sum1,sum0;wire co1,co0,cand;adder_4bits #(4) adder_1(.a(a),.b(b),.s(sum1),.ci(1'b1),.co(co1)); adder_4bits #(4) adder_2(.a(a),.b(b),.s(sum0),.ci(1'b0),.co(co0)); mux_2to1 #(4) mux1(.in0(sum0),.in1(sum1),.sel(ci),.out(s)); and G1(cand,ci,co1);or G2(co,cand,co0);endmodule# 顶层设计32位进位选择加法器module adder_32bits(a,b,s,ci,co);parameter N=32;input [N-1:0] a;input [N-1:0] b;input ci;output [N-1:0] s;output co;wire co1,co2,co3,co4,co5,co6,co7;adder_4bits #(4) adder1(.a(a[3:0]),.b(b[3:0]),.ci(ci),.s(s[3:0]),.co(co1));adder_high_4bits #(4) adder2(.a(a[7:4]),.b(b[7:4]),.ci(co1),.s(s[7:4]),.co(co2));adder_high_4bits #(4) adder3(.a(a[11:8]),.b(b[11:8]),.ci(co2),.s(s[11:8]),.co(co3));adder_high_4bits #(4) adder4(.a(a[15:12]),.b(b[15:12]),.ci(co3),.s(s[15:12]),.co(co4));adder_high_4bits #(4) adder5(.a(a[19:16]),.b(b[19:16]),.ci(co4),.s(s[19:16]),.co(co5));adder_high_4bits #(4) adder6(.a(a[23:20]),.b(b[23:20]),.ci(co5),.s(s[23:20]),.co(co6));adder_high_4bits #(4) adder7(.a(a[27:24]),.b(b[27:24]),.ci(co6),.s(s[27:24]),.co(co7));adder_high_4bits #(4) adder8(.a(a[31:28]),.b(b[31:28]),.ci(co7),.s(s[31:28]),.co(co)); endmodule4、仿真结果①四位先行进位加法器进行仿真,结果如下如图所示,a=0101,b=1010,ci=1;sum=0000,cout=1;仿真正确。

位可控加减法器设计32位算术逻辑运算单元

位可控加减法器设计32位算术逻辑运算单元标题:深入探讨位可控加减法器设计中的32位算术逻辑运算单元一、引言在计算机系统中,算术逻辑运算单元(ALU)是至关重要的部件,用于执行数字运算和逻辑运算。

而在ALU中,位可控加减法器设计是其中的重要部分,尤其在32位算术逻辑运算单元中更是不可或缺。

本文将深入探讨位可控加减法器设计在32位算术逻辑运算单元中的重要性,结构特点以及个人观点和理解。

二、位可控加减法器设计的重要性位可控加减法器是ALU中的重要组成部分,它具有对加法和减法操作进行控制的能力,可以根据输入信号来实现不同的运算操作。

在32位算术逻辑运算单元中,位可控加减法器的设计要考虑到对每一位进行并行操作,并且要保证高速、低功耗和稳定性。

位可控加减法器设计在32位算术逻辑运算单元中具有非常重要的意义。

三、位可控加减法器设计的结构特点在32位算术逻辑运算单元中,位可控加减法器的设计需要考虑到以下几个结构特点:1. 并行运算:位可控加减法器需要能够实现对32位数据的并行运算,以提高运算速度。

2. 控制信号:设计需要合理的控制信号输入,来实现不同的运算模式和操作类型。

3. 进位传递:保证进位信号能够正确传递和计算,以确保运算的准确性。

4. 低功耗:设计需要考虑到低功耗的特点,以满足现代计算机系统对能源的需求。

四、个人观点和理解在我看来,位可控加减法器设计在32位算术逻辑运算单元中扮演着十分重要的角色。

它不仅需要具备高速、稳定和精确的运算能力,还需要考虑到功耗和控制信号的合理设计。

只有兼具这些特点,才能更好地满足现代计算机系统对于高效、可靠和低功耗的需求。

五、总结和回顾通过本文对位可控加减法器设计在32位算术逻辑运算单元中的深入探讨,我们可以看到它在计算机系统中的重要性和结构特点。

而个人观点也表明了它需要具备高速、低功耗和稳定性等特点,才能更好地满足现代计算机系统的需求。

在写作过程中,我对位可控加减法器设计在32位算术逻辑运算单元中的重要性和结构特点进行了深入探讨,并分享了个人观点和理解。

基于 FPGA的32位除法器设计汇总

目录摘要 (1)第1章绪论 (2)第2章设计原理 (3)2.1 除法运算分析 (3)2.2 除法器算法的实现 (3)2.2.1除法器无符号数的除法 (3)2.2.2除法器有符号数的除法 (3)第3章软件介绍及设计过程 (4)3.1 Quartus II简介 (4)3.2 程序设计过程 (4)3.3 仿真结果 (6)结论 (7)参考文献 (8)附录1 源程序 (9)摘要介绍了一种使用可编程逻辑器件FPGA和VHDL语言实现32位除法器的设计方法。

该除法器不仅可以实现有符号数运算,也可以实现无符号数的运算。

除法器采用节省FPGA逻辑资源的时序方式设计,主要由移位、比较和减法三种操作构成。

由于优化了程序结构,因此程序浅显易懂,算法简单,不需要分层次分模块进行。

并使用Altera公司的QuartusⅡ软件对该除法器进行编译、仿真,得到了完全正确的结果。

关键词:FPGA;VHDL;除法器;减法;移位第1章绪论EDA 技术就是以计算机为工具,设计者在 EDA 软件平台上,用硬件描述语言 VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA 技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

VHDL是一种全方位的硬件描述语言,包括系统行为级、寄存器传输级和逻辑门级多个设计层次,支持结构、数据流和行为 3 种描述形式的混合描述,因此 VHDL几乎覆盖了以往各种硬件描述语言的功能,整个自顶向下或自底向上的电路设计过程都可以用 VHDL来完成。

另外,VHDL还有以下优点:VHDL的宽范围描述能力使它成为高层次设计的核心,将设计人员的工作重心转移到了系统功能的实现和调试上,只需要花较少的精力用于物理实现;VHDL可以用简洁明确的代码描述来进行复杂控制逻辑的设计,灵活且方便,而且也便于设计结果的交流、保存和重用;VHDL的设计不依赖于特定的器件,方便了工艺的转换。