常规阻抗设计参数

阻抗设计制作规范

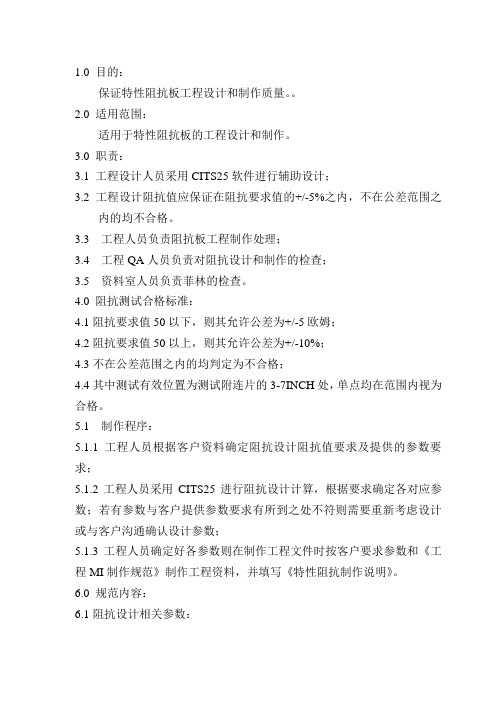

1.0 目的:保证特性阻抗板工程设计和制作质量。

2.0 适用范围:适用于特性阻抗板的工程设计和制作。

3.0 职责:3.1 工程设计人员采用CITS25软件进行辅助设计;3.2 工程设计阻抗值应保证在阻抗要求值的+/-5%之内,不在公差范围之内的均不合格。

3.3 工程人员负责阻抗板工程制作处理;3.4 工程QA人员负责对阻抗设计和制作的检查;3.5 资料室人员负责菲林的检查。

4.0 阻抗测试合格标准:4.1阻抗要求值50以下,则其允许公差为+/-5欧姆;4.2阻抗要求值50以上,则其允许公差为+/-10%;4.3不在公差范围之内的均判定为不合格;4.4其中测试有效位置为测试附连片的3-7INCH处,单点均在范围内视为合格。

5.1 制作程序:5.1.1工程人员根据客户资料确定阻抗设计阻抗值要求及提供的参数要求;5.1.2工程人员采用CITS25进行阻抗设计计算,根据要求确定各对应参数;若有参数与客户提供参数要求有所到之处不符则需要重新考虑设计或与客户沟通确认设计参数;5.1.3工程人员确定好各参数则在制作工程文件时按客户要求参数和《工程MI制作规范》制作工程资料,并填写《特性阻抗制作说明》。

6.0 规范内容:6.1阻抗设计相关参数:6.1.1介质层厚度与介电常数(生益材料):如果介质在HOZ和1OZ铜箔之间,其厚度按HOZ情况计算。

半固化片的计算6.1.1.2芯板厚度参数表:6.1.1.3介电常数:不同的组合介质、厚度介电常数:对介电常数的取值,要关键看其介质的厚度来对应查找其对应的介电常数,可以按最接近的原则进行选择。

如果客户提供板材,则按客户客户提供板材的介电常数取值。

6.1.2线宽/线距常规下侧蚀因子在2.0~2.5左右。

为了方便计算,在常规板制作计算时,使用计算线宽如下表:(对于非常规铜厚时则需要参考侧蚀因子进行计算及与工艺人员进行确认)。

使用计算间距为客户设计间距。

(注:W0=客户设计线宽)6.1.3铜厚常规下,内层基铜厚为1OZ、0.5OZ,外层基铜铜厚为HOZ。

制作阻抗设计原则

制作阻抗设计原则一.影响阻抗值的因素:<1> 介电质常数,与阻抗值成反比 [Er 值愈高 , Z0值愈低]<2> 线路层与垫地层间介电层厚度,与阻抗值成正比,参考基板及PP 之压合厚度 [介层愈厚 , Z0值愈高]<3> 线宽,与阻抗成反比 [线宽愈细 , Z0值愈高] <4> 铜厚,与阻抗值成反比 [铜愈厚 , Z0值愈低]=>内层为基板铜厚,厂内1OZ=1.2 MIL,外层为铜箔厚度+镀铜厚度 (ie.依据孔铜规格而定,孔铜min0.8时铜后取1.7mil)<5> 差动阻抗相邻线路与线路之间的间距,与阻抗值成正比 [Spacing 愈小 , Z0值愈低] <6> 线路层与线路层间介电层厚度,与阻抗值成反比 <7> 防焊漆厚度,与阻抗值成反比[绿漆愈厚 , Z0值愈低]二. 阻抗 Type 说明1.特性阻抗计算:1.1.Surface Microstrip1.2. Coated Microstrip1.3.Embedded Microstrip1.4. Symmetrical Microstrip1.5. Offset stripline2.差动阻抗计算:2.1. Edge-coupled Surface Microstrip2.2.Edge-coupled Coated Microstrip2.3.Edge-coupled Embedded Microstrip2.5.Edge-coupled Offset stripline3. Coplanar 阻抗计算:3.1 Surface Coplanar Line3.2 Coated Coplanar Line3.3 Embedded Coplanar Line3.4 Offset Coplanar Stripline。

阻抗设计方案及范例

阻抗设计方案及范例

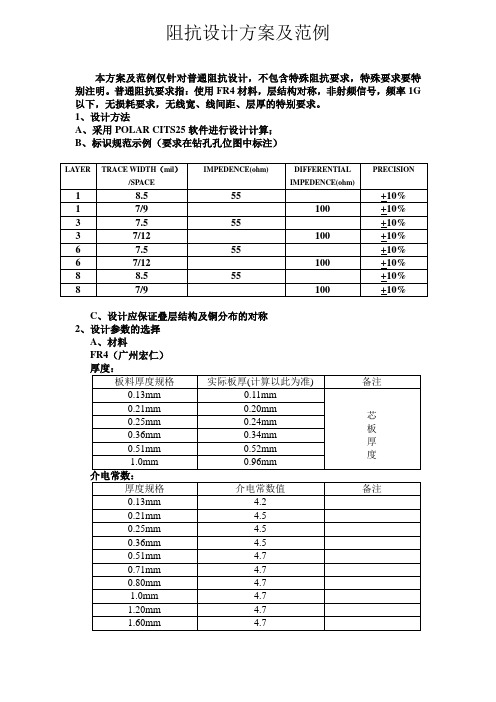

本方案及范例仅针对普通阻抗设计,不包含特殊阻抗要求,特殊要求要特别注明。

普通阻抗要求指:使用FR4材料,层结构对称,非射频信号,频率1G 以下,无损耗要求,无线宽、线间距、层厚的特别要求。

1、设计方法

A、采用POLAR CITS25软件进行设计计算;

B、标识规范示例(要求在钻孔孔位图中标注)

C、设计应保证叠层结构及铜分布的对称

2、设计参数的选择

A、材料

FR4(广州宏仁)

半固化片

B、线宽按中值(以D表示)的+/-0.5mil计算(即W=D-0.5mil,W1=D+0.5mil).

C

D、阻焊层厚度按10um为准.(选择盖阻焊模式)

3、参数调整

调整优先顺序为:介质层厚度、线间距、线宽。

任何参数的调整均要求与客户做沟通确认。

调整时注意满足总板厚及公差的要求

4、阻抗测试:

要求做阻抗测试的板在工程处理时在板边制作附连片,模拟要求控制的阻抗线路,对其进行测量,取其中4~7inch的值,通过判断其是否在客户要求阻抗值及公差以确定合格品。

范例:

以下提供各种范例以供设计参考:。

阻抗制作规范

规范制作阻抗PCB的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定。

2、适用范围:

适用于本厂客户要求阻抗控制的PCB的阻抗设计及之CAM制作的阻抗图形设计。

3、名词解释:

3.1特性阻抗(Characteristic Impedance):当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

7.2.9外层方形PAD对应接地层为Thermal Pad或直接与铜面导通。

7.2.10线宽/线距必须符合流程单要求。

7.2.11两层板设计如下:

6.2.12四层板设计如下:

7.2.13六层板设计如下:

7.2.14八层板设计如下:

ቤተ መጻሕፍቲ ባይዱ7.3特殊阻抗设计:

特殊阻抗设计时除了一般注意事项以外须根据实际情况进行修改。

4.3.3特性阻抗:成品60欧姆±10%

4.3.3.1要求理论值计算特性阻抗控制的范围为60欧姆±8%:

4.3.3.2产品的制作参数要求如下:

1)客户原本设计的特性阻抗线线宽:150um,

2)客户原本设计的与特性阻抗线相邻的线距最小为:100um

3)与特性阻抗线相邻的介层的厚度要求为:105um±15um

RC% 68压合后的介质厚度为71±8UM,RC%62压合后的介质厚度为65±8UM

5)当选用几种Prepreg同时压合时,则采用最高的介电常数与最低的介电常数的平均值进行计算。

6)内层板材铜厚计算数据:

板材铜厚是70um用62um计算,板材铜厚是35um用30um计算,板材铜厚是18um用16um计算.

3) 2116 Prepreg

A、介电常数为4.3±0.2

B、压合后的介质厚度为(内层100%残铜理论值):

PCB阻抗设计参考

PCB阻抗设计参考在PCB设计中,阻抗是一个非常重要的参数,尤其对于高频信号传输和数字信号传输。

正确设计PCB阻抗可以确保信号的稳定传输和减少信号衰减。

一般来说,要设计PCB的阻抗,需要考虑以下几个方面:1.材料特性:首先要了解所使用的PCB板材的介电常数和介磁常数。

这些参数会对阻抗产生影响,例如常用FR-4板材的介电常数在4.2~4.5之间。

2.PCB层结构:多层板的设计中,每一层的布线方式会影响阻抗。

通过选择合适的层次安排来控制阻抗。

两层板可以使用不同的宽度和间距的微带线或者分界线以控制阻抗,而对于多层板可以考虑使用阵列线、共面线、差分线等方式控制阻抗。

3. 线宽和间距的选择:根据所需的阻抗值和PCB的板厚,可以通过一些公式来选择合适的线宽和间距。

常用的公式有美国电气工程协会(IEEE)和Roger Ghirardi等提出的公式。

4.主要参数计算:对于常用的阻抗控制线如微带线、分界线和差分线,可以根据它们的几何特性和材料参数计算出所需的阻抗。

例如对于一条微带线,阻抗可以根据线宽、线距、介电常数等参数,使用公式计算得出。

5.仿真工具:使用仿真工具对阻抗进行验证也是一种常用的方法。

通过在仿真软件中建立PCB的模型,可以模拟信号在PCB中的传输情况,从而验证设计所得阻抗的准确性。

6.实际布局:在进行实际布局时,要确保实际线宽和间距与设计要求相符。

可以使用追踪宽度测量工具来检查PCB上的线宽,并使用追踪间距工具来检查线间距。

此外,还要注意信号线和地线的排列,以尽可能减小信号线的距离地线的距离。

通过合理的PCB阻抗设计,可以使得信号在PCB上得到稳定传输,减少信号衰减,提高系统的性能和可靠性。

(注:此回答基于2024年的知识,并不包括当前最新的技术和趋势,如有需要请参考最新资料和指导。

阻抗设计

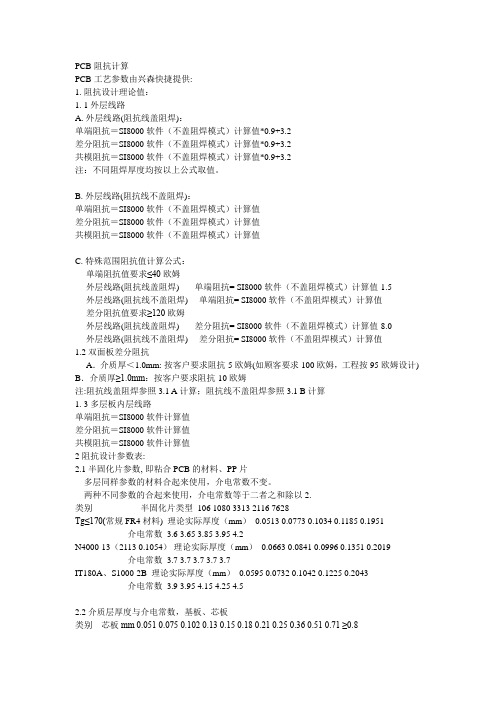

PCB阻抗计算PCB工艺参数由兴森快捷提供:1. 阻抗设计理论值:1. 1 外层线路A. 外层线路(阻抗线盖阻焊):单端阻抗=SI8000软件(不盖阻焊模式)计算值*0.9+3.2差分阻抗=SI8000软件(不盖阻焊模式)计算值*0.9+3.2共模阻抗=SI8000软件(不盖阻焊模式)计算值*0.9+3.2注:不同阻焊厚度均按以上公式取值。

B. 外层线路(阻抗线不盖阻焊):单端阻抗=SI8000软件(不盖阻焊模式)计算值差分阻抗=SI8000软件(不盖阻焊模式)计算值共模阻抗=SI8000软件(不盖阻焊模式)计算值C. 特殊范围阻抗值计算公式:单端阻抗值要求≤40欧姆外层线路(阻抗线盖阻焊) 单端阻抗= SI8000软件(不盖阻焊模式)计算值-1.5外层线路(阻抗线不盖阻焊) 单端阻抗= SI8000软件(不盖阻焊模式)计算值差分阻抗值要求≥120欧姆外层线路(阻抗线盖阻焊) 差分阻抗= SI8000软件(不盖阻焊模式)计算值-8.0外层线路(阻抗线不盖阻焊) 差分阻抗= SI8000软件(不盖阻焊模式)计算值1.2 双面板差分阻抗A.介质厚<1.0mm: 按客户要求阻抗-5欧姆(如顾客要求100欧姆,工程按95欧姆设计) B.介质厚≥1.0mm:按客户要求阻抗-10欧姆注:阻抗线盖阻焊参照3.1 A计算;阻抗线不盖阻焊参照3.1 B计算1. 3 多层板内层线路单端阻抗=SI8000软件计算值差分阻抗=SI8000软件计算值共模阻抗=SI8000软件计算值2 阻抗设计参数表:2.1 半固化片参数, 即粘合PCB的材料、PP片多层同样参数的材料合起来使用,介电常数不变。

两种不同参数的合起来使用,介电常数等于二者之和除以2.类别半固化片类型106 1080 3313 2116 7628Tg≤170(常规FR4材料) 理论实际厚度(mm)0.0513 0.0773 0.1034 0.1185 0.1951介电常数3.6 3.65 3.85 3.95 4.2N4000-13(2113 0.1054)理论实际厚度(mm)0.0663 0.0841 0.0996 0.1351 0.2019 介电常数3.7 3.7 3.7 3.7 3.7IT180A、S1000-2B 理论实际厚度(mm)0.0595 0.0732 0.1042 0.1225 0.2043介电常数3.9 3.95 4.15 4.25 4.52.2 介质层厚度与介电常数,基板、芯板类别芯板mm 0.051 0.075 0.102 0.13 0.15 0.18 0.21 0.25 0.36 0.51 0.71 ≥0.8Mil 2 3.0 4 5.1 5.9 7.0 8.27 10 14.5 20 28 ≥31.5Tg≤170 介电常数3.6 3.65 3.95 3.95 3.65 4.2 3.95 3.95 4.2 4.1 4.2 4.2IT180A、S1000-2 介电常数3.9 3.95 4.25 4.25 3.95 4.5 4.25 4.25 4.5 4.4 4.5 4.52.3 铜厚基铜厚内层铜厚度(mil)外层图镀工艺铜厚度(mil)外层工艺会在基铜上再次镀铜外层负片工艺铜厚度(mil)内层 18um/0.5OZ 0.65内层 35um/1OZ 1.25内层 70um 2.56外层 12um 2外层 18um/0.5OZ 2.2外层 35um/1OZ 2.92.4 线宽/线距基铜厚上线宽(mil)下线宽(mil)线距(mil)内层 18um W0-0.1 W0 S0内层 35um W0-0.4 W0 S0内层 70um W0-1.2 W0 S0外层 12um W0-0.6 W0+0.6 S0-0.6外层 18um W0-0.6 W0+0.7 S0-0.7外层 35um W0-0.9 W0+0.9 S0-0.9注:其中 W0 为顾客设计线宽,S0 为顾客设计线距。

使用SI9000进行PCB常规阻抗计算

SI9000常规阻抗计算常规信号分为微带线与带状线,微带线指该信号线只有一个参考平面(表底层),带状线指该信号线在两个参考平面之间(内层),故阻抗计算需要选择不同模型来完成。

一、外层(微带线)单端阻抗计算模型1、单端阻抗结构——>2、单端阻抗模型——>3、设置相应参数说明:介电常数与板材有关,常规FR4介电常数在4、2—4、5之间,常规半固化片介电常数106(3、9)、1080(4、2)、2116(4、2)、7628(4、5),罗杰斯板材RO4350B介电常数就是3、66,M6板材介电常数在3、3-3、5之间.二、外层(微带线)差分阻抗计算模型1、差分阻抗结构-—>2、差分阻抗模型——>3、设置相应参数说明:常规差分控制阻抗100ohm,USB控90ohm,Typec控90oh m以下就是1、6mm板厚常规八层板得层叠1、 3个信号层、2个地、一个电源2、射频隔层参考,线宽16mil3、关键信号在S1层,注意S2跨分割问题,适用于杂线多得情况A.根据微带线单端模型50ohm阻抗计算如下(线宽6):B。

根据微带线差分模型阻抗计算如下:1、单端阻抗结构-->2、单端阻抗模型—-〉3、设置相应参数1、差分阻抗结构-—>2、差分阻抗模型——>3、设置相应参数根据常规8层板层叠计算内层阻抗、A。

内层单端阻抗模型:S1:H1=16+1、2+4、3=21、5H2=1、2+4、3=5、5S1层50ohm:5mil(说明:阻抗允许误差正负10%,H1与H2数值)S1与S2参考层面厚度相差较小阻抗线宽一致(说明:如果H1与H2数值正确,H1与H2即使颠倒,阻抗变化很小)S2:H1=4、3ﻩ H2=1、2+16+1、2+4、3=22、7S2层50ohm:5milS3:H1=4、3H2=1、2+16=17、2S3层50ohm:5milB.内层差分阻抗模型(介质厚度与单端阻抗一致):S1:H1=16+1、2+4、3=21、5H2=1、2+4、3=5、5S2:H1=4、3ﻩ H2=1、2+16+1、2+4、3=22、7S3:H1=4、3H2=1、2+16=17、2S1、S2、S3:90ohmS1、S2、S3:100ohm同理计算,概不赘述.(关于射频线阻抗计算隔层参考,共面阻抗计算参考<SI9000隔层及共面模型计算>)阻抗说明:叠层厚度通常由单板实际情况决定,如果叠层确定,线宽变小,阻抗变大,差分阻抗线之间得间距变大,阻抗变大,差分100ohm计算时,可通过改变线宽与间距实现(注意:建议差分间距不要大于2倍线宽如4得线宽8得间距).单端阻抗主要依靠改变线宽实现。

电源阻抗合理范围

电源阻抗合理范围全文共四篇示例,供读者参考第一篇示例:电源阻抗是指电源对外部电路提供电能时所表现出的特性,是电源本身对外部电路的交流电阻。

在实际电路设计中,电源阻抗的选择对于整个电路的稳定性和性能起着非常重要的作用。

合理的电源阻抗可以保证电路的正常工作,提高电路的效率和可靠性。

电源阻抗的合理范围是指在一定的规定范围内,电源阻抗应该处于一个适当的数值范围内,以保证电路的正常工作。

电源阻抗的合理范围通常取决于电路的工作频率、电源类型以及电路的设计要求等因素。

在实际的电路设计中,电源阻抗的合理范围可以通过具体的计算和分析来确定。

一般来说,在低频电路中,电源阻抗的合理范围应该在几十欧姆至数百欧姆之间;在高频电路中,电源阻抗的合理范围则可能会更低一些,通常在几欧姆至几十欧姆之间。

这些数值只是一个参考范围,具体的电路设计还需要根据实际情况进行具体的计算和调整。

电源阻抗的大小也会影响到电路的稳定性和性能。

如果电源阻抗太大,会造成电路中的功率损耗较大,导致电路效率较低;如果电源阻抗太小,会导致电路中的谐波失真等问题。

合理的电源阻抗应该在一定的范围内,不能太大也不能太小。

除了电路设计本身,电源阻抗的合理范围还受到一些外部因素的影响。

电源线的长度、材料、接触电阻等都会对电源阻抗产生影响。

在实际电路设计中,还需要考虑这些外部因素,综合分析确定合理的电源阻抗。

电源阻抗是电路设计中一个非常重要的参数,合理的电源阻抗可以保证电路的正常工作,提高电路的效率和可靠性。

在设计电路时,需要根据具体的情况进行合理的计算和设置,以确保电源阻抗处于一个合理的范围内。

【字数未达到要求,是否需要继续追加内容?】第二篇示例:电源阻抗是指电源对外部装置电流或电压的响应特性,这个参数在电路设计和应用中非常重要。

一个合理的电源阻抗范围可以确保电路正常工作,并且对电路的稳定性和性能有着重要的影响。

本文将从电源阻抗的定义、影响因素、合理范围以及调节方法等方面进行详细探讨。