高级计算机体系结构作业汇总非标准答案

计算机体系结构习题三及答案专升本高升专计算机高本下学期

计算机体系结构习题三及答案专升本⾼升专计算机⾼本下学期计算机体系结构习题三⼀、(10分)某台主频为400MHz的计算机执⾏标准测试程序,程序中指令类⼆、(10分)计算机系统中有三个部件可以改进,这三个部件的改进加速⽐为:部件加速⽐1=30;部件加速⽐2=20;部件加速⽐3=10 (1)如果部件1和部件2在整个系统运⾏时间中所占的⽐例均为30%,那么当部件3的⽐例为多少时,系统加速⽐才可以达到10?(2)如果三个部件的所占⽐例分别为30%、30%和20%,三个部件同时改进,那么系统中不可加速部分的执⾏时间在总执⾏时间中占的⽐例是多少?三、(5分)根据CPU中保存操作数的存储器类型,可以把指令集结构分为哪些类型?四、(10分)在MIPS流⽔线上运⾏如下代码序列:LOOP:LW R1,0(R2)DADDIU R1,R1,#1SW R1,0(R2)DADDIU R2,R2,#4DSUB R4,R3,R2BNEZ R4,LOOP其中:R3的初值是R2+396。

假设:在整个代码序列的运⾏过程中,所有的存储器访问都是命中的,并且在⼀个时钟周期中可对同⼀个寄存器在前半周期写,⽽在后半周期读。

那么:(1)在没有任何其它定向(或旁路)硬件的⽀持下,请画出该指令序列执⾏的流⽔线时空图。

假设采⽤暂停流⽔线的策略处理分⽀指令,且所有的存储器访问都命中Cache,那么执⾏上述循环需要多少个时钟周期?(2)假设该流⽔线有通常的定向路径,请画出该指令序列执⾏的流⽔线时空图。

假设采⽤预测分⽀失败的策略处理分⽀指令,且所有的存储器访问都命中Cache,那么执⾏上述循环需要多少个时钟周期?(3)假设该流⽔线有通常的定向路径和⼀个时钟周期的延迟分⽀,请对该循环中的指令进⾏调度,你可以重新组织指令的顺序,也可以修改指令的操作数,但是注意不能增加指令的条数。

请画出该指令序列执⾏的流⽔线时空图,并计算执⾏上述循环所需要的时钟周期数。

五、(10分)假设某程序各种分⽀指令数占所有指令数的百分⽐如下:现有⼀条段数为4的流⽔线,⽆条件分⽀在第2个时钟周期结束时就被解析出来,⽽条件分⽀要到第3个时钟周期结束时才能够被解析出来。

计算机体系结构考试卷子及答案

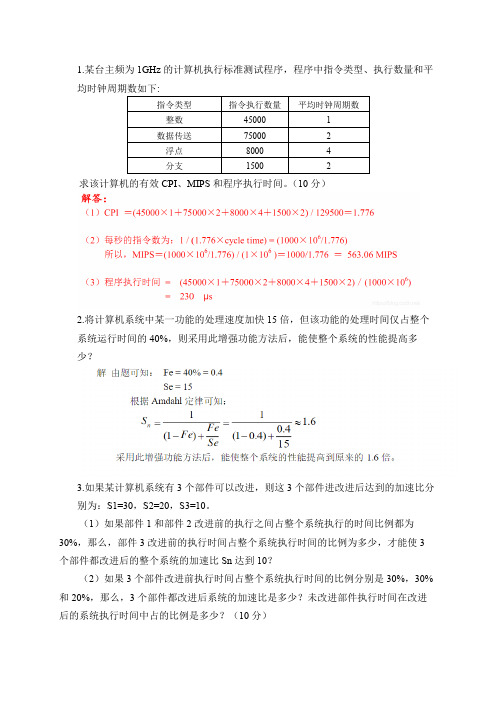

1.某台主频为1GHz的计算机执行标准测试程序,程序中指令类型、执行数量和平均时钟周期数如下:求该计算机的有效CPI、MIPS和程序执行时间。

(10分)2.将计算机系统中某一功能的处理速度加快15倍,但该功能的处理时间仅占整个系统运行时间的40%,则采用此增强功能方法后,能使整个系统的性能提高多少?3.如果某计算机系统有3个部件可以改进,则这3个部件进改进后达到的加速比分别为:S1=30,S2=20,S3=10。

(1)如果部件1和部件2改进前的执行之间占整个系统执行的时间比例都为30%,那么,部件3改进前的执行时间占整个系统执行时间的比例为多少,才能使3个部件都改进后的整个系统的加速比Sn达到10?(2)如果3个部件改进前执行时间占整个系统执行时间的比例分别是30%,30%和20%,那么,3个部件都改进后系统的加速比是多少?未改进部件执行时间在改进后的系统执行时间中占的比例是多少?(10分)4.假设某应用程序中有4类操作,通过改进,各操作获得不同的性能提高。

具体数据如下表所示:(1)改进后,各类操作的加速比分别是多少?(2)各类操作单独改进后,程序获得的加速比分别是多少?(3)4类操作均改进后,整个程序的加速比是多少?5.一台模型机的9条指令的使用频度如下:(10分)ADD(加):26%SHR(右移):2%SUB(减):17%CLL(循环左移):5%JOM(按页转移):11%CLA(累加器清零):15%STO(存):2%STP(停机):12%JMP(转移):10%试设计这9条指令的Huffman编码的操作码表示以及其等长扩展操作码表示,并计算这两种表示的平均操作码长度。

6.有一个“Cache-主存”存储层次。

主存共分为8个块(0~7),Cache为4个块(0~3),采用直接映像方式。

(1)对于如下主存块地址流:0、2、6、1、3、7、0、1、4、5、4、6、0、7、2,如主存中内容一开始未装入Cache,请列出每次访问后Cache中各块的分配情况;(2)对于(1),指出既发生块失效又发生块争用的时刻;(3)对于(1),求出此期间的Cache命中率。

计算机体系结构答案

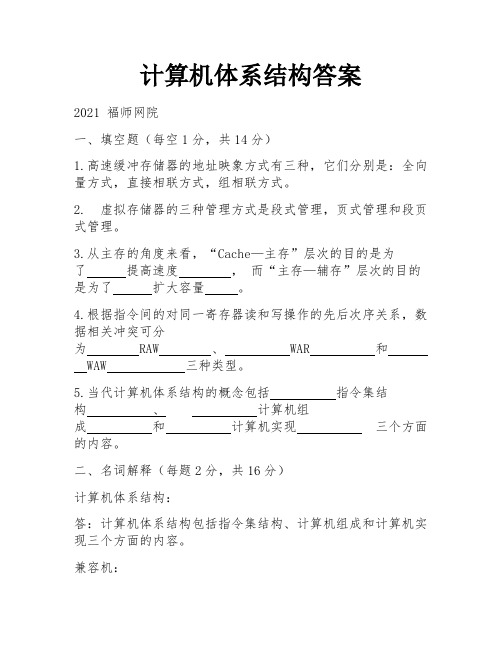

计算机体系结构答案2021 福师网院一、填空题(每空1分,共14分)1.高速缓冲存储器的地址映象方式有三种,它们分别是:全向量方式,直接相联方式,组相联方式。

2. 虚拟存储器的三种管理方式是段式管理,页式管理和段页式管理。

3.从主存的角度来看,“Cache—主存”层次的目的是为了提高速度,而“主存—辅存”层次的目的是为了扩大容量。

4.根据指令间的对同一寄存器读和写操作的先后次序关系,数据相关冲突可分为RAW 、WAR 和WAW 三种类型。

5.当代计算机体系结构的概念包括指令集结构、计算机组成和计算机实现三个方面的内容。

二、名词解释(每题2分,共16分)计算机体系结构:答:计算机体系结构包括指令集结构、计算机组成和计算机实现三个方面的内容。

兼容机:答:不同厂家生产的具有相同计算机结构的计算机;系列机:同一厂家生产的具有相同计算机结构,但具有不同组成和实现的一系列不同档次不同型号的机器;写直达法:答:执行“写”操作时,不仅写入Cache,而且也写入下一级存储器。

高速缓冲存储器:答:为解决CPU与主存储器间速度差而在内存储器和CPU之间增加的一种存取速度远高于普通内存的特殊存储器。

延迟转移技术:答:为了使指令流水线不断流,在转移指令之后插入一条不相关的有效的指令,而转移指令被延迟执行,这种技术称为延迟转移技术。

线性流水线:答:指各段串行连接、没有反馈回路的流水线。

数据通过流水线中的各段时,每一个段最多只流过一次;非线性流水线:指各段除了有串行的连接外,还有反馈回路的流水线。

流水线的吞吐率:答:在单位时间内流水线所完成的任务数量或输出结果的数量。

并行性:答:计算机系统在同一时刻或者同一时间间隔内进行多种运算或操作。

只要在时间上相互重叠,就存在并行性。

它包括同时性与并发性两种含义。

三、简答题(每题5分,共30分)1. 如有一个经解释实现的计算机,可以按功能划分成4级。

每一级为了执行一条指令需要下一级的N条指令解释。

计算机系统结构课后习题答案(第2版)

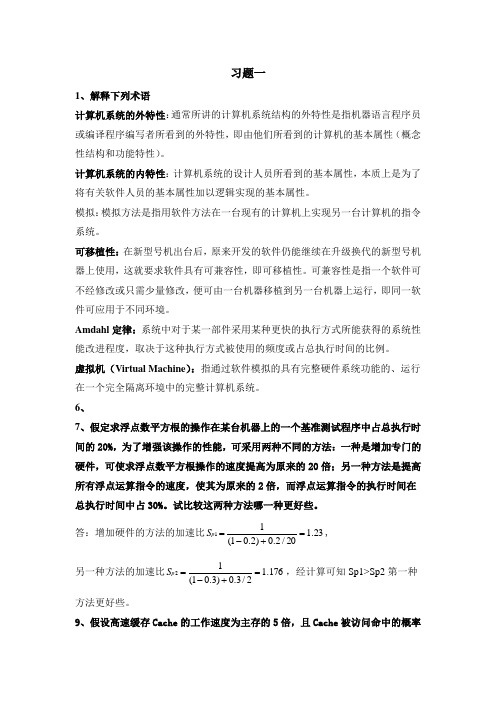

习题一1、解释下列术语计算机系统的外特性:通常所讲的计算机系统结构的外特性是指机器语言程序员或编译程序编写者所看到的外特性,即由他们所看到的计算机的基本属性(概念性结构和功能特性)。

计算机系统的内特性:计算机系统的设计人员所看到的基本属性,本质上是为了将有关软件人员的基本属性加以逻辑实现的基本属性。

模拟:模拟方法是指用软件方法在一台现有的计算机上实现另一台计算机的指令系统。

可移植性:在新型号机出台后,原来开发的软件仍能继续在升级换代的新型号机器上使用,这就要求软件具有可兼容性,即可移植性。

可兼容性是指一个软件可不经修改或只需少量修改,便可由一台机器移植到另一台机器上运行,即同一软件可应用于不同环境。

Amdahl定律:系统中对于某一部件采用某种更快的执行方式所能获得的系统性能改进程度,取决于这种执行方式被使用的频度或占总执行时间的比例。

虚拟机(Virtual Machine):指通过软件模拟的具有完整硬件系统功能的、运行在一个完全隔离环境中的完整计算机系统。

6、7、假定求浮点数平方根的操作在某台机器上的一个基准测试程序中占总执行时间的20%,为了增强该操作的性能,可采用两种不同的方法:一种是增加专门的硬件,可使求浮点数平方根操作的速度提高为原来的20倍;另一种方法是提高所有浮点运算指令的速度,使其为原来的2倍,而浮点运算指令的执行时间在总执行时间中占30%。

试比较这两种方法哪一种更好些。

答:增加硬件的方法的加速比Sp1=1.23, 另一种方法的加速比Sp2=1.176,经计算可知Sp1=方法更好些。

Sp2>Sp2第一种9、假设高速缓存Cache的工作速度为主存的5倍,且Cache被访问命中的概率T=为90%,则采用Cache能使整个存储系统获得多高的加速比?答:加速比,其中tm=5tc,代入公式、得到加速比S=3.33。

11、Flynn分类法的依据是什么,它与按“并行级”和“流水级”的分类方法有什么不同?答:Flynn分类法的依据是指令流和数据流多倍性概念进行分类的。

计算机系统结构网上作业参考答案

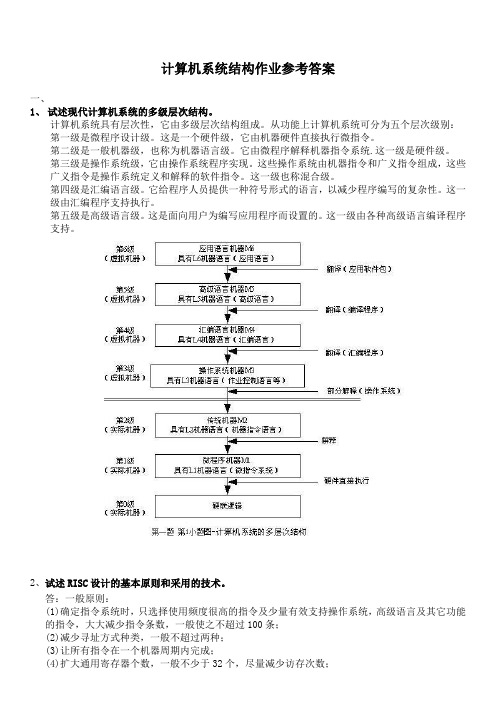

计算机系统结构作业参考答案一、1、试述现代计算机系统的多级层次结构。

计算机系统具有层次性,它由多级层次结构组成。

从功能上计算机系统可分为五个层次级别:第一级是微程序设计级。

这是一个硬件级,它由机器硬件直接执行微指令。

第二级是一般机器级,也称为机器语言级。

它由微程序解释机器指令系统.这一级是硬件级。

第三级是操作系统级,它由操作系统程序实现。

这些操作系统由机器指令和广义指令组成,这些广义指令是操作系统定义和解释的软件指令。

这一级也称混合级。

第四级是汇编语言级。

它给程序人员提供一种符号形式的语言,以减少程序编写的复杂性。

这一级由汇编程序支持执行。

第五级是高级语言级。

这是面向用户为编写应用程序而设置的。

这一级由各种高级语言编译程序支持。

2、试述RISC设计的基本原则和采用的技术。

答:一般原则:(1)确定指令系统时,只选择使用频度很高的指令及少量有效支持操作系统,高级语言及其它功能的指令,大大减少指令条数,一般使之不超过100条;(2)减少寻址方式种类,一般不超过两种;(3)让所有指令在一个机器周期内完成;(4)扩大通用寄存器个数,一般不少于32个,尽量减少访存次数;(5)大多数指令用硬联实现,少数用微程序实现;(6)优化编译程序,简单有效地支持高级语言实现。

基本技术:(1)按RISC一般原则设计,即确定指令系统时,选最常用基本指令,附以少数对操作系统等支持最有用的指令,使指令精简。

编码规整,寻址方式种类减少到1、2种。

(2)逻辑实现用硬联和微程序相结合。

即大多数简单指令用硬联方式实现,功能复杂的指令用微程序实现。

(3)用重叠寄存器窗口。

即:为了减少访存,减化寻址方式和指令格式,简有效地支持高级语言中的过程调用,在RISC机器中设有大量寄存嚣,井让各过程的寄存器窗口部分重叠。

(4)用流水和延迟转移实现指令,即可让本条指令执行与下条指令预取在时间上重叠。

另外,将转移指令与其前面的一条指令对换位置,让成功转移总是在紧跟的指令执行之后发生,使预取指令不作废,节省一个机器周期。

计算机系统结构——课后答案

习题一1、解释下列术语计算机系统的外特性:通常所讲的计算机系统结构的外特性是指机器语言程序员或编译程序编写者所看到的外特性,即由他们所看到的计算机的基本属性(概念性结构和功能特性)。

计算机系统的内特性:计算机系统的设计人员所看到的基本属性,本质上是为了将有关软件人员的基本属性加以逻辑实现的基本属性。

模拟:模拟方法是指用软件方法在一台现有的计算机上实现另一台计算机的指令系统。

可移植性:在新型号机出台后,原来开发的软件仍能继续在升级换代的新型号机器上使用,这就要求软件具有可兼容性,即可移植性。

可兼容性是指一个软件可不经修改或只需少量修改,便可由一台机器移植到另一台机器上运行,即同一软件可应用于不同环境。

Amdahl 定律:系统中对于某一部件采用某种更快的执行方式所能获得的系统性能改进程度,取决于这种执行方式被使用的频度或占总执行时间的比例。

虚拟机(Virtual Machine ):指通过软件模拟的具有完整硬件系统功能的、运行在一个完全隔离环境中的完整计算机系统。

6、7、假定求浮点数平方根的操作在某台机器上的一个基准测试程序中占总执行时间的20%,为了增强该操作的性能,可采用两种不同的方法:一种是增加专门的硬件,可使求浮点数平方根操作的速度提高为原来的20倍;另一种方法是提高所有浮点运算指令的速度,使其为原来的2倍,而浮点运算指令的执行时间在总执行时间中占30%。

试比较这两种方法哪一种更好些。

答:增加硬件的方法的加速比23.120/2.0)2.01(11=+-=p S ,另一种方法的加速比176.12/3.0)3.01(12=+-=p S ,经计算可知Sp1>Sp2第一种方法更好些。

9、假设高速缓存Cache 的工作速度为主存的5倍,且Cache 被访问命中的概率为90%,则采用Cache 能使整个存储系统获得多高的加速比? 答:加速比%10)(%90'⨯++⨯==tc tm tc tmT T S ,其中tm=5tc ,代入公式,得到加速比S=3.33。

(完整版)计算机系统结构考试题目及参考答案

一:名词解释1:虚拟机:由软件实现的机器。

2:CPI:是衡量CPU执行指令效率的重要标志,指执行每条指令所需的平均时钟周期数。

3:摩尔定律:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

4:并发性:指两个或多个事件在同一时间间隔内发生的并行性。

5:程序局部性原理:是指程序在执行时呈现出局部性规律,即在一段时间内,整个程序的执行仅限于程序中的某一部分。

相应地,执行所访问的存储空间也局限于某个内存区域。

局部性原理又表现为:时间局部性和空间局部性。

6:CISC/RISC:CISC:即复杂指令系统计算机,指在系统中增加更多和复杂的指令,来提高操作系统效率的计算机。

RISC:即精简指令系统计算机,指在系统中选取使用一些频率最高的、长度固定的、格式种类少的简单指令的计算机。

7:计算机系统结构:指对机器语言计算机的软、硬件功能的分配和对界面的定义。

8:系列机:指先设计好一种系统结构,而后就按这种系统结构设计它的系统软件,按器件状况和硬件技术研究这种结构的各种实现方法,并按照速度、价格等不同要求,分别提供不同速度、不同配置的各档机器。

9:模拟:用机器语言程序解释实现程序移植的方法。

10:仿真:用微程序直接解释另一种机器的指令系统。

11:寻址方式:寻找操作数或指令的有效地址的方式。

12:替换算法:在存储体系中,当出现页面失效时或者主存的所有页面已经全部被占用而又出现页面失效时,按照某种算法来替换主存中某页。

[由于主存中的块比Cache中的块多,所以当要从主存中调一个块到Cache中时,会出现该块所映象到的一组(或一个)Cache块已全部被占用的情况。

这时,需要被迫腾出其中的某一块,以接纳新调入的块。

]二:选择题1,直接执行微指令的是(C)A 汇编程序B 编译程序C 硬件D微指令程序2,对汇编语言程序员不透明的是(C)A 程序计数器B主存地址寄存器C条件码寄存器D指令寄存器3,最早的冯·诺依曼型计算机是以(B)为中心的A运算器B控制器C存储器 D I/O设备4,计算机系统结构的角度的结构来看,机器语言程序员看到的机器属性是(C )A 计算机软件所要完成的功能B 计算机硬件的全部组成C 编程要用到的硬件组织D计算机各部分硬件的实现5,不同系列计算机之间实现可移植性的途径,不包括(B )A 采用统一的高级语言B采用统一的汇编语言C 模拟D仿真6,利用时间重叠原理,实现并行处理的是(A)A流水处理机B多处理机 C 阵列处理机D集群系统7,多处理机实现的并行主要是(B)A指令级并行 B 任务级并行C 操作级并行D操作步骤的级并行8计算机系统结构不包括(B)A信息保护B存储速度C数据表示D机器工作状态9,不需要编址的数据存储空间(D )A CPU通用寄存器B 主存储器C I/O寄存器D堆栈10,RISC执行程序的速度比CISC 快的原因是(C)A RISC指令系统中条数较少B 程序在RISC编译生成的目标程序较短C RISC指令平均执行周期数较少D RISC中只允许LOAD和STORE指令存储11,程序员在编写程序时,使用的访存地址是(B)A主存地址B逻辑地址C物理地址D有效地址12,虚拟存储器主要是为了(A)A扩大存储器系统容量B提高存储器系统速度C扩大存储器系统容量和提高存储器系统速度D便于程序的访存操作13,与全相联映像相比,组相联映像的优点是(B)A目录表小B块冲突概率低C命中率高D主存利用率高14,输入输出数据不经过CPU内部寄存器的输入输出方式是(C )A程序控制方式B中断 C DMA方式D上述三种方式15,在配置了通道的计算机系统中,用户程序需要输入输出时引起的中断是(A)A访管中断 B I/O中断C程序性中断D外部中断16,当计算机系统通过执行通道程序,完成输入输出工作时,执行通道程序的是(B)A CPUB 通道C CPU和通道D指定的外设三:填空1,常见的计算机系统结构的分类法有两种:Flynn分类法,冯氏分类法冯氏分类法是根据系统的最大并行度对计算机系统结构进行分类,大多数的位并行的单处理机属于字串位并的处理机方式2,由软件实现的机器称为:虚拟机3,在一个计算机系统中,低层机器的属性往往对高层机器的程序员是透明的。

计算机体系结构试题及答案版本

计算机体系结构试题及答案1、计算机高性能发展受益于:(1)电路技术的发展;(2)计算机体系结构技术的发展。

2、层次结构:计算机系统可以按语言的功能划分为多级层次结构,每一层以不同的语言为特征。

第六级:应用语言虚拟机 ->第五级:高级语言虚拟机 ->第四级:汇编语言虚拟机 ->第三级:操作系统虚拟机->第二级:机器语言(传统机器级) ->第一级:微程序机器级。

3、计算机体系结构:程序员所看到的计算机的属性,即概括性结构与功能特性。

4、透明性:在计算机技术中,对本来存在的事物或属性,从某一角度来看又好像不存在的概念称为透明性。

5、Amdahl提出的体系结构是指机器语言级程序员所看见的计算机属性。

6、经典计算机体系结构概念的实质3是计算机系统中软、硬件界面的确定,也就是指令集的设计,该界面之上由软件的功能实现,界面之下由硬件和固件的功能来实现。

7、计算机组织是计算机系统的逻辑实现;计算机实现是计算机系统的物理实现。

8、计算机体系结构、计算机组织、计算机实现的区别和联系?答:一种体系结构可以有多种组成,一种组成可以有多种物理实现,体系结构包括对组织与实现的研究。

9、系列机:是指具有相同的体系结构但具有不同组织和实现的一系列不同型号的机器。

10、软件兼容:即同一个软件可以不加修改地运行于系统结构相同的各机器,而且它们所获得的结果一样,差别只在于运行时间的不同。

11、兼容机:不同厂家生产的、具有相同体系结构的计算机。

12、向后兼容是软件兼容的根本特征,也是系列机的根本特征。

13、当今计算机领域市场可划分为:服务器、桌面系统、嵌入式计算三大领域。

14、摩尔定律:集成电路密度大约每两年翻一番。

15、定量分析技术基础(1)性能的评测:(a)响应时间:从事件开始到结束之间的时间;计算机完成某一任务所花费的全部时间。

(b)流量:单位时间内所完成的工作量。

(c)假定两台计算机 x、y;x比 y 快意思为:对于给定任务,x的响应时间比y少。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.Explain the ConceptsComputer Architecture系统结构由程序设计者所看到的一个计算机系统的属性。

即计算机系统的软硬件界面。

Advanced CA高级系统结构新型计算机系统结构。

基于串行计算机结构,研究多指令多数据计算机系统,具有并发、可扩展和可编程性。

为非冯式系统结构。

Amdahl lawAmdahl定律系统中某部件由于采用某种方式时系统性能改进后,整个系统性能的提高与该方式的使用频率或占的执行时间的比例有关。

SCALAR PROCESSING标量处理机在同一时间内只处理一条数据。

LOOK-AHEAD先行技术通过缓冲技术和预处理技术,解决存储器冲突,使运算器能够专心与数据的运算,从而大幅提高程序的执行速度。

PVP向量型并行计算处理机以流水线结构为主的并行处理器。

SMP对称多处理机系统任意处理器可直接访问任意内存地址,使用共享存储器,访问延迟、带宽、机率都是等价的。

MPP大规模并行计算机系统物理和逻辑上均是分布内存,能扩展至成百上千处理器,采用专门设计和定制的高通信带宽和低延迟的互联网络。

DSM分布式共享存储系统内存模块物理上局部于各个处理器内部,但逻辑上是共享存储的。

COW机群系统每个节点都是一个完整的计算机,各个节点通过高性能网络相互连接,网络接口和I/O总线松耦合连接,每个节点有完整的操作系统。

GCE网格计算环境利用互联网上的计算机的处理器闲置处理能力来解决大型计算问题的一种科学计算。

CISC复杂指令集计算机通过设置一些复杂的指令,把一些原来由软件实现的常用功能改用硬件实现的指令系统实现,以此来提高计算机的执行速度。

RISC精简指令集计算机尽量简化计算机指令功能,只保留那些功能简单,能在一个节拍内执行完的指令,而把复杂指令用段子程序来实现。

VMM虚拟机监视器作为软硬件的中间层,在应用和操作系统所见的执行环境之间。

SUPERCOMPUTER超级计算机数百数千甚至更多的处理器组成的能计算普通计算机不能完成的大型复杂问题的计算机。

SVM共享虚拟存储器存储器虚拟化为一个共享的存储器,并提供单一的地址空间。

MAINFRAME大型计算机作为大型商业服务器,一般用于大型事务处理系统,特别是过去完成的且不值得重新编写的数据库应用系统方面。

COMPUTER SYSTEM ON CHIP片上计算机系统在单个芯片上集成的一个完整系统。

PARALLEL ARCHITECTURE INTO SINGLE CHIP单片并行结构在单个芯片上采用的并行体系结构MOORE lawMoore定律当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

UMA一致存储访问采用集中式存储的模式,提供均匀的存储访问。

NUMA非一致存储访问内存模块局部在各个结点内部,所有局部内存模块构成并行机的全局内存模块。

COMA全高速缓存存储访问采用分布式存储模式,通过高速缓存提供快速存储访问。

CC-NUMA全高速缓存非一致性均匀访问存在专用硬件设备保证在任意时刻,各结点Cache中数据与全局内存数据的一致性。

NORMA非远程存储访问利用私有的存储器通过互联网络进行消息传递。

SHELL ARCHITECTUREShell结构用专门定制的Shell电路将商用微处理器和节点的其它部分(包括板级Cache、局存、NIC 和DISK)连接起来。

PRAM随机存取并行机器模型共享存储的SIMD模型,假定存在一个容量无限大的共享存储器,有有限或无限个功能相同的处理器,且他们都具有简单的算术运算和逻辑判断功能,在任何时刻处理器都可以通过共享存储单元相互交互数据。

BSP整体同步并行计算模型分布存储的MIMD计算模型,将处理器和路由器分开,强调了计算任务和通信任务的分开。

采用障碍同步的方式以硬件实现的全局同步是在可控的粗粒度级,从而提供了执行紧耦合同步式并行算法的有效方式。

LOG P分布存储的、点到点通信的多处理机模型L (Latency) 表示信息从源到目的地所需的时间;O (Overhead) 表示处理器接受或发送一条消息所需额外开销,并且在此期间处理器不能做作任何操作;G (Gap)表示处理器连续进行两次发送或接收消息之间必须有的时间间隔;P (Processor) 表示处理器的数目。

2.Explain the Flynn classify and its semantics.1)单指令流单数据流(Single Instruction Stream Single Data Stream,SISD)SISD其实就是传统的顺序执行的单处理器计算机,其指令部件每次只对一条指令进行译码,并只对一个操作部件分配数据。

2)单指令流多数据流(Single Instruction Stream Multiple Data Stream,SIMD)SIMD以并行处理机为代表,结构如图,并行处理机包括多个重复的处理单元PU1~PUn,由单一指令部件控制,按照同一指令流的要求为它们分配各自所需的不同的数据。

3)多指令流单数据流(Multiple Instruction Stream Single Data Stream,MISD)MISD的结构,它具有n个处理单元,按n条不同指令的要求对同一数据流及其中间结果进行不同的处理。

一个处理单元的输出又作为另一个处理单元的输入。

4)多指令流多数据流(Multiple Instruction Stream Multiple Data Stream,MIMD)MIMD的结构,它是指能实现作业、任务、指令等各级全面并行的多机系统,多处理机就属于MIMD。

3.Where are the difficulties of Parallel Processing? What is ‘Parallel(并行)、concurrent(并发)and Simultaneous(同时)’separately?1)并行处理的难度:a)处理单元的多少以及其功能的强弱;b)处理单元的连接方式以及其处理结构;c)同步与互斥的实现;d)处理单元之间的数据传输;e)不同存储层次上的数据一致性。

2)并行:两个或多个事件在同一时刻发生;并发:两个或多个事件在同一时间间隔内发生;同时:两个或多个事件在同一时间内完成。

4.Assume that a system component be speeded to 10 times,Its past processing timeaccounts for 40% of the system,how much will be the system performance improved?5.Please draw the memory Hierarchy chart。

6.Explaining ConceptionsRISC精简指令集计算机尽量简化计算机指令功能,只保留那些功能简单,能在一个节拍内执行完的指令,而把复杂指令用段子程序来实现。

CISC复杂指令集计算机通过设置一些复杂的指令,把一些原来由软件实现的常用功能改用硬件实现的指令系统实现,以此来提高计算机的执行速度。

VLIW超大规模集成电路指几毫米见方的硅片上集成上万至百万晶体管、线宽在1微米以下的集成电路。

SUPER-SCALAR超标量通过内置多条流水线来同时执行多个处理器,其实质是以空间换取时间。

SUPER-PIPELINE超流水线通过细化流水、提高主频,使得在一个机器周期内完成一个甚至多个操作,其实质是以时间换取空间。

SUPER-SCALAR-SUPER-PIPELINE超标量超流水线在一个基本时钟周期内能够分时发送多组指令,并且每组指令又可包涵一条或多条指令。

IPC单位时钟周期内所执行的指令数SINGLE ISSUE单发射结构在一个时钟周期内只从存储器中取出一条指令,并且只对一条指令进行译码,只执行一条指令,只写一个运算结果。

MULTIPLE ISSUE多发射结构在一个基本时钟周期内同时从指令Cache中读出多条指令,同时对多条指令进行译码。

OOO乱序执行结构能够不按照程序提供的顺序完成计算任务,是一种加快处理器运算速度的架构。

Multi-Threading多线程同时运行多个轻量级任务。

7.In ideal case, please give the performances for SUPER-SCALAR, SUPERPIPELINE,SUPER-SCALAR-SUPER-PIPELINE, and give N=8 examples and their average IPC.1)性能超标量性能:S(m,1) = T(1,1) / T(m,1) = (K+N-1) / (K+(N-m)/m)超流水性能:S(1,n) = T(1,1)/T(1,n) = n(k+N-1) / nk+N-1超标量超流水性能:S(m,n) = T(1,1)/T(m,n) = (K+N-1) / (K+(N-m)/(mn))其中,N表示不相关指令数,m表示指令的并行度,n表示指令流水线的并行度,K表示指令流水线的阶段数2)N=8的周期图超标量:F- D- E- WF- D- E- WF- D- E- WF- D- E- WF- D- E- WF- D- E- WF- D- E- WF- D- E- W1 2 3 4 5 6 7IPC = 8 /7 = 1.14超流水:F |D |E |W | | | |F | D |E| W| | | ||F |D |E |W | | || F| D | E| W| | || |F |D |E |W | || | F| D | E| W| || | |F |D |E |W || | | F| D | E| W|1 2 3 4 5 6 7IPC = 8 / 7 = 1.14超标量超流水:F |D |E |W | |F |D |E |W | |F | D |E| W| |F | D |E| W| ||F |D |E |W ||F |D |E |W || F | D | E | W|| F | D| E | W|1 2 3 4 5IPC = 8 / 5 = 1.608.Please describe the CPU technology in recent years, and give an example to illustratetheir technical parameters.1)Hyper threadingThreads are independent parts of a computer program. Multi-tasking operating systems (e.g. Windows or Linux) work by allocating each thread a certain amount of "CPU time" in which toexecute some instructions. This means that they can run dozens of programs "at the same time".Multi-processor systems allow the OS to literally run two or more program threads simultaneously on different CPUs. This means that there is less competition for CPU time and therefore the computer should operate more quickly. However, multiprocessor systems are expensive.Hyper-Threading Technology (HTT) was introduced by Intel to give a cost-effective compromise. By duplicating some of the parts of the main core it pretends to be two processors. This gives a small speed increase (up to 30%).2)Dual Core & multi-coreDual core designs have two cores on a single chip, sometimes sharing L2 cache memory and always sharing bus interfaces. A dual-core chip is not as good as having two processors; however it gives typically 25%–75% faster performance than a single core processor.The Athlon 64 X2 and Pentium D were the first dual-core processors released for the PC, followed by the Intel Core Duo, Core 2 Duo and AMD Athlon FX60. Intel has released aThe diagram below shows the architecture of a Conroe core:9.Please give computing trace of a[i+7]=b[j+1]+c[k+8]+d[m+10] for T9000a[i+7]=b[j+1]+c[k+8]+d[m+10]1 |2 |3 |4 |5 |6 |7 |8 |9 |…Fj | | | | | | | | |Fb | | | | | | | | ||Fb[j] | | | | | | | || |Fb[j+1] | | | | | | ||Fk | | | | | | | ||Fc | | | | | | | || |Fc[k] | | | | | | || | |Fc[k+8] || | | | || | | |Eadd | | | | || |Fm | | | | | | || |Fd | | | | | | || | |Fd[m] | | | | | || | | |Fd[m+10]| | | | || | | | |Eadd | | | || | |Fi | | | | | || | |Fa | | | | | || | | |Fa[i] | | | | || | | | | | |Wa[i+7] | |2 |3 |4 |4 |3 |1 | |1 | |10.How to solve the multicore memory wall problem?解决“内存墙”问题包括内存带宽和内存等待时间两大基本途径,前者的应对方法是采用提高内存总线位宽和传输倍率的技术;后者是采用多级缓存和数据预取、多线程和乱序执行等技术。