IC 制程简介

IC 生产工艺

IC 生产工艺IC(集成电路)是一种关键的电子元器件,在现代科技中起着至关重要的作用。

IC的生产工艺是指将电子元件组装在硅片上的过程,它采用复杂的生产工艺流程,具有高精度和高可靠性的特点。

下面将详细介绍IC的生产工艺。

IC的生产工艺主要包括晶圆加工、电极蚀刻、沉积、光刻和封装等多个步骤。

首先是晶圆加工。

晶圆加工是将硅(或其他半导体材料)制成圆盘形状的过程。

晶圆加工通常分为六个步骤:选择硅材料、切割晶片、抛光晶圆、清洗晶圆、烘干晶圆和测量晶片。

接下来是电极蚀刻。

电极蚀刻是指将导电材料通过化学腐蚀的方式去除晶圆上不需要的部分。

电极蚀刻通常分为两个步骤:先用光刻技术将要去除的部分用光刻胶覆盖,然后通过腐蚀剂将光刻胶未覆盖的部分腐蚀掉,从而得到所需的电极形状。

然后是沉积。

沉积是将材料沉积在晶圆上的过程,以形成所需的结构。

沉积通常采用化学气相沉积(CVD)或物理气相沉积(PVD)方法进行。

CVD是通过将气体中的原子或分子化合物分解并沉积在晶圆上,而PVD是通过将固态材料蒸发或溅射,并将其沉积在晶圆上。

接着是光刻。

光刻是将图案转移到光刻胶上的过程,以便进一步制造线路和结构。

光刻通常分为两个步骤:先将光刻胶涂在晶圆上,然后通过照射光刻胶的方法,将图案转移到光刻胶上。

然后,通过化学处理去除未照明的光刻胶部分,留下所需的图案。

最后是封装。

封装是将晶圆上的芯片固定在封装底座上,并与外部引脚相连的过程。

封装通常分为两个步骤:先将芯片粘在封装底座上,然后通过焊接或金线连接芯片和封装底座,同时对芯片进行保护,以确保其在使用过程中的可靠性和稳定性。

以上是IC的生产工艺的主要步骤。

随着科技的进步,IC的生产工艺也在不断更新,以实现更小、更高性能和更高可靠性的IC产品。

IC的生产工艺是现代电子产业中非常关键的一环,对于推动科技的发展和提高产品性能有着重要的影响。

IC的生产工序流程以及其结构

IC的生产工序流程以及其结构IC,即集成电路,是现代电子产品中不可或缺的一部分。

从电子设备内部的芯片到计算机主板上的处理器,都离不开集成电路。

在这篇文章中,我们将会讨论IC生产的工序流程以及生产过程中的一些关键结构。

什么是IC?集成电路(Integrated Circuit,简称IC)是指在单个半导体晶片上集成了多种电子元器件,并通过扩散、离子注入、金属化等工艺技术把多个电子元器件集成在一起组成电路。

通常情况下,IC芯片都很小,大小通常被表示为微米(μm)或纳米(nm)级别。

IC的应用广泛,几乎覆盖了各个电子领域。

它们可以用于计算机处理器、智能手机、电视、汽车、医疗设备以及其他种类的电子产品。

IC生产的工序流程IC生产的工流程相当复杂,通常分为数十个步骤。

不过,大致上可以将IC生产的工序分为以下步骤:1. 半导体晶片制造半导体晶片制造是IC生产的第一步,也是最重要的一步。

半导体晶片通常由硅(Si)和氮化镓(GaN)、碳化硅(SiC)等半导体材料制成。

整个晶片制造流程通常包括以下几步:•晶圆生长:利用化学和物理反应方法,在单晶硅中生长出远大于晶体结构尺寸的大型晶体。

•制成硅晶圆:将生长出来的晶体锯成一层一层薄的硅片,制成硅晶圆。

•熔融硅基片上生长氧化层:在硅晶圆表面生成一个氧化物层。

•制作掩膜:通过光刻技术,将芯片上的某些区域遮蔽以形成模板。

•淀粉形成:将晶圆在磁场作用下放入高温炉中,以使得硅表面形成一层非晶质硅氧化物。

•拉后扩散水晶:在芯片上面涂上一层磷酸盐玻璃,并使其退火形成扩散层扩散N型氧化物或P型氧化物等。

2. 芯片制造在晶片制造的基础上,需要进行芯片制造。

这个步骤中,电阻器、电容器、二极管和晶体管等元件被加入到晶片中。

具体步骤如下:•氧化上浮:在表面形成氮化硅或氧化硅薄膜。

•制作掩膜:光刻技术用于制作薄膜的图案。

•腐蚀删除:将未被圈定的材料腐蚀去除。

•重复上述步骤:重复执行以上步骤,以形成几个电子元件。

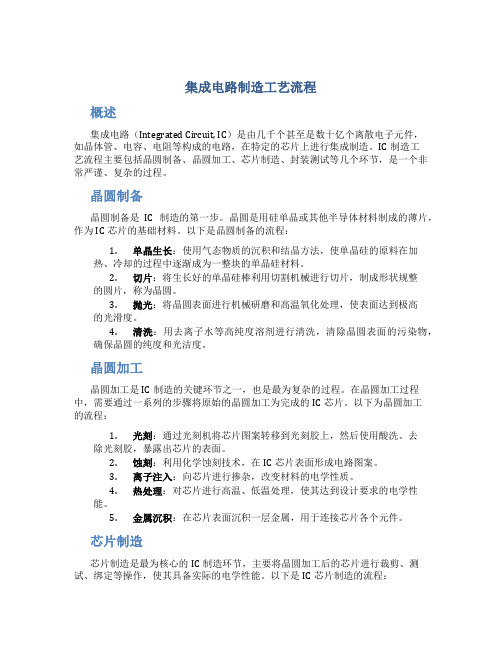

IC封装产品及制程简介

Bus bar

Signal

Signal

Signal

Signal

Bus bar tape

IC chip

Sectional View

wire

Inner Lead

tape

IC chip

Process Flow Chart, Equipment & Material

FLOW

PROCESS WAFER BACKGRINDRING

PIN PTH IC

J-TYPE P

BALL BGA

BUMPING F/C

IC Package Family

PTH IC:DIP── SIP、PDIP(CDIP)

PGA

SMD IC: SOIC ── SOP(TSOP-I、TSOP-II)、SOJ

LCC ── PLCC/CLCC

QFP ── 14×20/28×28、

LQFP)

10×10/14×14(TQFP、MQFP、 Others ── BGA、TCP、F/C

Something about IC Package Category

PTH IC:1960年代发表,至今在一些低价的电子组件上仍被广泛应用。 DIP ──美商快捷首先发表 CDIP。由于成本技术的低廉,很快成为当时主要的 封装形式;随后更衍生出 PDIP、SIP等。 PGA ──美商IBM首先发表,仅应用于早期的高阶 IC封装上,其Grid Array的 概念后来更进一步转换成为 BGA的设计概念。

EQUIPMENT SIBUYAMA-508

DIE SAW DIE ATTACH WIRE BOND MOLDING

DISCO 651

HITACHI CM200( LOC) HITACHI LM400(LOC)

集成电路制造工艺流程

集成电路制造工艺流程概述集成电路(Integrated Circuit, IC)是由几千个甚至是数十亿个离散电子元件,如晶体管、电容、电阻等构成的电路,在特定的芯片上进行集成制造。

IC制造工艺流程主要包括晶圆制备、晶圆加工、芯片制造、封装测试等几个环节,是一个非常严谨、复杂的过程。

晶圆制备晶圆制备是IC制造的第一步。

晶圆是用硅单晶或其他半导体材料制成的薄片,作为IC芯片的基础材料。

以下是晶圆制备的流程:1.单晶生长:使用气态物质的沉积和结晶方法,使单晶硅的原料在加热、冷却的过程中逐渐成为一整块的单晶硅材料。

2.切片:将生长好的单晶硅棒利用切割机械进行切片,制成形状规整的圆片,称为晶圆。

3.抛光:将晶圆表面进行机械研磨和高温氧化处理,使表面达到极高的光滑度。

4.清洗:用去离子水等高纯度溶剂进行清洗,清除晶圆表面的污染物,确保晶圆的纯度和光洁度。

晶圆加工晶圆加工是IC制造的关键环节之一,也是最为复杂的过程。

在晶圆加工过程中,需要通过一系列的步骤将原始的晶圆加工为完成的IC芯片。

以下为晶圆加工的流程:1.光刻:通过光刻机将芯片图案转移到光刻胶上,然后使用酸洗、去除光刻胶,暴露出芯片的表面。

2.蚀刻:利用化学蚀刻技术,在IC芯片表面形成电路图案。

3.离子注入:向芯片进行掺杂,改变材料的电学性质。

4.热处理:对芯片进行高温、低温处理,使其达到设计要求的电学性能。

5.金属沉积:在芯片表面沉积一层金属,用于连接芯片各个元件。

芯片制造芯片制造是最为核心的IC制造环节,主要将晶圆加工后的芯片进行裁剪、测试、绑定等操作,使其具备实际的电学性能。

以下是IC芯片制造的流程:1.芯片测试:对芯片的性能进行测试,找出不合格的芯片并予以淘汰。

2.芯片切割:将晶圆上的芯片根据需求进行切割。

3.接线:在芯片表面安装金线,用于连接各个器件。

4.包装:将芯片放入封装盒中,并与引线焊接,形成成品IC芯片。

封装测试封装测试是IC制造的最后一步。

第1讲 半导体器件(IC)制作工艺简介

优点:掩模寿命长(可提高10 倍以上),图形缺陷少。 缺点:衍射效应使分辨率下降。 最小可分辨的线宽为:

Wmin 15 d 200 d

当

0.4m, d 5~ 25m 时,Wmin 1.4~ 3.2m

23

(3). 缩小投影曝光技术

光源

透镜

随着线宽的减小和晶片直径的 增大,分辨率与焦深的矛盾越来越 严重。为解决这一问题,人们开发 出了:

13

光源 wafer mask

14

正性光刻胶 硅片 掩膜 二氧化硅膜 光

1. 光刻 胶的涂 覆

2. 前烘

3. 曝光

显影液

4.显影

5. 后烘

6. 腐蚀

7. 光刻 胶的去 15 除

16

光刻 (Photolithography & Etching) 过程如下: 1.涂光刻胶 2. 前烘 3.掩膜对准 4.曝光 5.显影 6.刻蚀:采用干法刻蚀(Dry Etching) 7.去胶:化学方法及干法去胶 (1)丙酮中,然后用无水乙醇

2

Process Flow of Annealed Wafer

Crystal Growth

Si Crystal Wafering Slicing High Temp. Annealed Wafer Annealing (Surface Improvement)

Furnace

Polished Wafer

11

1. 图形转换(光刻与刻蚀工艺)

光刻是加工集成电路微图形结构的关键工艺技 术,通常,光刻次数越多,就意味着工艺越复杂。 另—方面,光刻所能加工的线条越细,意味着工艺 线水平越高。光刻工艺是完成在整个硅片上进行开 窗的工作。 光刻技术类似于照片的印相技术,所不同的是, 相纸上有感光材料,而硅片上的感光材料--光刻胶是 通过旋涂技术在工艺中后加工的。光刻掩模相当于 照相底片,一定的波长的光线通过这个“底片”, 在光刻胶上形成与掩模版(光罩)图形相反的感光 区,然后进行显影、定影、坚膜等步骤,在光刻胶 膜上有的区域被溶解掉,有的区域保留下来,形成 了版图图形。

请简述你理解的芯片开发全流程及所需具备的技能。

请简述你理解的芯片开发全流程及所需具备的技能概述芯片(I nt eg ra te dC i rc ui t,I C)是现代电子产品的核心组件,其开发流程复杂且需要多种技能。

本文将简述芯片开发的全流程,并介绍在该过程中所需具备的技能。

芯片开发全流程芯片开发全流程通常包括前端设计、验证与验证、物理设计和半导体制造四个主要阶段。

前端设计前端设计是芯片开发的起始阶段,主要包括电路设计、逻辑设计和验证。

1.电路设计:根据芯片的需求和规格,设计各种模拟电路和数字电路,如放大器、滤波器、逻辑门等。

2.逻辑设计:根据芯片功能需求,设计芯片的逻辑电路,包括逻辑门、时序逻辑以及算术逻辑等。

3.验证:通过仿真和测试验证设计的电路和逻辑是否满足需求,调整设计模型以达到预期效果。

验证与验证验证与验证阶段是芯片开发的重要环节,旨在确保设计的正确性和稳定性。

1.功能验证:对设计的芯片进行功能验证,验证其是否满足预期功能。

2.时序验证:验证芯片中各个电路之间的时序关系是否满足需求。

3.电源与温度验证:验证芯片在不同电源电压和温度条件下的运行情况。

4.特性验证:验证芯片的特性参数,如功耗、噪声、功率纹波等。

物理设计物理设计阶段将前端设计的逻辑电路转化为物理实现,包括布局设计和版图设计两个方面。

1.布局设计:将芯片的逻辑电路进行物理布局,包括各个电路的位置、大小和连线的布线等。

2.版图设计:根据布局设计,进行具体的电路板设计,包括将电路转化为版图、调整连线路径、进行电气规则检查等。

半导体制造半导体制造是芯片开发的最后阶段,将物理设计的版图制造成真实的芯片产品。

1.掩膜制作:根据物理设计的版图,制作光刻掩膜,用于传输图案到硅片上。

2.硅片加工:将掩膜图案转移至硅片上,并进行各种工艺加工,如刻蚀、沉积、离子注入等。

3.封装与测试:将芯片进行封装,同时进行电性能测试,包括引脚功能、性能参数以及可靠性测试等。

所需具备的技能芯片开发需要综合掌握硬件、电路设计、逻辑设计和半导体制造等多个领域的知识和技能。

集成电路的制造工艺与特点

集成电路的制造工艺与特点集成电路(Integrated Circuit,简称IC)是现代电子技术的核心和基础,广泛应用于各个领域。

制造一颗集成电路需要经历多道复杂的工艺流程,下面将详细介绍集成电路的制造工艺与特点。

一、制造工艺步骤:1.掺杂:首先,将硅片(制造IC的基础材料)通过掺杂工艺,添加特定的杂质元素,如硼、磷等。

掺杂过程中,杂质元素会改变硅片的电学性质,形成P型或N 型半导体材料。

2.沉积:接下来,将制造IC所需的氧化层或其他特殊材料沉积在硅片表面。

这些材料可以保护芯片,也可以作为电气隔离层或其他功能层。

3.光刻:在硅片上涂上光刻胶,并通过光刻机器曝光、显影、清洗等步骤,将设计好的电路图案转移到光刻胶上。

然后,根据光刻胶的图案,在硅片上进行蚀刻或沉积等处理。

4.蚀刻:利用蚀刻工艺,在未被光刻胶保护的区域上去除多余的材料。

蚀刻可以采用化学腐蚀或物理蚀刻等方法。

5.离子注入:通过离子注入工艺,将特定的杂质元素注入硅片中,以改变硅片的电学性质。

这个过程可以形成导线、二极管、晶体管等功能器件。

6.金属化:在硅片上涂上金属层,以形成电路的金属导线。

经过一系列的金属化工艺,如光刻、蚀刻等,可以形成复杂的电路连接。

7.封装:将完成的芯片连接到封装基板上,通过线缆与外部器件连接。

封装的目的是保护芯片,并提供外部电路与芯片之间的连接。

8.测试:对制造完成的芯片进行测试,以确保其性能和质量符合设计要求。

测试可以包括功能测试、可靠性测试等多个方面。

二、制造工艺特点:1.微小化:集成电路的制造工艺趋向于微小化,即将电路的尺寸缩小到纳米级别。

微小化可以提高电路的集成度,减小体积,提高性能,并降低功耗和成本。

2.精密性:制造集成电路需要高度精密的设备和工艺。

尺寸误差、浓度误差等都可能影响电路的功能和性能。

因此,工艺步骤需要严格控制,以确保芯片的准确性和一致性。

3.多工艺组合:集成电路的制造通常需要多种不同的工艺组合。

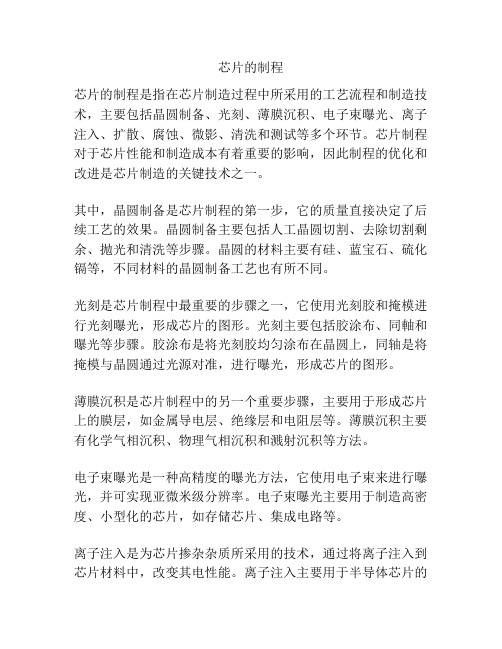

芯片的制程

芯片的制程芯片的制程是指在芯片制造过程中所采用的工艺流程和制造技术,主要包括晶圆制备、光刻、薄膜沉积、电子束曝光、离子注入、扩散、腐蚀、微影、清洗和测试等多个环节。

芯片制程对于芯片性能和制造成本有着重要的影响,因此制程的优化和改进是芯片制造的关键技术之一。

其中,晶圆制备是芯片制程的第一步,它的质量直接决定了后续工艺的效果。

晶圆制备主要包括人工晶圆切割、去除切割剩余、抛光和清洗等步骤。

晶圆的材料主要有硅、蓝宝石、硫化镉等,不同材料的晶圆制备工艺也有所不同。

光刻是芯片制程中最重要的步骤之一,它使用光刻胶和掩模进行光刻曝光,形成芯片的图形。

光刻主要包括胶涂布、同軸和曝光等步骤。

胶涂布是将光刻胶均匀涂布在晶圆上,同轴是将掩模与晶圆通过光源对准,进行曝光,形成芯片的图形。

薄膜沉积是芯片制程中的另一个重要步骤,主要用于形成芯片上的膜层,如金属导电层、绝缘层和电阻层等。

薄膜沉积主要有化学气相沉积、物理气相沉积和溅射沉积等方法。

电子束曝光是一种高精度的曝光方法,它使用电子束来进行曝光,并可实现亚微米级分辨率。

电子束曝光主要用于制造高密度、小型化的芯片,如存储芯片、集成电路等。

离子注入是为芯片掺杂杂质所采用的技术,通过将离子注入到芯片材料中,改变其电性能。

离子注入主要用于半导体芯片的制造过程中。

扩散是将材料中的杂质扩散到芯片表层,以形成所需的电性能。

扩散主要用于芯片的导电层和绝缘层的制造过程中。

腐蚀是芯片制程中用于去除杂质、污染物和不需要的材料的技术,它主要通过化学腐蚀和物理腐蚀两种方法进行。

微影是芯片制程中用于制造芯片图形的方法,主要包括光刻、腐蚀和清洗等步骤。

微影是芯片制程中的核心步骤之一,其精度和分辨率直接影响芯片的性能和制造成本。

清洗是芯片制程中用于去除制造过程中产生的污染物和杂质的方法,它主要通过溶液清洗、超声波清洗和喷洗等方法进行。

测试是芯片制程中的最后一步,用于检测芯片的性能和品质。

测试主要包括电测试、可视测试和射频测试等方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Seam/void PECVD

HDP

[3] 薄膜種類 -material poly-Si Si3N4 SiO2 反應氣體 SiH4 DCS+NH3 SiH4+NH3+N2 SiH4+O2(PH3+B2H6) SiH4+O2(PH3+BCl3) SiH4+N2O(PH3+B2H6) DCS+N2O TEOS(PH3, TMP) TEOS+O2(PH3, TMP) TEOS+O3 TEOS+O3(TMP, TMB) WF6+SiH4 Cu (hfac)(tmvs), Cu (hfac)2+H2 WF6+H2 WF6+SiH4 TiCl4+NH3 TDEAT+NH3 TDMAT(+NH3) DMAH Dimer Thermal decomposition

IC 製程簡介

FAB4 DRAM Process Integration

Contents

1. 製程原理簡介 :

a. 擴散 oxidation, doping b. 薄膜 CVD, PVD c. 微影 d. 蝕刻 dry, wet etching e. 化學機械研磨 CMP

2. 製程整合簡介:

- CMOS process flow簡介

[p]

mask

[p]

將離子射進Si中

d

• 一般分成blanket或 masked implantation

x

x

• 一般亦分成blanket或 masked implantation 植入法的優勢

• doping profile 的控制 - easy

差異點

• doping profile 擴散法 - 表面濃度最高 植入法 - 因植入能量而定

Application

Vt gate Field oxide

S/D Channel stop

well

substrate

[6] 未來趨勢-Junction Depth(um)

1. 淺接面(shallow junction) --> low junction capacitance --> small later diffusion 2. Little charge damage/high throughput 機台 3. 短時間回火技術開發 --> for shallow junction

• lateral(側向) diffusion 擴散法 > 植入法

• little lateral diffusion dimension shrinkage

[4] 植入法的特性(缺點) -Channeling effect Atom back-scattering • dopant離子射入Si時, 除了會沿入射方向前進 外,亦有部份離子會被反 向散射 • dopant離子進入Si內, 因Si 為單晶結構, 朝某 個方向看去時其空間相 對鬆散, 離子穿入較深 的深度

熱氧化模 型 (Deal-Grove Model)

• 反應氣體須到達gas-oxide界面 • 反應氣體須穿過(擴散)已存在的 oxide layer • 反應氣體在Si表面起反應

Cgas Cs

oxide

Si

• substrate doping : B enhanced • wet type > dry type

[2] 方式 – 1. Sputtering(濺鍍)

-- 利用Ar離子對靶材(target)進行轟擊(bombardment), 轟出靶材表面的原子或原子團,而後吸附在晶片上以生 成薄膜

+

Al-Cu target plasma Ar+ wafer

2. Evaporation(蒸鍍)

low

high

high(1150C)

low

[5] 應用 :

thickness 30~100A 150~500A 200~500A 2000~5000A application gate oxide, tunneling capacitor dielectrics LOCOS pad-oxide field oxide

I II

WSi Cu W TiN

Method LP LP PE AP LP PE LP LP PE AP, LP AP LP LP LP LP LP LP LP LP

用途 半導体 500~700 750~850 barrier 350~400 passivation 400~480 650~750 200~400 750~850 650~750 isolation 350~500 350~500 350~500 導線 300~400 350~450 400~500 " 400~700 " " 150~300 導線 導線 barrier ARC 導線

3. 製程規格與design rule

Thermal oxidation (熱氧化) :

[1] 原理 – 在高溫氧化爐(oxidation furnace)中利用高純度的O2或水蒸氣將Si 反應 成SiO2 [2] 方式 – 乾式(dry)氧化 Si + O2 SiO2 -- 濕式(wet)氧化 Si + 2H2O SiO2 + 2H2 [3] 機台 – 水平式 -- 垂直式 [4] 特性 –

300kev [B]

800kev

• 一般而言, 質量越輕的 離子此現象越明顯 ==>> 非預期的doping profile

==> 非預期的doping profile

<111>

Depth(um)

[P]

tail

<100>

Damage

Depth(um)

• dopant離子射入Si時, 是靠與矽原子的碰撞喪 失能量後才停在預期的 深度, 而矽原子也因此 可能被撞離原來所在的 晶格位置, 此稱之

1. Pressure 2. Temperature 3. Reactant concentration 4. dopants

PVD ( physical vapor deposition) : 物理氣相沉積

[1] 原理 – 氣相反應物沉積在Si surface以成長出所需之薄膜

(並未發生化學反應 )

Trend Chart

10 line w idth 1 Xj(n) Xj(p)

0.1

0.01 0.1 1 10 100

MG bit

CVD ( chemical vapor deposition) : 化學氣相沉積

[1] 原理 – 氣相反應物在Si surface發生化學反應, 成長出所需之薄膜

( * 若化學反應未到達Si surface即發生, 此 即為particle)

溫度 ©

Remark 溫度控制結晶度 reduce H含量 doped doped doped reduce H含量 doped(TEOS) doped(TEOS) doped(BPSG)

Al

SiO2 deposition依原料分

[4] 影響沉積的參數 -SiH4 based poor step coverage dangerous TEOS based good step coverage high particle O2/O3 低溫沉積 low viscosity low shrinkage after anneal better step coverage

-- high deposition rate/ throughput

Deposition profile

Conformal LPCVD

2. SACVD ( sub-atmospheric ) CVD:50~600torr

-- flow-like deposition

flow-like SACVD

3. LPCVD ( low pressure) CVD: 0.1~10torr

Boundary layer (a) diffusion (b) absorption (c) reaction (d) diffusion

Main stream

(e)

Si surface

[2] 方式 – 依反應室(chamber)的氣壓及電磁環境 可分成: 1. APCVD (atmospheric pressure) CVD

-- good uniformity/ conformal

4. PECVD* ( plasma enhanced ) CVD: 0.1~10torr

-- low temperature

Over-hang PECVD

5. HDPCVD* ( high density plasma ) CVDt 100

1000

Doping (摻雜) : 將不純物(dopant), 如 B, P 加入Si中, 藉此改變Si type及電性

[1] 方式 – 離子植入(ion implantation)法 -- 擴散(diffusion)法 [2] 機台 – ion implantation implanter -- diffusion furnace [3] 原理 –

[6] 未來趨勢 -1. very thin, defect-free oxide film 2. 大尺寸化熱處理條件

DRAM gate/capacitor trend chart

30

Ox ide Thickne ss(nm )

25 20 15 10 5 0 1 10 capacitor gate

防止Na 污染 : Na離子 --> 電晶體電性變差 1. 氧化時添加 HCl (3~5%) 2. PSG getter layer 3. Si3N4 diffusion barrier