锁相技术译文翻译

锁相环英文文献翻译

锁相技术译文翻译英文原名:High Speed Digital Hybrid PLL Frequency Synthesizer 译文:高速数字混合锁相环频率合成器年纪专业:08级通信工程班姓名:学号:2011年 5月2日prepare the precise synchronization of the complicated design.In 2001, H. G. Ryu proposed a simplified structure of the DDFS (direct digital frequency synthesizer)-driven PLL for the high switching speed [2].However, there is a problem that the speed of the whole system is limited by PLL.Y. Fouzar proposed a PLL frequency synthesizer of dual loop configuration using frequency-to-voltage converter (FVC) [3].It has a fast switching speed by the PD (phase detector), FVC using output signal of VCO and the proposed coarse tuning controller.However, H/W complexity is increased for the high switching speed.Also, it shows the fast switching characteristic only when the FVC works well.Another method is pre-tuning one which is called DH-PLL in this study [4].It has very high speed switching property, but H/W complexity and power consumption are increased due to digital look-up table (DLT) which is usually implemented by the ROM including the transfer characteristic ofVCO(voltage controlled oscillator).For this reason, this paper proposes a timing synchronization circuit for the rapid frequency synthesis and a very simple DLT replacement digital logic block instead of the complex ROM type DLT for high speed switching and low power consumption. Also, the requisite condition is solved in the proposed method. The fast switching operation at every the frequency synthesis process is verified by the computer circuit simulation.II.DH-PLL synthesizerAs shown in Fig.1, the open-loop synthesizer is a direct frequency synthesis type that VCO generates the desired output by the FCW (frequency control word) input from the D/A 压转换器(FVC)具有双重回路结构的锁相环频率合成器【3】。

2000门课程名称翻译大全(十五)

2000门课程名称翻译大全(十五)色彩 Color色谱 Color Spectrum摄影技巧 Techniques for Photography涉外企业管理 Enterprise Administration Concerning Foreign Natio社会调查的理论与方法 Theories & Methods for Social Investigation社会调查方法 Methods for Social Investigation社会工作 Social Work社会统计分析与SYSTAT应用 Social Statistics Analysis & SYSTAT Application社会统计学 Social Statistics社会问题研究 Research on Social Problems社会心理学 Social Psychology社会学概论 Introduction to Sociololgy社会学简论 Brief Introduction to Sociology社会学理论专题 Current Issues in Theories of Socilolgy 社会学问题研究 Research on Problems of Sociology社会学研究方法 Research Methods of Sociology社会主义财政学 Finance of Socialism社会主义各国政,经体制讨论 Discussion on Political & Economic Systems in Socialism审计学 Science of Auditing生产管理 Administration of Manufacturing生产过程计算机控制 Computer Control in Manufacturing Process生产过程自动化 Water-Turbine Engine生理学 Physiology生命科学与无机化学 Life Science and Inorganic Chemistry 生物工程产品 Bio-engineering Products生物工程导论 Introduction to Bio-engineering生物化学 Biochemistry生物化学工程 Biochemical Engineering生物化学及实验 Biochemistry Experiment生物检测技术 Measurement for Biotechnique生物控制论 Biocybernetics生物流变学 Biorheology生物物理 Biophysics生物学专题 Currents Issues in Biology生物医学超声学 Biomedical Supersonics失效分析 Invalidation Analysis诗歌美学 Aesthetics of Poetry时间序列 Time Sequence实变函数 Functions of Real Variable实验分析 Experimental Analysis实验力学 Experimental Mechanics实验力学基础 Basis of Experimental Mechanics实验流体 Experimental Flowing Object实验应力分析 Analysis of Experimental Stress世界近现代经济史 Modern History of World Economy世界近现代史 Modern History of the World世界文化史 History of World Culture世界政治经济与国际关系 World Politic Ecomony&International Relationship适应控制系统 Adaption Control System市场学 Science of Market市场研究 Research on Market市场预测 Market Predicting输入输出设计原理 Principle of Input and Output Designing 书法 Handwriting数据结构 Data Structure数据库概论 Introduction to Database数据库基础 Basis of Database数据库技术 Technique of Database数据库设计与分析 Design & Analysis of Database数据库系统原理 Principles of Database System数据库应用 Application of Database数据库原理及应用 Principle & Application of Database数控机床 Digit Control Machine Tool数控技术 Digit Control Technique数理方程 Mathematical Equations数理方程积分变换 Integral Transmission of Mathematical Equation数理方程与特殊函数 Equations of Mathmatical Physics & Special Functions数理逻辑 Mathematical Logic数理统计 Mathematical statistics数量经济 Quantity Economics数学分析 Mathematical Analysis数学规划 Mathematical Planning数学模型 Mathematical Modening数学物理方法 Method of Mathematical Physics数值电路 Digital Circuit数值分析 Numerical Analysis数值计算 Digital Computation数字测量技术 Digital Measuring Technique数字测量实验技术 Experimental Technique of Digital Measuring数字测试实验技术 Experimental Technique of Digital Testing数字电路 Digital Circuit数字电路及微机原理 Digital Circuit & Computer Principles 数字电视 Digital Television数字电子基础 Fundamental Digital Electionics数字电子技术 Digital Electronic Technique数字电子技术基础 Fundamental Digital Electronic Technique数字电子技术设计与实验 Experiment & Design of Digital Electron Technique数字电子线路 Digital Electrical Circuitry数字电子与微机原理 Digital Electronics & Principle of Microcomputer数字仿真 Digital Simulation数字化测量技术 Digital Measuring Technique数字控制及微机控制技术 Digital Control & Microcomputer Control Technique数字逻辑 Digital Logic数字图象处理 Digital Image Processing数字系统逻辑设计 Logical Design of Digital System数字系统设计 Design of Digital System数字信号处理 Digital Signal Processing双曲线方程 Hyperbolic Equation水电能源学 Science of HydrOelectric Enelgy水电站过渡过程的特殊问题 Special Problems in the Transition of a Hydropower Station水电站计算机控制 Computer Control in Hydropower Station 水电站经济运行 Economic Operation in Hydropower Station 水电站控制系统分析 Analysis of Control System in Hydropower Station水电站自动化 Automation of Hydropower Station水动力学 Water Dynamics水机工艺结构分析 Technics Structure Analysis of Hydraulic Machinery水力机械测试技术 Test Technique of Hydraulic Machinery 水力机械的汽蚀 Gas Etching of Hydraulic Machinery水力机械调节 Adjustment of Hydraulic Machinery水力机械强度计算 Intensity Calculation of Hydraulic Machinery水力机械原理 Principles of Hydraulic Machinery水力机械制造工艺及结构分析 Manufacturing Technique &Structure Analysis of Hydraulic Machinery水力机械制造工艺学 Manufacturing Technique for Hydraulic Machinery水力学 Hydraulics水轮机 Water-Turbine Engine水轮机调节 Water-Turbine Engine Adaption水轮机调节系统 Adaptive System of Water-Turbine Engine 水轮机水力设计 Hydraulic Design of Water Engine水轮机原理及水力设计 Principles of Water-Turbine Engine & Design of Water Engine水轮机原理与CAD Principle of Water-Turbine Engine & CAD 水轮水力设计 Hydraulic Design of Water Engine水现代控制理论 Modern Theory of Water Controling水质稳定技术 Stability Technique of Water Quality思想教育 Virtue Education素描 Pencil Sketch速冻技术 Technique of Speed Freezing塑性力学 Plastic Machanics算法语言 Algorithmic Language随机过程 Stochastic Process & Time Series Analysis随机运筹学 Randomized Operational Research锁相技术 Phase Lock Technique---来源网络整理,仅供参考。

锁相技术课件

一、概述

§6.3 频率合成

1. 概念

频率合成器是将一个高精确度和高稳定度的标准

参考频率,经过混频、倍频与分频等对它进行加、

减、乘、除的四则运算,最终产生大量的具有同样

精确度和稳定度的频率源。

2. 应用 频率合成器在雷达、通信、遥控遥测、电视广

播和电子测量仪器等方面得到了广泛的应用。

《锁相技术》

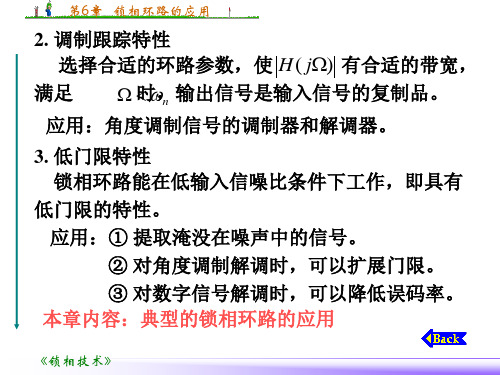

第6章 锁相环路的应用

于He (s)具有高通特性,只要在He (s) 的通带之内,

输出信号频偏正比于调制信号的幅度。----调频波

调相波:

2

(s)

He (s)

Ko s

sU F

(s)

对调制信号先 微分再调频

2 (s) He (s)KoUF (s)

输出信号相位正比于调制信号的幅度。----调相波

《锁相技术》

第6章 锁相环路的应用

音频信号调频,则输入瞬时频率为:

载频

i (t) c sin t

Δω为峰 值频偏

当 0 时,i c ,所以 实际是叠加到c 上的。

做出 H ( ji ) i 的关系图,就是环路对输入信号 瞬时频率i 的振幅频率响应:

《锁相技术》

第6章 锁相环路的应用

-3dB点

2c

① 具有带通滤波特性。带宽为 2c 。 ② 由于锁相环的跟踪性能,其中心频率可以跟踪输

fd

fo N V

fo N Vfr

①增加前置分频器,解决了输出频率高于程序分频

器的工作频率的问题,提高了输出频率范围。

《锁相技术》

第6章 锁相环路的应用

②输出频率增量为Vfr ,频率分辨率降低了。

③如果保持原有的频率分辨率 fr ,需要使参考频率

锁具方面的专业术语的英文

1、锁具结构mechanisms of lock1.1 弹子结构Pin tumbler mechanism 一组基本形状为圆柱形的零件,起销住或释放锁芯运动作用的结构称弹子结构。

1.2 叶片结构flat tumbler mechanism 一组形状为片状形的零件,起卡住或释放锁芯运动作用的结构称叶片结构。

1.3 磁性结构magnetic mechanism 应用磁性材料制成的零件,起锁住作用,其结构称为磁性结构。

1.4 密码结构combination mechanism 以数字编码组成的结构称密码结构。

1.5 电子编码结构electronic coding mechanism 应用电子原理编码组成的结构电子结构。

2、锁具分类classification of Locks2.1 挂锁padlock 以挂的形式锁住物件(体)的锁。

2.1.1 直开挂锁bottom opening padlock 钥匙从锁头底面插入后,旋转开启的锁。

2.1.2 横开挂锁lateral opening padlock 钥匙从锁头侧面插入后,旋转开启的锁。

2.1.3 顶开挂锁pushing opening padlock 钥匙插入后,向前顶开的锁2.1.4 双开挂锁double key padlock 用两把不同钥匙才能开启的锁。

2.2 建筑门锁door lock in building 适用于建筑楼房门上的锁。

2.2.1 外装门锁rim lock 锁体安装在门挺表面上的锁。

2.2.1.1 单舌单保险门锁single bolt single security door lock 单舌结构具有单保险功能的锁。

2.2.1.2 单舌双保险门锁single bolt double security door lock 单舌结构具有双保险的锁。

2.2.1.3 单舌三保险门锁single bolt triple security door lock 单舌结构具有三保险功能的锁。

锁相环英文文献翻译

锁相技术译文翻译英文原名:High Speed Digital Hybrid PLL Frequency Synthesizer译文:高速数字混合锁相环频率合成器年纪专业:08级通信工程班姓名:学号:2011年 5月2日To get the high-speed, it is necessary to prepare the precise synchronization of the complicated design.In 2001, H. G. Ryu proposed a simplified structure of the DDFS (direct digital frequency synthesizer)-driven PLL for the high switching speed [2].However, there is a problem that the speed of the whole system is limited by PLL.Y. Fouzar proposed a PLL frequency synthesizer of dual loop configuration using frequency-to-voltage converter (FVC) [3].It has a fast switching speed by the PD (phase detector), FVC using output signal of VCO and the proposed coarse tuning controller.However, H/W complexity is increased for the high switching speed.Also, it shows the fast switching characteristic only when the FVC works well.Another method is pre-tuning one which is called DH-PLL in this study [4].It has very high speed switching property, but H/W complexity and power consumption are increased due to digital look-up table (DLT) which is usually implemented by the ROM including the transfer characteristic ofVCO(voltage controlled oscillator).For this reason, this paper proposes a timing synchronization circuit for the rapid frequency synthesis and a very simple DLT replacement digital logic block instead of the complex ROM type DLT for high speed switching and low power consumption. Also, the requisite condition is solved in the proposed method. The fast switching operation at every the frequency synthesis process is verified by the computer circuit simulation.II.DH-PLL synthesizerAs shown in Fig.1, the open-loop synthesizer is a direct frequency synthesis type that VCO 要得到高运行速度,事先做好复杂设计的精确同步是必要的。

锁相技术译文翻译

锁相技术译文翻译英文原名:An On-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOI译文:45纳米SOI全数字片上测量电路表征锁相环响应特性English中文 An On-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOI Dennis Fischette, Richard DeSantis, and John Haeseon LeeAdvanced Micro Devices, Inc., Sunnyvale, CA 94085-3905 USAAbstract —An all-digital measurement circuit, built in 45-nm SOI-CMOS enables on-chip characterization of phase-locked loop (PLL) response to a self-induced phase step. This technique allows estimation of PLL closed-loop bandwidth and jitter peaking. The circuit can be used to plot step-response vs. time, measure static phase error, and observe phase-lock status.INTRODUCTIONMany applications such as PCI Express ™require a PLL to produce a low-jitter clockat a given frequency while meeting stringentbandwidth and jitter peaking requirements.Process, voltage, and temperature (PVT) variations as well as random device mismatchmake it difficult to guarantee a narrow rangefor PLL response. For example, loopparameters such as VCO gain could vary by more than 2X over PVT corners. In Fig. 1, we see the closed-loop jitter transfer functions of two PLLs with identical reference clock and output frequencies. One PLL exhibits large peaking and low bandwidth while the other shows little peaking but high bandwidth. Although differences in this example are more extreme than usual, similar but smaller differences often result from PVT variations.45纳米SOI 全数字片上测量电路表征锁相环响应特性作者信息摘要——全数字化测量电路,45纳米SOI-CMOS 工艺使其能够片上表征锁相环(PLL )对自诱导相步进的响应。

《锁相技术》课件

减小功耗的措施

采用低功耗的器件

如低功耗的VCO、鉴相器等。

优化电路设计

优化电路设计,降低功耗。

开启/关闭不必要的功能

在不需要时关闭某些功能,降低功耗。

01

锁相环路的测试与 验证

测试方法与测试环境

测试方法

采用模拟信号源和频谱分析仪对锁相环路的性能进行测试。

感谢观看

THANKS

THE FIRST LESSON OF THE SCHOOL YEAR

21世纪

随着通信技术的发展,锁相技 术在移动通信、卫星通信等领

域得到广泛应用。

01

锁相环路的工作原 理

锁相环路的组成

鉴相器(PD)

VCO(压控振荡器)

用于检测输入信号与输出信号的相位 差。

用于产生可调频率的输出信号,通过 电压控制其振荡频率。

环路滤波器(LF)

用于滤除鉴相器产生的误差电压中的 高频分量,平滑输出电压。

锁相技术在其他领域的应用探索

要点一

总结词

要点二

详细描述

除了通信领域,锁相技术在其他领域也有广泛的应用前景 。

随着科技的不断发展,锁相技术的应用领域也在不断拓展 。未来,锁相技术有望在雷达、导航、电子对抗、电力系 统等领域得到广泛应用。例如,在雷达领域,锁相技术可 以实现高精度、高稳定性的频率源,提高雷达的探测精度 和距离分辨率;在电力系统领域,锁相技术可以用于实现 电网的稳定运行和故障诊断等方面。

测试环境

在实验室条件下进行,确保测试结果的准确性和可靠性。

测试结果与分析

测试结果

锁相环路在低频和高频段均表现出良 好的跟踪性能和噪声抑制能力。

16、锁相技术

锁相技术一、引言锁相,就是实现两个电信号相位同步的自动控制。

锁定放人器(LIA —L0ck —in AmDlmer)是锁相技术在微弱信号检测中的应用,本实验将研究锁定放大器的原理和应用。

实验的目的要求是:l 了解锁定放大器的工作原理,着重掌握相关器的原理。

2学会使用锁定放大器,并用它测量p .n 结势垒电容。

二、原理(一)锁定放大器的基本原理本实验采用NL 一1锁定放大器,其原理框图见图12.k 锁定放大器是一种交流电压表,它能精确地测定深埋在噪声之中的周期重复信号的幅值及相位,这种抑制噪声的作用主要是通过相关器实现的,使用时,除要输入待测信号外,还要输入参考信号。

图12—1 NL 一1锁定放大器原理框图1、相关器 锁定放大器中的相关器如图12—2所示。

它由相乘电路和低通滤波器组成,相乘电路有许多形式,如开关型、电流控制型等等,NL 一1锁定放大器采用开关型。

低通滤波器具有压缩噪声带宽,让直流信号通过的作用,它抑制噪声的能力可以用“等效噪声带宽”图12—2相关器这一参数来描述,可以求出,图12—2中的低通滤波器的等效噪声带宽f n=1144RC T= 低通滤波器的时间常数T=Rc ,T 越长则f n 越小,但实际上由于漂移等问题,T 是不能太长的。

下面是相关器的工作原理。

相关器采用的是所谓相关接收技术。

设输入信号为()Vi t ,参考信号为()Vr t ,由于低通滤波器实际上是一个积分器,因此相关器的输出0V 是()Vi t 和()Vr t 乘积,再对时间积分,并取平均值有0V = ()1lim ()2T i t T V t Vr t dt T τ→∞--⎰ (12-1)式中t 是参考信号相对于输入信号的延迟时间,积分时间上限T 即低通滤波器的时间常数,通常把式(12.1)所表示的0V 称为()Vi t 和()Vr t 的相关函数,实现求相关函数的电子线路称为相关器或相关接收器。

下面的讨论会更清楚相关器的作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相技术译文翻译

英文原文:

An On-Chip All-Digital Measurement Circuit to Characterize

Phase-Locked Loop Response in 45-nm SOI

译文:45纳米SOI全数字片上测量电路表征锁相环响应特性

年级专业:

姓名:学号:

2013年6月2日

CIRCUIT DESIGN

The PLL under test (Fig. 5) isa standard integer-N charge-pump PLL. The only modification is the addition of loop measurement circuitry. The feedback divisor (N) isprogrammable from 5 to 63,although N>=8 during loop measurement tests. The charge-pump current, loop-filter resistance, and VCO gain are programmable to allow for bandwidth and peaking adjustments aswell as jitter optimization. The PLL bandwidth may be configured from 3 to 25 MHz while the peaking may be varied from <1 to >4 dB. The VCO operates from 1.6 to 5 GHz. The expected reference clock frequency rangeis 100 to 200 MHz.

INTRODUCTION

Many applications such as PCI Express™require a PLL to produce alow-jitter clock at a given frequency while meeting stringent bandwidth and jitter peaking requirements. Process, voltage, and temperature (PVT) variations as well as random device mismatch make it difficult to guarantee a narrow range for PLL response. For example ,loop parameters such as VCO gain could vary by more than 2X over PVT corners. In Fig. 1, we see the closed-loop jitter transfer functions of two PLLs with identical reference clock and output frequencies. One PLL exhibits large peaking and low bandwidth while the other shows little peaking but high bandwidth. Although differences in this example are more extreme than usual, similar but smaller differences often result from PVT varOn-Chip All-Digital Measurement Circuit to Characterize Phase-Locked Loop Response in 45-nm SOI

Abstract—An all-digital measurement

Circuit , built in 45-nm SOI-CMOS enables on-chip characterization of phase-locked loop (PLL) response to a self-induced phase step. This technique allows estimation of PLL closed-loop bandwidth and jitter peaking. The circuit can be used to plot step-response vs.time, measure static phase error, and observe phase-lock status.

A simple way to induce the required input phase step is to flip the polarity of the reference clock so its phase is advancedby half a clock cycle. A disadvantage to this approach is that the magnitude of the phase step is dependent on the reference clock duty cycle. This is undesirable because overshoot tests require a large and predictable input phase step. Instead, the circuit implementation presented here manipulates the feedback divisor to induce a known phase step. The circuit then automatically measures the resulting crossover and MaxOvershoot. Fig.6 shows a block diagram of the loop measurement test circuit. It includes three main units: control, crossover detector, and MaxOvershoot detector. The control unit contains two synchronizers (to VCO clock), three edge detectors (rising and falling), andlogic to enable the induced phase step. The crossover detector includes a bang-bang phase detector, a phase-error change-of-sign detector, and a 10-bit counter. The MaxOvershoot detector contains a feedback count sampler, a comparator, and a maximum overshoot register.

PLL response is often measured on a test bench using signal generators, oscilloscopes, and/or spectrum analyzers. For example, the transfer functions in Fig. 1 were automatically generated by modulating the 100-MHz reference clock with various frequencies while observing the amplitudes of the resulting output spurs. Such methods, which may require many seconds to complete, motivate the need for faster, less expensive, and preferably on-chip techniques to characterize PLL response [1]-[3]. Fig. 2 shows the PLL output phase transient response to an induced phase step. Similar to other second-order feedback systems, the PLL tends to overcorrect (or overshoot) as it works to eliminate the induced phase error. If the PLL is underdamped, as in this example, the PLL may ring several times before settlingto its final lock state. A key metric in the PLL step-response is crossover, defined here as the elapsed time from input step toonset of phase overshoot. Another key metric is MaxOvershoot. It measures the maximum overcorrectionin the step response.