全定制集成电路设计流程PPT课件

合集下载

集成电路设计流程

集成电路设计流程

(1)要素分析:分析用户要求,根据用户需求深入研究,确定集成电路所需要的各种要素,确定所需要的元器件;

(2)原理图设计:按照确定的要素,根据原理及功能确定元器件的布局,完成原理图设计;

(3)栅格布局:根据原理图设计完成元器件的实际布置,并按照规定的栅格布局完成布局;

(4)栅格设计:完成布局后,将布局信息转化为栅格数据,完成栅格设计;

(5)电路模拟:根据栅格设计结果,使用电路模拟软件对电路功能进行模拟;

(6) 驱动器布线设计:根据模拟中发现的问题,将电路输入输出端进行驱动器布线,完成所有驱动器的连接;

(7) 质量测试与验证:根据确定的质量指标,对集成电路的质量进行测试,确保设计的集成电路满足用户对性能的要求;

(8) 封装设计:根据栅格设计结果,进行封装设计,确定实际封装的参数;

(9) 布线设计:完成封装设计后,在封装中进行布线设计,确保集成电路布线连接良好;

(10) 生产组装:将设计完成的集成电路进行实际生产,将所需要的元器件组装,完成集成电路的制作。

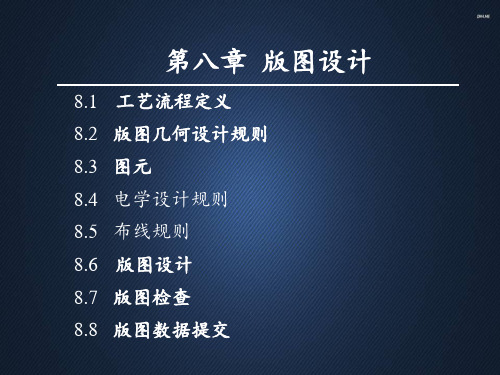

集成电路版图设计 ppt课件

(b)

图8.3 交叠的定义

表8.5 TSMC_0.35μm CMOS工艺版图各层图形之间最小交叠

表 16.5 T SM C _0.35μ m C M O S 工 艺 版 图 各 层 图 形 之 间 最 小 交 迭

N _ w e ll A c tiv e P o ly P _ l\p lu s_ se le c t/N _ p lu s_ se l ect C o n ta c t M e ta l1 V ia 1 M e ta l2 E le c tro d e V ia 2 M e ta l3

MOS管的可变参数为:栅长(gate_length)、栅宽(gate_width) 和栅指数(gates)。

栅长(gate_length)指栅极下源区和漏区之间的沟道长度,最 小值为2lambda=0.4μm。

栅宽(gate_width)指栅极下有源区(沟道)的宽度,最小栅宽为 3 lambda=0.6μm。

201010233636cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图716画l型金属线作地线图717画出两只mcs3并将它们的栅漏和源极互连201010233737vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图718画出两只mn1并将它们的栅漏和源极互连cmos差动放大器单元电路设计版图的过程201010233838图719依次画出r1并联的两只msf1和并联的两只mcf1以及偏压等半边电路版图vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outoutcmos差动放大器单元电路设计版图的过程201010233939cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图720通过对图819中半边版图对x轴作镜像复制形成的完整版图201010234040在正式用cadence画版图之前一定要先构思也就是要仔细想一想每个管子打算怎样安排管子之间怎样连接最后的电源线地线怎样走

最新模拟集成电路设计流程课件

Session菜单

Schematic Window Save State Load State Options Reset Quit

回到电路图

2021/1/15

保存当前 所设定的 模拟所用 到的各种

参数

加载已 经保存 的状态

共88页

一些显 示选项 的设置

重置

analog artist。 相当于 重新打 开一个 模拟窗

ac(交流分析)是 分析电路性能随着 运行频率变化而变

化的仿真。

既可以对频率进行 扫描也可以在某个 频率下进行对其它

变量的扫描。

2021/1/15

共88页

22

其它有关的菜单项

Outputs/Setup

当然我们需要输出的有时不仅仅是电流、电压,还有一 些更高级的。比如说:带宽、增益等需要计算的值,这时 我们可以在Outputs/setup中设定其名称和表达式。在运行 模拟之后,这些输出将会很直观的显示出来。

2021/1/15

共88页

11

编辑完成的电路图

2021/1/15

共88页

12

一些快捷键

以下是一些常用的快捷键: i 添加元件,即打开添加元件的窗口; [ 缩小两倍; ] 扩大两倍; w 连线(细线); f 全图显示; p 查看元件属性; m 整体移动(带连接关系); shift+m 移动(不带连接关系)。

2021/1/15

共88页

13

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

《IC设计流程》课件

《IC设计流程》PPT课件

# IC设计流程 ## 概述 - IC设计是指集成电路的设计过程 - IC设计流程包括多个阶段 - IC设计的目的是制造高质量电子产品

什么是IC设计?

IC设计是指集成电路的设计和制造过程,它涵盖了从初始概念到最终产品的 多个阶段。它是现代电子产品制造过程中的关键步骤。

IC设计流程详解

IC设计行业前景展望

IC设计行业前景广阔,将在智 能手机、物联网等领域持续迎 来机遇。

总结

IC设计流程的重要性

IC设计流程是确保电子产品质量 和性能的关键步骤。

IC设计行业的前景及挑战

IC设计行业将面临激烈的竞争和 技术更新的挑战。

如何提高IC设计效率和质量

采用先进的设计工具和方法,注 重团队协作和创新。

用于评估电路的物理特性 和性能的仿真软件

3 电路仿真软件

用于模拟电路行为和性能 的仿真软件

4 芯片测试仪器

用于测试和评估芯片性能的仪器设备

5 整机测试仪器

用于测试和评估整机性能的仪器设备

IC设计行业数据

IC设计市场规模

IC设计市场规模不断增长,预 计将在未来几年保持稳定增长。

IC设计市场发展趋势

IC设计行业正在向更高集成度、 更低功耗和更高性能的方向发 展。

前期准备

项目规划、技术方案研究、 芯片功能定义、芯片架构设 计等

测试验证

芯片测试、整机应用测试等

电路计

逻辑设计、前端仿真、前端 布局等

物理设计

后端布局、物理验证、物理 仿真等

封装测试

封装设计、封装仿真、封装测试等

IC设计流程中的常用工具

1 电路布局软件

用于设计和优化电路布局 的软件工具

2 物理仿真软件

# IC设计流程 ## 概述 - IC设计是指集成电路的设计过程 - IC设计流程包括多个阶段 - IC设计的目的是制造高质量电子产品

什么是IC设计?

IC设计是指集成电路的设计和制造过程,它涵盖了从初始概念到最终产品的 多个阶段。它是现代电子产品制造过程中的关键步骤。

IC设计流程详解

IC设计行业前景展望

IC设计行业前景广阔,将在智 能手机、物联网等领域持续迎 来机遇。

总结

IC设计流程的重要性

IC设计流程是确保电子产品质量 和性能的关键步骤。

IC设计行业的前景及挑战

IC设计行业将面临激烈的竞争和 技术更新的挑战。

如何提高IC设计效率和质量

采用先进的设计工具和方法,注 重团队协作和创新。

用于评估电路的物理特性 和性能的仿真软件

3 电路仿真软件

用于模拟电路行为和性能 的仿真软件

4 芯片测试仪器

用于测试和评估芯片性能的仪器设备

5 整机测试仪器

用于测试和评估整机性能的仪器设备

IC设计行业数据

IC设计市场规模

IC设计市场规模不断增长,预 计将在未来几年保持稳定增长。

IC设计市场发展趋势

IC设计行业正在向更高集成度、 更低功耗和更高性能的方向发 展。

前期准备

项目规划、技术方案研究、 芯片功能定义、芯片架构设 计等

测试验证

芯片测试、整机应用测试等

电路计

逻辑设计、前端仿真、前端 布局等

物理设计

后端布局、物理验证、物理 仿真等

封装测试

封装设计、封装仿真、封装测试等

IC设计流程中的常用工具

1 电路布局软件

用于设计和优化电路布局 的软件工具

2 物理仿真软件

集成电路设计与制造的主要流程图

集成电路芯片设计过程框架

否 否

否

3

引言

半导体器件物理基础:包括PN结的物理机制、双极管、 MOS管的工作原理等

器件

小规模电路

大规模电路

超大规模电路

甚大规模电路

电路的制备工艺:光刻、刻蚀、氧化、离子注入、扩散、 化学气相淀积、金属蒸发或溅射、封装等工序

集成电路设计:另一重要环节,最能反映人的能动性

✓ 高度复杂电路系统的要求 ✓ 什么是分层分级设计? 将一个复杂的集成电路系统的设计问题分解为复杂性较低的设 计级别,这个级别可以再分解到复杂性更低的设计级别;这样 的分解一直继续到使最终的设计级别的复杂性足够低,也就是 说,能相当容易地由这一级设计出的单元逐级组织起复杂的系 统。一般来说,级别越高,抽象程度越高;级别越低,细节越 具体

集成电路 设计与制造的主要流程

1

集成电路设计与制造的主要流程框架

系 统 需 求 设计

掩膜版

芯片制造 过程

芯片检测

封装 测试

单晶、外 延材料

2

集成电路的设计过程:

设计创意 +

仿真验证

功能要求 行为设计(VHDL)

行为仿真 是

综合、优化——网表

时序仿真 是

布局布线——版图

—设计业—

后仿真 是

Sing off

没有单元库支持:对各单元进行电路设计,通过电

路模拟与分析,预测电路的直流、交流、瞬态等特性, 之后再根据模拟结果反复修改器件参数,直到获得满 意的结果。由此可形成用户自己的单元库

21

单元库:一组单元电路的集合

经过优化设计、并通过设计规则检查和反复工艺验证, 能正确反映所需的逻辑和电路功能以及性能,适合于工 艺制备,可达到最大的成品率。

否 否

否

3

引言

半导体器件物理基础:包括PN结的物理机制、双极管、 MOS管的工作原理等

器件

小规模电路

大规模电路

超大规模电路

甚大规模电路

电路的制备工艺:光刻、刻蚀、氧化、离子注入、扩散、 化学气相淀积、金属蒸发或溅射、封装等工序

集成电路设计:另一重要环节,最能反映人的能动性

✓ 高度复杂电路系统的要求 ✓ 什么是分层分级设计? 将一个复杂的集成电路系统的设计问题分解为复杂性较低的设 计级别,这个级别可以再分解到复杂性更低的设计级别;这样 的分解一直继续到使最终的设计级别的复杂性足够低,也就是 说,能相当容易地由这一级设计出的单元逐级组织起复杂的系 统。一般来说,级别越高,抽象程度越高;级别越低,细节越 具体

集成电路 设计与制造的主要流程

1

集成电路设计与制造的主要流程框架

系 统 需 求 设计

掩膜版

芯片制造 过程

芯片检测

封装 测试

单晶、外 延材料

2

集成电路的设计过程:

设计创意 +

仿真验证

功能要求 行为设计(VHDL)

行为仿真 是

综合、优化——网表

时序仿真 是

布局布线——版图

—设计业—

后仿真 是

Sing off

没有单元库支持:对各单元进行电路设计,通过电

路模拟与分析,预测电路的直流、交流、瞬态等特性, 之后再根据模拟结果反复修改器件参数,直到获得满 意的结果。由此可形成用户自己的单元库

21

单元库:一组单元电路的集合

经过优化设计、并通过设计规则检查和反复工艺验证, 能正确反映所需的逻辑和电路功能以及性能,适合于工 艺制备,可达到最大的成品率。

《集成电路版图设计》课件

元器件工作原理

了解各种元器件的工作原理是进行版图设计的基础,如晶 体管的工作原理涉及到载流子的运动和电荷的积累等。

元器件版图设计规则

在进行元器件版图设计时,需要遵循一定的设计规则,如 电阻的阻值计算、电容的容量计算等,以确保设计的准确 性和可靠性。

集成电路工艺

01 02

集成电路工艺流程

集成电路的制造需要经过多个工艺步骤,包括薄膜制备、光刻、刻蚀、 掺杂等,这些工艺步骤的参数和条件对集成电路的性能和可靠性有着重 要影响。

学生需要按照指导要求,完成集成电路版图设计实践任务,并

提交实践报告。

集成电路版图设计实践图设计

案例四

某混合信号集成电 路版图设计

案例一

某数字集成电路版 图设计

案例三

某射频集成电路版 图设计

案例五

某可编程逻辑集成 电路版图设计

集成电路版图设计实践经验总结

实践经验总结的重要性

特点

集成电路版图设计具有高精度、 高复杂度、高一致性的特点,需 要综合考虑电路功能、性能、可 靠性以及制造工艺等多个方面。

集成电路版图设计的重要性

01

02

03

实现电路功能

集成电路版图设计是将电 路设计转化为实际产品的 关键环节,是实现电路功 能的重要保障。

提高性能和可靠性

合理的版图设计可以提高 集成电路的性能和可靠性 ,确保产品在长期使用中 保持稳定。

DRC/LVS检查

进行设计规则检查和版图验证 ,确保版图设计的正确性和可 制造性。

布图输出

将版图数据输出到制造环节, 进行硅片的制作。

02

集成电路版图设计基础知识

半导体材料

半导体材料分类

半导体材料分为元素半导体和化合物半导体两大类,元素半导体包括硅和锗,化合物半导 体包括三五族化合物(如砷化镓、磷化镓等)和二六族化合物(如硫化镉、硒化镉等)。

了解各种元器件的工作原理是进行版图设计的基础,如晶 体管的工作原理涉及到载流子的运动和电荷的积累等。

元器件版图设计规则

在进行元器件版图设计时,需要遵循一定的设计规则,如 电阻的阻值计算、电容的容量计算等,以确保设计的准确 性和可靠性。

集成电路工艺

01 02

集成电路工艺流程

集成电路的制造需要经过多个工艺步骤,包括薄膜制备、光刻、刻蚀、 掺杂等,这些工艺步骤的参数和条件对集成电路的性能和可靠性有着重 要影响。

学生需要按照指导要求,完成集成电路版图设计实践任务,并

提交实践报告。

集成电路版图设计实践图设计

案例四

某混合信号集成电 路版图设计

案例一

某数字集成电路版 图设计

案例三

某射频集成电路版 图设计

案例五

某可编程逻辑集成 电路版图设计

集成电路版图设计实践经验总结

实践经验总结的重要性

特点

集成电路版图设计具有高精度、 高复杂度、高一致性的特点,需 要综合考虑电路功能、性能、可 靠性以及制造工艺等多个方面。

集成电路版图设计的重要性

01

02

03

实现电路功能

集成电路版图设计是将电 路设计转化为实际产品的 关键环节,是实现电路功 能的重要保障。

提高性能和可靠性

合理的版图设计可以提高 集成电路的性能和可靠性 ,确保产品在长期使用中 保持稳定。

DRC/LVS检查

进行设计规则检查和版图验证 ,确保版图设计的正确性和可 制造性。

布图输出

将版图数据输出到制造环节, 进行硅片的制作。

02

集成电路版图设计基础知识

半导体材料

半导体材料分类

半导体材料分为元素半导体和化合物半导体两大类,元素半导体包括硅和锗,化合物半导 体包括三五族化合物(如砷化镓、磷化镓等)和二六族化合物(如硫化镉、硒化镉等)。

《集成电路版图设计》(第二章)PPT课件

方式二:选择Attach

基于Cadence系统的 全定制版图设计基础

基于Cadence系统的 全定制版图设计基础

三、显示文件准备

LSW窗口:

✓ nwell是N 阱,PMOS管做在N阱中; ✓ ndiff是N型扩散区,也叫N型有源区(active),用来做NMOS管; ✓ pdiff是P型扩散区,也叫P型有源区,用来做PMOS管; ✓ nimp是N型扩散区注入层; ✓ pimp是P型扩散区注入层; ✓ poly是多晶层,主要用来做管子的栅极; ✓ cont是接触孔contact; ✓ metal1是一铝层; ✓ via1是一铝层和二铝层之间的连接孔,称为通孔; ✓ metal2是二铝层; ✓ pad是压焊点所在的层; ✓ 其它还包括一些特殊器件上的标识层等等

3、单元的宽长比设 置原则——最常见 宽长比的设置

逻辑图中每一 个管子宽长比 的设置

基于Cadence系统的 全定制版图设计基础

3、单元的宽长 比设置原则— —最常见宽长 比的设置(续)

单元符号的建立和 Label的设置

基于Cadence系统的 全定制版图设计基础

3、单元的宽长比 设置原则——其它 宽长比的设置

基于Cadence系统的 全定制版图设计基础

第一部分、D508项目逻辑图的准备

一、逻辑图输入工具启动

二、一个传输门逻辑图及符 号的输入流程

三、D508项目单元逻辑图的准备 四、D508项目总体逻辑图的准备

第二部分、D508项目版图输入准备

一、设计规则准备 二、工艺文件准备 三、显示文件准备

第三部分、版图设计步骤及操作

三、显示文件准备(续)

基于Cadence系统的 全定制版图设计基础

Display Resource Editor 窗口:

《集成电路设计》课件

蒙特卡洛模拟法

通过随机抽样和概率统计的方法,模 拟系统或产品的失效过程,评估其可 靠性。

可靠性分析流程

确定分析目标

明确可靠性分析的目 的和要求,确定分析 的对象和范围。

进行需求分析

分析系统或产品的使 用环境和条件,确定 影响可靠性的因素和 条件。

进行失效分析

分析系统或产品中可 能出现的失效模式和 原因,确定失效对系 统性能和功能的影响 。

DRC/LVS验证

DRC/LVS验证概述

DRC/LVS验证是物理验证中的两个重要步骤,用于检查设计的物 理实现是否符合设计规则和电路图的要求。

DRC验证

DRC验证是对设计的物理实现进行规则检查的过程,以确保设计的 几何尺寸、线条宽度、间距等参数符合设计规则的要求。

LVS验证

LVS验证是检查设计的物理实现与电路图一致性的过程,以确保设 计的逻辑功能在物理实现中得到正确实现。

版图设计流程

确定设计规格

明确设计目标、性能指标和制造工艺要求 。

导出掩模版

将最终的版图导出为掩模版,用于集成电 路制造。

电路设计和模拟

进行电路设计和仿真,以验证电路功能和 性能。

物理验证和修改

进行DRC、LVS等物理验证,根据结果进 行版图修改和完善。

版图绘制

将电路设计转换为版图,使用专业软件进 行绘制。

集成电路设计工具

电路仿真工具

用于电路设计和仿真的软件, 如Cadence、Synopsys等。

版图编辑工具

用于绘制版图的软件,如Laker 、Virtuoso等。

物理验证工具

用于验证版图设计的正确性和 可靠性的软件,如DRC、LVS等 。

可靠性分析工具

用于进行可靠性分析和测试的 软件,如EERecalculator、 Calibre等。

通过随机抽样和概率统计的方法,模 拟系统或产品的失效过程,评估其可 靠性。

可靠性分析流程

确定分析目标

明确可靠性分析的目 的和要求,确定分析 的对象和范围。

进行需求分析

分析系统或产品的使 用环境和条件,确定 影响可靠性的因素和 条件。

进行失效分析

分析系统或产品中可 能出现的失效模式和 原因,确定失效对系 统性能和功能的影响 。

DRC/LVS验证

DRC/LVS验证概述

DRC/LVS验证是物理验证中的两个重要步骤,用于检查设计的物 理实现是否符合设计规则和电路图的要求。

DRC验证

DRC验证是对设计的物理实现进行规则检查的过程,以确保设计的 几何尺寸、线条宽度、间距等参数符合设计规则的要求。

LVS验证

LVS验证是检查设计的物理实现与电路图一致性的过程,以确保设 计的逻辑功能在物理实现中得到正确实现。

版图设计流程

确定设计规格

明确设计目标、性能指标和制造工艺要求 。

导出掩模版

将最终的版图导出为掩模版,用于集成电 路制造。

电路设计和模拟

进行电路设计和仿真,以验证电路功能和 性能。

物理验证和修改

进行DRC、LVS等物理验证,根据结果进 行版图修改和完善。

版图绘制

将电路设计转换为版图,使用专业软件进 行绘制。

集成电路设计工具

电路仿真工具

用于电路设计和仿真的软件, 如Cadence、Synopsys等。

版图编辑工具

用于绘制版图的软件,如Laker 、Virtuoso等。

物理验证工具

用于验证版图设计的正确性和 可靠性的软件,如DRC、LVS等 。

可靠性分析工具

用于进行可靠性分析和测试的 软件,如EERecalculator、 Calibre等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

20

设计规则检查(DRC) 对版图进行几何规则检查,使得设计的电路可 以被制造出来。 电气规则检查(ERC) 检查电源地的短路,开路,浮空的器件、浮空 的网络… 一致性校验(LVS) 检查版图和电路图的一致性 RC分布参数提取

21

22

数模混合集成电路 设计流程

23

测试向量

技术规范

系统级建模

总体设计 数字/模拟

18

* Feedback CAP Cc vout 4 0.44pF Cl vout 0 4pF Ibias vdd vbias 8.8u * Voltage sourses vdd vdd 0 5v vss vss 0 0v

19

版图设计

布局:安排模块位置(面积/速度) 电源分布 信号耦合 天线效应 电磁兼容性 可控硅效应 静电保护 焊盘位置、封装 测试探针

可靠性分析 可控硅效应 静电放电(ESD)

9

芯片封装

功能:提供保护、散热和系统连接 考虑: 引脚数目 管芯大小 热阻 安装方式 电气特性 DEBUG

10

电路设计

•功能 •定时约束 •可测试性设计 •电源地 •功耗

11

电路技术规范:

电气条件 极限工作条件:电源电压、输入电压范围、工作温

度范围、存储温度范围 静态参数:输入/输出电压、电流、功耗 动态工作参数:工作频率、上升/下降时间、建立

Typical

15

16

*Two stage OP design .lib "umc05.lib" TYP .options post nomod .TEMP 27 * Netlist information M1 3 1 5 0 nmos L=2u W=8u AS=18p AD=18p + PS=18u PD=18u M2 4 2 5 0 nmos L=2u W=8u AS=18p AD=18p + PS=18u PD=18u M3 3 3 vdd vdd pmos L=10u W=10u AS=12p AD=12p PS=16u PD=16u

17

M4 4 3 vdd vdd pmos L=10u W=10u AS=12p AD=12p PS=16u PD=16u M5 5 vbias vss vss nmos L=2u W=7u AS=49p AD=49p PS=26u PD=26u M6 vout 4 vdd vdd pmos L=2u W=70u AS=490p AD=490p PS=150u PD=150u M7 vout vbias vss vss nmos L=2u W=130u AS=930p AD=930p + PS=260u PD=260u M8 vbias vbias vss vss nmos L=2u W=7u AS=49p AD=49p PS=26u PD=26u

划分 RTL描述仿

真

A

模拟单元技 术规范

结构选择电 路设计

B

24

约束 综合库 扫描链/BIST配置

测试向量 仿真库

物理约束 单元库

A

逻辑综合

门级混合仿 真

版图规划

布局 RC延时估计

C

定时估计

B 设计仿真

模拟单元模型 定时估计

版图设计

E

物理验证 RC分布参数

提取

后仿真

D

25VS, DRC,ERC)

TapeOut

网表 定时信息

D

模拟单元模 型修正

定时验证

OK?

E

26

2020/1/3

27

保持时间

功能定义:真值表、状态图,… 模拟指标:频率响应、电源抑制比、共模抑制比、稳

定时间、增益、增益误差,…

其他:

ESD,I/O电容、测量条件、引脚对应、封装形式,…

12

电路设计时应当考虑 工艺参数:每一层的厚度… 工艺流程: 电气参数:阈值电压、最大耐压、方块电阻、 方块电容、温度系数… 设计规则: 晶体管模型参数

7

后仿真

实际的互连线有阻抗特性,对原有电路的功能/ 性能有影响, 完整的设计必须考虑互连线对电路的影响; 准确的互连线模型才能得到准确的仿真结果; 完整的互连线模型是分布参数模型,在仿真时必 须考虑分布参数元件的缩减 后仿真包括RC分布参数提取和仿真

8

信号完整性分析

集成电路中线间距很小、一个信号线上的信号变 化可能影响其他信号的波形; 集成电路所有元件加工在同一个衬底上,干扰信 号可能通过衬底影响其它元件; 集成电路上的电源和地用金属线连接到所有元件 上,金属线上的分布电感可以把电流的变化转换 成电压的变化而影响电路的工作;

13

2020/1/3

14

设计容限

制造误差:

Fast

Typical

Slow

温度变化:

0 ℃ -25 ℃ -70 ℃(商业)

-55 ℃ -25 ℃ -125℃(军品)

电源变化:

VDDX(1+/-10%)

Desing Conner

VDD ,T , fast PMOS, fast NMOS

VDD ,T , slow PMOS, slow NMOS

4

仿真

根据给定的元件模型验证所设计电路的功能和指标 提供电路参数修改的依据 根据模拟结果得到版图设计的依据:电源线宽… 根据工艺参数误差确定电路的工作范围和限制 验证环境变化对电路特性的影响

5

版图设计

将电路转换成集成电路加工所需要的几何图形描述

6

版图验证

每个工艺都有其设备和控制上的极限,如:光解析度、化 学药品浓度、温度、时间…;版图设计必须能够适应工艺 流程合理的差异,在版图设计过程中要符合代工厂的要求 设计规则。 电路设计和版图设计是设计过程中不同的阶段,必须确认 电路与版图之间的映射关系。

全定制集成电路 设计流程

1

2

确定技术规范

系统级建模

测试向量 单元模型

测试向量 单元模型

模块技术规范 仿真

布局

单元库

后仿真 满足规范要求?

版图验证 RC参数提取

设计规则

生产

3

电路设计

根据技术规范选择合适的结构 根据结构选择元件的组合 根据交直流参数要求确定晶体管的大小和工作点 根据环境确定负载类型和大小

设计规则检查(DRC) 对版图进行几何规则检查,使得设计的电路可 以被制造出来。 电气规则检查(ERC) 检查电源地的短路,开路,浮空的器件、浮空 的网络… 一致性校验(LVS) 检查版图和电路图的一致性 RC分布参数提取

21

22

数模混合集成电路 设计流程

23

测试向量

技术规范

系统级建模

总体设计 数字/模拟

18

* Feedback CAP Cc vout 4 0.44pF Cl vout 0 4pF Ibias vdd vbias 8.8u * Voltage sourses vdd vdd 0 5v vss vss 0 0v

19

版图设计

布局:安排模块位置(面积/速度) 电源分布 信号耦合 天线效应 电磁兼容性 可控硅效应 静电保护 焊盘位置、封装 测试探针

可靠性分析 可控硅效应 静电放电(ESD)

9

芯片封装

功能:提供保护、散热和系统连接 考虑: 引脚数目 管芯大小 热阻 安装方式 电气特性 DEBUG

10

电路设计

•功能 •定时约束 •可测试性设计 •电源地 •功耗

11

电路技术规范:

电气条件 极限工作条件:电源电压、输入电压范围、工作温

度范围、存储温度范围 静态参数:输入/输出电压、电流、功耗 动态工作参数:工作频率、上升/下降时间、建立

Typical

15

16

*Two stage OP design .lib "umc05.lib" TYP .options post nomod .TEMP 27 * Netlist information M1 3 1 5 0 nmos L=2u W=8u AS=18p AD=18p + PS=18u PD=18u M2 4 2 5 0 nmos L=2u W=8u AS=18p AD=18p + PS=18u PD=18u M3 3 3 vdd vdd pmos L=10u W=10u AS=12p AD=12p PS=16u PD=16u

17

M4 4 3 vdd vdd pmos L=10u W=10u AS=12p AD=12p PS=16u PD=16u M5 5 vbias vss vss nmos L=2u W=7u AS=49p AD=49p PS=26u PD=26u M6 vout 4 vdd vdd pmos L=2u W=70u AS=490p AD=490p PS=150u PD=150u M7 vout vbias vss vss nmos L=2u W=130u AS=930p AD=930p + PS=260u PD=260u M8 vbias vbias vss vss nmos L=2u W=7u AS=49p AD=49p PS=26u PD=26u

划分 RTL描述仿

真

A

模拟单元技 术规范

结构选择电 路设计

B

24

约束 综合库 扫描链/BIST配置

测试向量 仿真库

物理约束 单元库

A

逻辑综合

门级混合仿 真

版图规划

布局 RC延时估计

C

定时估计

B 设计仿真

模拟单元模型 定时估计

版图设计

E

物理验证 RC分布参数

提取

后仿真

D

25VS, DRC,ERC)

TapeOut

网表 定时信息

D

模拟单元模 型修正

定时验证

OK?

E

26

2020/1/3

27

保持时间

功能定义:真值表、状态图,… 模拟指标:频率响应、电源抑制比、共模抑制比、稳

定时间、增益、增益误差,…

其他:

ESD,I/O电容、测量条件、引脚对应、封装形式,…

12

电路设计时应当考虑 工艺参数:每一层的厚度… 工艺流程: 电气参数:阈值电压、最大耐压、方块电阻、 方块电容、温度系数… 设计规则: 晶体管模型参数

7

后仿真

实际的互连线有阻抗特性,对原有电路的功能/ 性能有影响, 完整的设计必须考虑互连线对电路的影响; 准确的互连线模型才能得到准确的仿真结果; 完整的互连线模型是分布参数模型,在仿真时必 须考虑分布参数元件的缩减 后仿真包括RC分布参数提取和仿真

8

信号完整性分析

集成电路中线间距很小、一个信号线上的信号变 化可能影响其他信号的波形; 集成电路所有元件加工在同一个衬底上,干扰信 号可能通过衬底影响其它元件; 集成电路上的电源和地用金属线连接到所有元件 上,金属线上的分布电感可以把电流的变化转换 成电压的变化而影响电路的工作;

13

2020/1/3

14

设计容限

制造误差:

Fast

Typical

Slow

温度变化:

0 ℃ -25 ℃ -70 ℃(商业)

-55 ℃ -25 ℃ -125℃(军品)

电源变化:

VDDX(1+/-10%)

Desing Conner

VDD ,T , fast PMOS, fast NMOS

VDD ,T , slow PMOS, slow NMOS

4

仿真

根据给定的元件模型验证所设计电路的功能和指标 提供电路参数修改的依据 根据模拟结果得到版图设计的依据:电源线宽… 根据工艺参数误差确定电路的工作范围和限制 验证环境变化对电路特性的影响

5

版图设计

将电路转换成集成电路加工所需要的几何图形描述

6

版图验证

每个工艺都有其设备和控制上的极限,如:光解析度、化 学药品浓度、温度、时间…;版图设计必须能够适应工艺 流程合理的差异,在版图设计过程中要符合代工厂的要求 设计规则。 电路设计和版图设计是设计过程中不同的阶段,必须确认 电路与版图之间的映射关系。

全定制集成电路 设计流程

1

2

确定技术规范

系统级建模

测试向量 单元模型

测试向量 单元模型

模块技术规范 仿真

布局

单元库

后仿真 满足规范要求?

版图验证 RC参数提取

设计规则

生产

3

电路设计

根据技术规范选择合适的结构 根据结构选择元件的组合 根据交直流参数要求确定晶体管的大小和工作点 根据环境确定负载类型和大小