应用VHDL语言设计八位二进制加法器

8位加法器的设计

实验二8位加法器的设计1.实验目的:(1)学习使用Quartus II软件的基本用法(2)了解和掌握VHDL语言的语法规则和编程方法及基本流程(3)了解VHDL语言的基本结构(4)掌握元件例化设计思想2.实验内容设计一个由两个4位二进制并行加法器级联而成的8位加法器。

参考设计方案:加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器都可由加法器来构成。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有进位产生逻辑,运算速度较快;串行进位方式是将全加器级联构成多位加法器。

并行进位加法器通常比串行级联加法器占用更多的资源。

随着位数的增加,相同位数的并行加法器与串行加法器的资源占用差距也越来越大。

因此,在工程中使用加法器时,要在速度和容量之间寻找平衡点。

实践证明,4位二进制并行加法器和串行级联加法器占用几乎相同的资源。

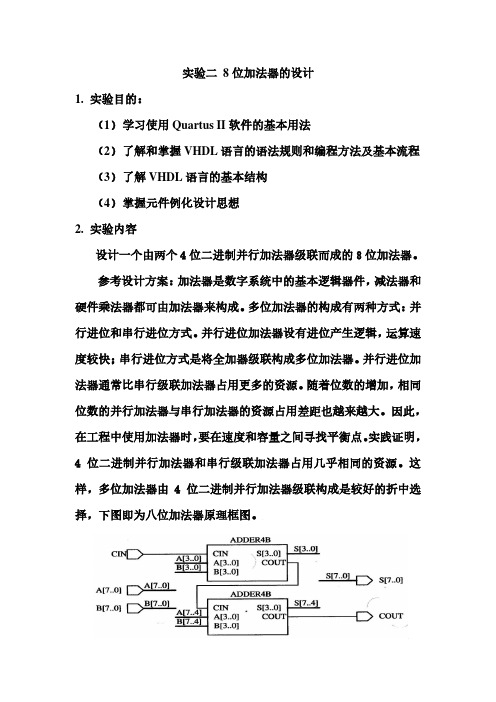

这样,多位加法器由4位二进制并行加法器级联构成是较好的折中选择,下图即为八位加法器原理框图。

3.实验要求(1)画出系统的RTL原理框图,说明系统中个主要成分的功能(2)编写VHDL程序(3)进行系统时序仿真,画出时序图(4)记录实验过程中遇到的问题及解决办法4.程序设计5.生成RTL电路图如图所示,一个8位加法器由2个4位二进制并行加法器级联构成,4位二进制并行加法器U1的进位输出串接在U2的低位进位CIN上,4位二进制并行加法器U1的输入是A、B、CIN,4位二进制并行加法器U2的输入是A、B和由U1来的进位CONT,从而得到一个8位全加器。

6.仿真波形7.实验心得在本次实验中我遇到的问题是,刚开始我以为只要把4位二进制并行加法器和8位二进制加法器的VHDL程序代码全打在ADDER8B 中编译就可以了,这样做虽然也能够编译成功,但是,结果是,Quartus II软件只默认编译的第一个源程序,也就是4位二进制并行加法器的源程序。

结果我尝试了很久才发现,原来要把两个.vhd文件分开书写,并且8位二进制加法器的顶层文件名要与程序的实体名称一致。

EDA实验六8位二进制全加法器的设计说明

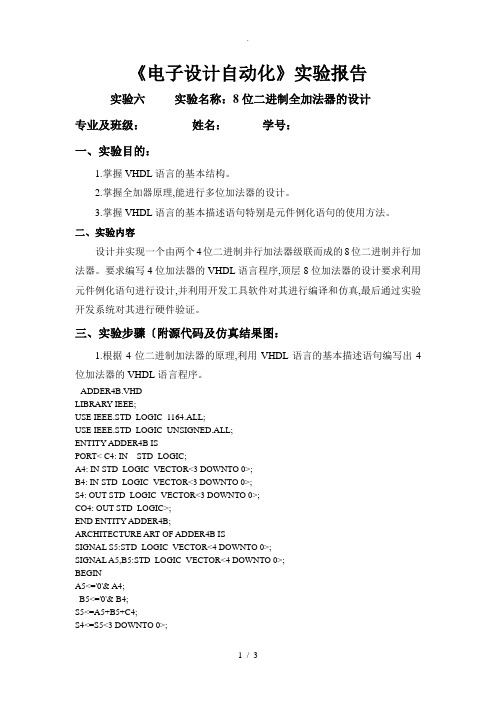

《电子设计自动化》实验报告实验六实验名称:8位二进制全加法器的设计专业及班级:姓名:学号:一、实验目的:1.掌握VHDL语言的基本结构。

2.掌握全加器原理,能进行多位加法器的设计。

3.掌握VHDL语言的基本描述语句特别是元件例化语句的使用方法。

二、实验内容设计并实现一个由两个4位二进制并行加法器级联而成的8位二进制并行加法器。

要求编写4位加法器的VHDL语言程序,顶层8位加法器的设计要求利用元件例化语句进行设计,并利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

三、实验步骤〔附源代码及仿真结果图:1.根据4位二进制加法器的原理,利用VHDL语言的基本描述语句编写出4位加法器的VHDL语言程序。

--ADDER4B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER4B ISPORT< C4: IN STD_LOGIC;A4: IN STD_LOGIC_VECTOR<3 DOWNTO 0>;B4: IN STD_LOGIC_VECTOR<3 DOWNTO 0>;S4: OUT STD_LOGIC_VECTOR<3 DOWNTO 0>;CO4: OUT STD_LOGIC>;END ENTITY ADDER4B;ARCHITECTURE ART OF ADDER4B ISSIGNAL S5:STD_LOGIC_VECTOR<4 DOWNTO 0>;SIGNAL A5,B5:STD_LOGIC_VECTOR<4 DOWNTO 0>;BEGINA5<='0'& A4;B5<='0'& B4;S5<=A5+B5+C4;S4<=S5<3 DOWNTO 0>;CO4<=S5<4>;END ARCHITECTURE ART;2.对所设计的4位二进制加法器的VHDL程序进行编译,然后对其进行仿真,初步验证程序设计的正确性。

8位二进制加法计算器

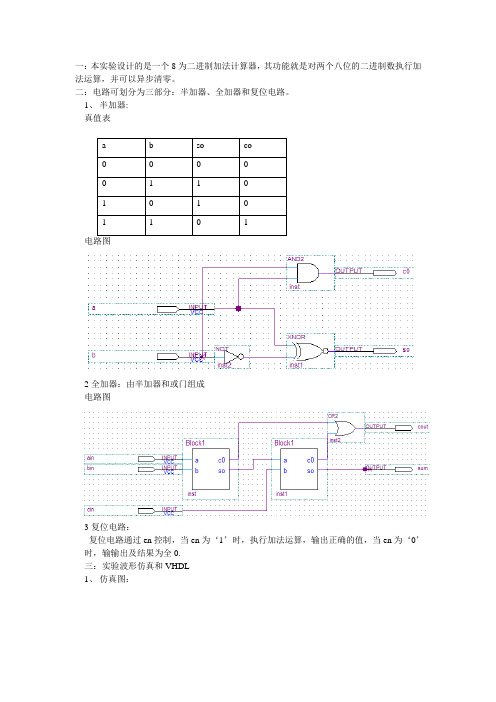

一:本实验设计的是一个8为二进制加法计算器,其功能就是对两个八位的二进制数执行加法运算,并可以异步清零。

二:电路可划分为三部分:半加器、全加器和复位电路。

1、半加器:真值表a b so co0 0 0 00 1 1 01 0 1 01 1 0 1电路图2全加器:由半加器和或门组成电路图3复位电路:复位电路通过en控制,当en为‘1’时,执行加法运算,输出正确的值,当en为‘0’时,输输出及结果为全0.三:实验波形仿真和VHDL1、仿真图:2、VHDL代码1)半加器h_adder:library ieee;use ieee.std_logic_1164.all;entity h_adder isport (a,b :in std_logic;co,so :out std_logic);end entity h_adder;architecture fh1 of h_adder isbeginso <= not(a xor (not b));co <= a and b ; end architecture fh1;2)或门or2a:library ieee;use ieee.std_logic_1164.all;entity or2a isport (a,b :in std_logic;c: out std_logic);end entity or2a;architecture one of or2a isbeginc <= a or b ;end architecture one;3)全加器f_adder:library ieee;use ieee.std_logic_1164.all;entity f_adder isport (ain,bin,cin:in std_logic;cout,sum:out std_logic);end entity f_adder;architecture fd1 of f_adder iscomponent h_adderport (a,b :in std_logic;co,so :out std_logic);end component;component or2aport (a,b :in std_logic;c: out std_logic);end component;signal d,e,f: std_logic;beginu1:h_adder port map(a=>ain,b=>bin,co=>d,so=>e);u2:h_adder port map(a=>e,b=>cin,co=>f,so=>sum);u3: or2a port map(a=>d,b=>f,c=>cout);end architecture fd1;4)与门and2a:library ieee;use ieee.std_logic_1164.all;entity and2a isport (a,b :in std_logic;c: out std_logic);end entity and2a;architecture one of and2a isbeginc <= a and b ;end architecture one;5)顶层设计文件library ieee;use ieee.std_logic_1164.all;entity zong isport (a1,a2,a3,a4,a5,a6,a7,a8,b1,b2,b3,b4,b5,b6,b7,b8,en :in std_logic;solution1,solution2,solution3,solution4,solution5,solution6,solution7,solution8,solution9 :out std_logic );end entity zong;architecture fh1 of zong iscomponent h_adderport (a,b :in std_logic;co,so :out std_logic);end component;component f_adderport (ain,bin,cin:in std_logic;cout,sum:out std_logic);end component;component and2aport (a,b :in std_logic;c: out std_logic);end component;signale2,e3,e4,e5,e6,e7,e8,e9,e10,e11,e12,e13,e14,e15,e16,e17,e18,e19,e20,e21,e22,e23,e24 :std_logi c;beginu1:and2a port map(a=>en,b=>a1,c=>e2);u2:and2a port map(a=>en,b=>a2,c=>e3);u3:and2a port map(a=>en,b=>a3,c=>e4);u4:and2a port map(a=>en,b=>a4,c=>e5);u5:and2a port map(a=>en,b=>a5,c=>e6);u6:and2a port map(a=>en,b=>a6,c=>e7);u7:and2a port map(a=>en,b=>a7,c=>e8);u8:and2a port map(a=>en,b=>a8,c=>e9);u9:and2a port map(a=>en,b=>b1,c=>e10);u10:and2a port map(a=>en,b=>b2,c=>e11);u11:and2a port map(a=>en,b=>b3,c=>e12);u12:and2a port map(a=>en,b=>b4,c=>e13);u13:and2a port map(a=>en,b=>b5,c=>e14);u14:and2a port map(a=>en,b=>b6,c=>e15);u15:and2a port map(a=>en,b=>b7,c=>e16);u16:and2a port map(a=>en,b=>b8,c=>e17);u17:h_adder port map(a=>e2,b=>e10,co=>e18,so=>solution1);u18:f_adder port map(ain=>e3,bin=>e11,cin=>e18,cout=>e19,sum=>solution2);u19:f_adder port map(ain=>e4,bin=>e12,cin=>e19,cout=>e20,sum=>solution3);u20:f_adder port map(ain=>e5,bin=>e13,cin=>e20,cout=>e21,sum=>solution4);u21:f_adder port map(ain=>e6,bin=>e14,cin=>e21,cout=>e22,sum=>solution5);u22:f_adder port map(ain=>e7,bin=>e15,cin=>e22,cout=>e23,sum=>solution6);u23:f_adder port map(ain=>e8,bin=>e16,cin=>e23,cout=>e24,sum=>solution7);u24:f_adder port map(ain=>e9,bin=>e17,cin=>e24,cout=>solution9,sum=>solution8);end architecture fh1;。

第六讲2第6章 VHDL设计应用实例(8位加法器的设计)

东北石油大学

第6章

VHDL设计应用实例

东北石油大学

第6章

VHDL设计应用实例

这时,MAX+plus II调出编译器对ADDER4.VHD进行编 译,编译后生成ADDER4的图形符号。如果源程序有 错,要对源程序进行修改,重复上面的步骤,直到此 元件符号创建成功。 点击File\Project\set project to current file设置此项目为当

2. 内容 设计并调试好一个由两个4位二进制并行加法器级

联而成的8位二进制并行加法器,并用EDA实验开发系

统进行硬件验证。

东北石油大学

第6章

VHDL设计应用实例

3. 要求 (1) 画出系统的原理框图,说明系统中各主要组成

部分的功能。

(2) 编写各个VHDL源程序。 (3) 根据选用的软件编好用于系统仿真的测试文件。 (4) 根据选用的软件及EDA实验开发装置编好用于 硬件验证的管脚锁定文件。 (5) 记录系统仿真、硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

东北石油大学

第6章

VHDL设计应用实例

输入4位并行加法器源程序后,选择菜单“Flie→Save”, 即出现如图所示的对话框。 文件存盘后,为了能在图形编辑器中调用,自动 为ADDER4创建一个元件图形符号。或选择菜单 “File”→“Create Default Symbol”,出现如图所示的对

话框,询问是否将当前工程设为ADDER4,可按下

东北石油大学

第6章

VHDL设计应用实例

3.硬件逻辑验证 选择实验电路结构图如6.1,由图6.1确定引脚的锁

定。如可取实验电路结构图的PIO3~PIO0接A8[3..0],

EDA8位二进制并行加法器

实验二:8位加法器的设计1.实验目的(1)学习Quartus Ⅱ/ISE Suite/ispLEVER软件的基本使用方法。

(2)学习GW48-CK或其他EDA实验开发系统的基本使用方法。

(3)了解VHDL程序的基本结构。

2.实验内容设计并调试好一个由两个4位二进制加法器级联而成的8位二进制并行加法器,并用GW48-CK或其他EDA实验开发系统(事先应选定拟采用的实验芯片的型号)进行硬件验证。

3.实验要求(1)画出系统的原理图,说明系统中各主要组成部分的功能。

(2)编写各个VHDL源程序。

(3)根据系统的功能,选好测试用例,画出测试输入信号波形或编号测试程序。

(4)根据选用的EDA实验开发装置编好用于硬件验证的管脚锁定表格或文件。

(5)记录系统仿真、逻辑综合及硬件验证结果。

(6)记录实验过程中出现的问题及解决办法。

4.实验条件(1)开发条件:Quartus Ⅱ 8.0。

(2)实验设备:GW48-CK实验开发系统。

(3)拟用芯片:EPM7128S-PL84。

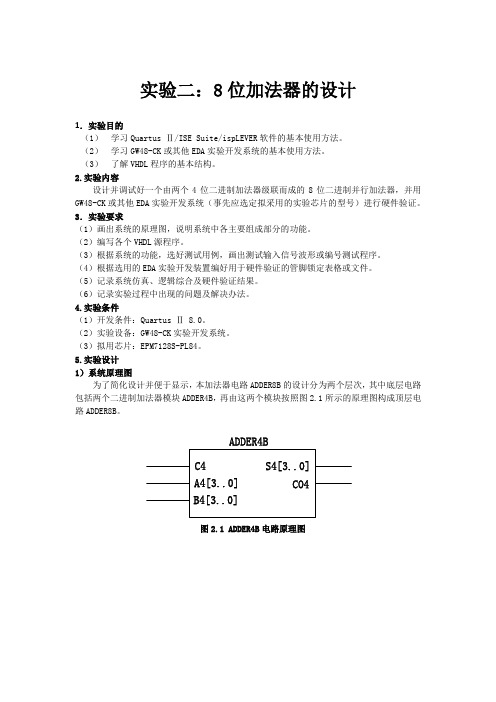

5.实验设计1)系统原理图为了简化设计并便于显示,本加法器电路ADDER8B的设计分为两个层次,其中底层电路包括两个二进制加法器模块ADDER4B,再由这两个模块按照图2.1所示的原理图构成顶层电路ADDER8B。

ADDER4B图2.1 ADDER4B电路原理图A8[7..0]图 2.1 ADDER8B电路原理图2)VHDL程序加法器ADDER8B的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。

ADDER4B的VHDL源程序:--ADDER4B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER4B ISPORT(C4:IN STD_LOGIC;A4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO4: OUT STD_LOGIC);END ENTITY ADDER4B;ARCHITECTURE ART OF ADDER4B ISSIGNAL S5:STD_LOGIC_VECTOR(4 DOWNTO 0);SIGNAL A5,B5:STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINA5<='0'&A4;B5<='0'&B4;S5<=A5+B5+C4;S4<=S5(3 DOWNTO 0);CO4<=S5(4);END ARCHITECTURE ART;ADDER8B的VHDL源程序:--ADDER8B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER8B ISPORT(C8: IN STD_LOGIC;A8: IN STD_LOGIC_VECTOR(7 DOWNTO 0);B8: IN STD_LOGIC_VECTOR(7 DOWNTO 0);S8: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);CO8: OUT STD_LOGIC );END ENTITY ADDER8B;ARCHITECTURE ART OF ADDER8B ISCOMPONENT ADDER4B ISPORT(C4: IN STD_LOGIC;A4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);B4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);S4: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO4: OUT STD_LOGIC );END COMPONENT ADDER4B;SIGNAL SC: STD_LOGIC;BEGINU1:ADDER4B PORT MAP(C4=>C8,A4=>A8(3 DOWNTO 0),B4=>B8(3 DOWNTO 0),S4=>S8(3 DOWNTO 0),CO4=>SC);U2:ADDER4B PORT MAP(C4=>SC,A4=>A8(7 DOWNTO 4),B4=>B8(7 DOWNTO 4),S4=>S8(7 DOWNTO 4),CO4=>CO8);END ARCHITECTURE ART;CTRLS的VHDL程序--CTRLS.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CTRLS ISPORT(CLK: IN STD_LOGIC;SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END ENTITY CTRLS;ARCHITECTURE ART OF CTRLS ISSIGNAL CNT:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINPROCESS(CLK) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CNT="111" THENCNT<="000";ELSECNT<=CNT+'1';END IF;END IF;END PROCESS;SEL<=CNT;END ARCHITECTURE ART;DISPLAY的VHDL程序--DISPLAY.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DISPLAY ISPORT( SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0); -- DATAIN: IN STD_LOGIC_VECTOR(15 DOWNTO 0); DATAIN: IN STD_LOGIC_VECTOR(7 DOWNTO 0); COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --LEDW: OUT STD_LOGIC_VECTOR(2 DOWNTO 0); SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END ENTITY DISPLAY;ARCHITECTURE ART OF DISPLAY ISSIGNAL DATA: STD_LOGIC_VECTOR(3 DOWNTO 0);-- SIGNAL DATA: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINP1:PROCESS(SEL) ISBEGINCASE SEL ISWHEN"000"=>COM<="11111110";WHEN"001"=>COM<="11111101";WHEN"010"=>COM<="11111011";WHEN"011"=>COM<="11110111";WHEN"100"=>COM<="11101111";WHEN"101"=>COM<="11011111";WHEN"110"=>COM<="10111111";WHEN"111"=>COM<="01111111";WHEN OTHERS=>COM<="11111111";END CASE;END PROCESS P1;--LEDW<=SEL;P2:PROCESS(SEL)BEGINCASE SEL ISWHEN"000"=>DATA<=DATAIN(3 DOWNTO 0);WHEN"001"=>DATA<=DATAIN(7 DOWNTO 4);-- WHEN"010"=>DATA<=DATAIN(11 DOWNTO 8);-- WHEN"011"=>DATA<=DATAIN(15 DOWNTO 12); WHEN OTHERS=>DATA<="0000";END CASE;CASE DATA ISWHEN"0000"=>SEG<="00111111";WHEN"0001"=>SEG<="00000110";WHEN"0010"=>SEG<="01011011";WHEN"0011"=>SEG<="01001111";WHEN"0100"=>SEG<="01100110";WHEN"0101"=>SEG<="01101101";WHEN"0110"=>SEG<="01111101";WHEN"0111"=>SEG<="00000111";WHEN"1000"=>SEG<="01111111";WHEN"1001"=>SEG<="01101111";WHEN OTHERS=>SEG<="00000000";END CASE;END PROCESS P2;END ARCHITECTURE ART;ADDER8B动态扫描的VHDL程序--ADDER8B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER8B ISPORT(C8: IN STD_LOGIC;A8: IN STD_LOGIC_VECTOR(7 DOWNTO 0);B8: IN STD_LOGIC_VECTOR(7 DOWNTO 0);CLK:IN STD_LOGIC;-- S8: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); S8: BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0); CO8: OUT STD_LOGIC ;COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END ENTITY ADDER8B;ARCHITECTURE ART OF ADDER8B IS--COMPONENT ADDER4BCOMPONENT ADDER4B ISPORT(C4: IN STD_LOGIC;A4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);B4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);S4: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO4: OUT STD_LOGIC );END COMPONENT ADDER4B;--COMPONENT CTRLSCOMPONENT CTRLS ISPORT(CLK: IN STD_LOGIC;SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END COMPONENT CTRLS;--COMPONENT DISPLAYCOMPONENT DISPLAY ISPORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);--DATAIN: IN STD_LOGIC_VECTOR(15 DOWNTO 0);DATAIN: IN STD_LOGIC_VECTOR(7 DOWNTO 0);COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT DISPLAY;SIGNAL SC: STD_LOGIC;SIGNAL SB: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINU1:ADDER4B PORT MAP(C4=>C8,A4=>A8(3 DOWNTO 0),B4=>B8(3 DOWNTO 0),S4=>S8(3 DOWNTO 0),CO4=>SC);U2:ADDER4B PORT MAP(C4=>SC,A4=>A8(7 DOWNTO 4),B4=>B8(7 DOWNTO 4),S4=>S8(7 DOWNTO 4),CO4=>CO8);U3:CTRLS PORT MAP(CLK,SB);U4:DISPLAY PORT MAP(SB,S8(7 DOWNTO 0),COM(7 DOWNTO 0),SEG(7 DOWNTO 0));END ARCHITECTURE ART;3)仿真波形设置本设计包括两个层次,因此先进行底层的二进制加法器ADDER4B的仿真,再进行顶层ADDER8B的仿真。

8位全加器

目录一、设计目的和要求 (1)1.课程设计目的 (1)2.课程设计的基本要求 (1)3.课程设计类型 (1)二、仪器和设备 (1)三、设计过程 (1)1.设计内容和要求 (1)2.设计方法和开发步骤 (2)3.设计思路 (2)4.设计难点 (4)四、设计结果与分析 (4)1.思路问题以及测试结果失败分析 (4)2.程序简要说明 (5)五、心得体会 (9)六、参考文献 (9)一、设计目的和要求1.课程设计目的设计一个带进位的八位二进制加法计数器:要求在MAX+plusⅡ10.2软件的工作平台上用VHDL语言层次设计出一个带进位的八位二进制加法器,并通过编译及时序仿真检查设计结果。

2.课程设计的基本要求全加器与带进位输入8位加法器设计要求我们通过8位全加器的设计掌握层次化设计的方法,充分理解全加器的设计过程,掌握一位全加器的程序,熟悉MAX+plusⅡ10.2软件的文本和原理图输入方法设计简单组合电路。

课程设计过程中要求能实现同步和异步的八位二进制全加器的设计。

3.课程设计类型EDA课程设计二、仪器和设备PC机、MAX+plusⅡ10.2软件三、设计过程1.设计内容和要求方法一:1.原理图输入完成半加器和1位全加器的设计,并封装入库2.层次化设计,建立顶层文件,由8个1位全加器串联构成8位全加器3.每一层次均需进行编译、综合、适配及仿真方法二:1. 原理图输入完成一个四位全加器的设计2.层次化设计,建立顶层文件,由2个4位全加器串联构成8位全加器3.每一层次均需进行编译、综合、适配及仿真2.设计方法和开发步骤加法器是数字系统中的基本逻辑器件。

例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。

但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

EDA与VHDL实现8位加法器

EDA技术与VHDL实训姓名:李*班级:电信**-*学号:12********电子与信息工程学院8位加法器设计一实训目的1.学习使用VHDL语言设计电路,加深对VHDL语言的理解与应用。

2.学习8位加法器的VHDL程序设计方法。

3.学习例化语句的应用,并能够利用例化语句完成从半加器到全加器的设计。

二加法器加法器是为了实现加法的。

即是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

对于1位的二进制加法,相关的有五个的量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。

前三个量为输入量,后两个量为输出量,五个量均为1位。

对于32位的二进制加法,相关的也有五个量:1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。

这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT 提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。

而最后的第32位必须在前31位全部计算出结果后,才能开始计算。

这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

三实训内容首先设计半加器,然后用例化语句将它们连接起来。

利用半加器和或门构成1位全加器,以1位全加器为基本硬件,构成串行进位的8位加法器。

3.1 设计1位半减器利用真值表设计1位半减器。

图3-1中的h_add是半加器,sum是输出和,a_out是进位输出,add_in是进位输入。

EDA2实验4-8位加法器的设计

实验四八位加法器的设计一、实验目的(1)进一步熟悉和掌握Quartus II 软件的使用。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的基本使用方法。

(3)学习VHDL程序的基本构成。

二、实验内容设计并调试好一个由两个4位二进制并行加法器级联而成的8位二进制并行加法器,并用GW48-CK或其他EDA实验开发系统进行硬件验证。

三、实验条件(1)开发软件:Quartus II 9.0(2)实验设备:W48-CK EDA实验开发系统。

四、实验原理加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器都可以由加法器来构成。

多位加法器的构成有两种方式:并行进位和串行进位。

并行进位加法器设有进位产生逻辑,运算速度较快;串行进位方式是将全加器级联构成多位加法器。

并行进位加法器通常比串行级联加法器占用更多的资源。

随着位数增加。

相同位数的并行加法器与串行加法器的资源占用差距也越来越大。

因此,在工程中使用加法器时,要在速度和容量之间寻找平衡点。

实践证明,4位二进制并行加法器和串行级联加法器占用几乎相同的资源,这样,多位加法器由4位二进制并行加法器级联构成是较好的折中选择。

本设计中的8位二进制并行加法器即是由两个4位二进制并行加法器级联而成的,其电路原理图如图所示。

五、实验设计VHDL程序(1)4位二进制并行加法器的源程序ADDER4B.VHD library ieee;use ieee.std_logic_1164.all;use ;entity ADDER4B isport (C4:in std_logic;A4:in std_logic_vector (3 downto 0);B4:in std_logic_vector (3 downto 0);S4:out std_logic_vector (3 downto 0);CO4:out std_logic);end entity ADDER4B;architecture ART of ADDER4B issignal S5:std_logic_vector (4 downto 0);signal A5,B5:std_logic_vector (4 downto 0);beginA5<='0'&A4;B5<='0'&B4;S5<=A5+B5+C4;S4<=S5(3 downto 0);CO4<=S5(4);end architecture ART;(2)8位二进制并行加法器的源程序ADDER8B.VHD library ieee;use ieee.std_logic_1164.all;use ;entity ADDER8B isport (C8:in std_logic;A8:in std_logic_vector (7 downto 0);B8:in std_logic_vector (7 downto 0);S8:out std_logic_vector (7 downto 0);CO8:out std_logic);end entity ADDER8B;architecture ART of ADDER8B iscomponent ADDER4B isport (C4:in std_logic;A4:in std_logic_vector (3 downto 0);B4:in std_logic_vector (3 downto 0);S4:out std_logic_vector (3 downto 0);CO4:out std_logic);end component ADDER4B;signal SC:std_logic;beginU1:ADDER4Bport map (C4=>C8,A4=>A8 (3 downto 0),B4=>B8(3 downto 0),S4=>S8(3 downto 0),CO4=>SC);U2:ADDER4Bport map (C4=>SC,A4=>A8 (7 downto 4),B4=>B8(7 downto 4),S4=>S8(7 downto 4),CO4=>CO8);end architecture ART;仿真波形设置(1)4位二进制(2)8位二进制六、实验结果及总结(1)4位二进制功能仿真结果4位二进制时序仿真结果(2)8位二进制功能仿真结果8位二进制时序仿真结果从系统仿真的结果可以看出,程序的设计完全符合设计要求。

基于VHDL的8位模型计算机的设计与实现

摘要随着计算机在人们生活中重要性和不可或缺性的提高,为了更方便的为大众使用,发展计算机性能成为IT行业的热点,但计算机的部结构极其复杂,为了便于研究便产生了模型计算机。

本文完成了基于VHDL的8位模型计算机的设计与实现。

文中首先阐述了8位模型计算机的原理,然后对其十个功能模块〔算术逻辑运算单元,累加器,控制器,地址寄存器,程序计数器,数据寄存器,存储器,节拍发生器,时钟信号源,指令寄存器和指令译码器进行了分析与设计。

最后在Quartus II 9.0环境下进行了仿真,完成了8位模型计算机的整体实现。

本文综合了计算机组成原理和数字逻辑与系统设计的知识,设计的8位模型计算机能更方便的了解计算机部构造和工作原理。

整个系统的开发体现了在Quartus II软件平台上用VHDL设计数字控制系统的实用性。

关键词:8位模型机; Quartus II ;VHDL语言AbstractWith the improvement of importance and indispensability in computer in people's life,in order to use more conveniently for public ,computer performance is becoming a hot in the IT industry development.but the internal structure of the computer is very complicate,Computer model simplifies the difficulty of the research.This article completed the design and implementation of eight model computer based on VHDL.First ,this article expounds the principle of eight model computer,then divides it into 10 modules<arithmetic logic unit, accumulator, controllers, address register, the program counter and data registers, memory, beat generator, a clock signal, instruction register and instruction decoder>and analyse and design each of them.Finally under the environment of the Quartus II 9.0 simulation, completed overall implementation of the 8 model computer. The analysis and design of the eight model computer integrated the knowledge of computer constitute principle and Digital logic and system design. The design of the eight model computer can be more convenient to understand internal structure and working principle.The whole system development manifests the practicability of designing the numerical control system on the Quartus II software platform with VHDL.Key words:eight model computer ; VHDL language; Quartus II目录1 绪论11.1 本课题研究的目的11.2 本课题研究的背景及意义12 基于VHDL编程的基础知识32.1 VHDL语言概述32.2 VHDL的设计流程 (4)2.3 有关Quartus II 的介绍52.4 本课题基于Quartus II的设计流程73 基于VHDL8位模型机的原理与设计73.1 模型计算机的原理73.2 模型机的总体设计要求83.3 模型机逻辑框图的设计83.3 模型机的指令系统设计83.4 模型机的指令执行流程设计83.5 基于VHDL8位模型机各模块的设计与实现 (10)3.5.1 算术逻辑单元ALU模块103.5.2 累加器模块113.5.3 控制器模块123.5.4 节拍发生器143.5.5 指令寄存器模块IR和指令译码器163.5.6 时钟产生器173.5.7 程序计数器模块183.5.8 地址寄存器MAR203.5.9 存储器RAM213.5.10 数据寄存器DR224 基于VHDL的8位模型计算机的实现234.1 基于VHDL的微程序执行流程图234.2 8位模型机的顶层原理图设计244.3 基于VHDL的8位模型机工作流程244.4 顶层VHDL源程序设计254.4.1 头文件cpu_defs的VHDL设计254.4.2 CPU的VHDL源程序设计264.5 8位模型机的整体实现34结论34致 35参考文献36附录A 英文原文.......................................... 错误!未定义书签。

谭会生eda实验报告八位加法器

EDA实验报告学院:电气学院班级:电科1班学号:***********姓名:***实验二八位加法器是设计1.实验目的(1)进一步熟悉掌握Quartus Ⅱ。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的应用。

(3)学习和掌握VHDL进程语句和元件例化语句的使用。

2.实验内容设计并调试好8位加法器电路ADDER8B,并用GW48-CK或其他EDA实验开发系统进行硬件验证。

3.实验条件(1)开发软件:Quartus Ⅱ。

(2)实验设备:GW48-CK EDA实验开发系统。

(3)拟用芯片:EPM7128S-PL84.4.实验设计1)系统原理框图为了简化设计并便于显示,本累加器电路adder8b的设计分为两个层次,其底层电路包括4位二进制adder4b源程序,再由两个4位二进制并行加法器级联而成。

Adder4b电路图Adder8b电路图2)VHDL程序累加器adder8b的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。

Adder4b的VHDL源程序:--ADDER4B.VHDLIBARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.SLL;ENTITY ADDER4B IS --4位二进制并行加法器PORT(C4:IN STD_LOGIC; --低位来的进位A4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --4位加数B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --4位被加数S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --4位和CO4:OUT STD_LOGIC); --进位输出END ENTITY ADDER4B;ARCHITECTURE ART OF ADDER4B ISSIGNAL S5:STD_LOGIC_VECTOR(4 DOWNTO 0);SIGNAL A5,B5:STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINA5<=0& A4; --将4位加数矢量扩为5位,为进位提供空间B5<=0& B4; --将4位被加数矢量扩为5位,为进位提供空间S5<=A5+B5+C4;S4<=S5(3 DOWNTO 0);CO4<=S5(4);END ARCHITECTURE ART;Adder8b的VHDL源程序:--ADDER8B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.SLL;ENTITY ADDER8B IS --4位二进制加法器级联成8位二进制加法器PORT(C8:IN STD_LOGIC;A8:IN STD_LOGIC_VECTOR(7 DOWNTO 0);B8:IN STD_LOGIC_VECTOR(7 DOWNTO 0);S8:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);CO8:OUT STD_LOGIC);END ENTITY ADDER8B;ARCHITECTURE ART OF ADDER8B ISCOMPONENT ADDER4B IS --对要调用的ADDER4B定义界面端PORT(C4:IN STD_LOGIC;A4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO4:OUT STD_LOGIC);END COMPONENT ADDER4B;SIGNAL SC:STD_LOGIC; --4位加法器的进位标志BEGINU1:ADDER4B --例化(安装)一个4位二进制加法器U1PORT MAP(C4=>C8,A4=>A8(3 DOWNTO 0),B4=>B8(3 DOWNTO 0),S4=>S8(3 DOWNTO 0),CO4=>SC);U2:ADDER4B --例化(安装)一个4位二进制加法器U2PORT MAP(C4=>C8,A4=>A8(7 DOWNTO 4),B4=>B8(7 DOWNTO 4),S4=>S8(7 DOWNTO 4),CO4=>CO8);END ARCHITECTURE ART;3)仿真波形设置本程序包括两个程序,因此先进行底层的累加器adder4b的方针,在进行顶层adder8b的仿真,下图为adder4b的输入设置及可能结果估计图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

§4.2 完成工作任务的引导

一、资讯

要完成应用VHDL语言设计出一个八位二进制加法器,请大家 认真阅读4.3节所介绍的基本内容,并复习3.2节的有关介绍。

二、计划

类似3.2节中提出有3种应用原理图设计输入法实现八位二进制

加法器的方案,应用VHDL语言设计八位二进制加法器也有多种

方案。

第一种方案:以8个全加器为底层模块,用VHDL语言层次设计

法设计八位二进制加法器。

第二种方案:运用在程序包ieee.std_logic_signed中定义

的标准逻辑位矢量的加法来设计八位二进制加法器。

下一页

§4.2 完成工作任务的引导

第三种方案:应用VHDL语言设计法中的LPM方法来设计八位 二进制加法器。

三、决策

第一种方案与第3章的第一种方案相似,其实这种方案不是设计 上最简单的方案,也不是性能最好的方案。但它所应用的层次设计 法是VHDL语言设计中重要的一种方法,建议大家应用这种方法做 一次。

第4章 应用VHDL语言方法设计 八位二进制加法器

【要求】

应用VHDL语言设计八位二进制加法器

【知识点】•ຫໍສະໝຸດ 应用VHDL语言设计八位二进制加法器

•

掌握VHDL语言输入法

•

掌握VHDL语言层次化设计方法

【重点和难点】

应用VHDL语言设计八位二进制加法器

下一页

第4章 应用VHDL语言方法设计 八位二进制加法器

end add4;

上一页 下一页

§4.3 相关技术基础知识与基本技能

architecture b of add4 is signal ct:std_logic_vector(6 downto 0); component fulladd is

port(cin:in std_logic; a,b: in std_logic; s:out std_logic; cout:out std_logic);

begin crlt>=('0'&a)+('0'&b)+cin; s>=crlt(0); cout>=crlt(1);

End; (3)设计顶层设计文件

设计顶层设计文件add4.vhd,其中把全加器文件作为元件调用:

上一页 下一页

§4.3 相关技术基础知识与基本技能

library ieee; use ieee.std_logic_1164.all; entity add4 is

上一页 下一页

§4.3 相关技术基础知识与基本技能

对于弹出的选择其他EDA工具的对话框,由于我们使用 Quartus且的集成环境进行开发,因此不需做任何改动。单击Next 按钮进入如图4-11所示工程的信息总概对话框。

在图4-11中单击Finish按钮就建立了一个空的工程项目。 2.建立VHDL文件

2.仿真VHDL文件 执行File=>New,如图4-18所示,选择Other Files中的 Vector Waveform File ,然后确定。

上一页 下一页

§4.3 相关技术基础知识与基本技能

出现文件编辑器,如图4-19所示。 在图4-19中鼠标所在处单击鼠标右键,出现图4-20所示菜单,选 择InsertNode or Bus…命令。 出现图4-21所示的对话框,单击Node Finder…按键。 在出现的图4-22所示的对话框中单击List按键。此操作是在对话 框中Filter: 文本框显示Pins:all的情况下进行的;若此文本框不显示 Pins:all,请选择Pins:all项。 选择需要的输入输出引脚,如图4-23所示。 如图4-24所示,单击鼠标所点的按键,选中需要的输入输出引脚。

a,b : in std_logi; ---加数及被加数 s : out std_ logic; ---本位和

cout: out std logic); ---向高位的进位信号 End;

上一页 下一页

§4.3 相关技术基础知识与基本技能

architecture one of fulladd is signal crlt:std_logic_vector(1 downto 0);

四、实施

在应用第一种方案设计时,请参考下一节例4.1或例4.2。先设计 底层模块全加器,再在顶层文件中调用全加器元件,构成八位二进制 加法器。在应用第一种方案设计时,请参考下一节例4.3。

五、检查

对所设计的八位二进制加法器的各个底层模块和顶层模块进行编译 仿真,以验证所设计电路否符合设计的要求。

上一页 下一页

上一页 返 回

§4.3 相关技术基本知识与基本技能

一、 Quartus II的VHDL输入法

Quartus II 的常用输入法有原理图输入法和 HDL 输入法。 HDL 输入法又有AHDL, VHDL和Verilog HDL三种语言,本书 主要介绍VHDL语言。下面以全加器设计为例介绍 Quartus II 的 VHDL文件的输入编辑和编译仿真方法。

上一页 下一页

§4.3 相关技术基础知识与基本技能

然后,两次确定,出现如图4-25所示的画面。 执行Edit=>End Time命令,设置合适的时问,如图4-26所示。 执行Edit=>Grid Size命令,设置时问单位为100ns,如图427所示。 设置输入信号波形,保存文件,注意保存的波形文件名与工程的顶 层实体名要一致。执行Processing=>Start Simulation命令,进 行仿真,如图4-28所示。 仿真结果如图4-29所示。 认真核对输入输出波形,可检查设计的功能正确与否。

上一页 下一页

§4.3 相关技术基础知识与基本技能

(二)编译仿真VHDL文件 1.编译VHDL文件 执行Processing=>Start Compilation命令,如图4-16所示,

进行编译。 若通过,则弹出如图4-17所示对话框。 若不通过,先双击第一个错误提示,可使鼠标出现在第一个错误处

附近,检查纠正,第一个错误后保存再编译,如果还有错误,重复以 上操作,直至最后通过。

单击Family下拉框,根据需要选择器件的系列,比如Cyclone系 列FPGA 。然后在“Available devices:”中选择需要的器件的型 号,比如“EP1C3T144C8”,注意在Show in 'Available devices' list一栏中选上“Show Advanced Devices”以显 示所有的器件型号。单击Next按钮,出现如图4-10所示的对话框。

上一页 下一页

§4.3 相关技术基础知识与基本技能

二、VHDL层次化文件设计

VHDL层次化文件设计,就是将一个复杂的电路划分为若十模块, 再把较大的模块划分为较示的模块,先编写VHDL设计文件分别描写 每个较示的模块,再编写VHDL设计文件描写较大的电路模块,最后 编写顶层文件来描写整体电路。顶层文件把各个模块文件作为元件调 用,而较大的模块文件把较示的模块的文件作为元件调用。下面以四 位二进制加法器为例说明VHDL层次化文件设计方法。

end component; begin

上一页 下一页

§4.3 相关技术基础知识与基本技能

u0: fulladd port map(cin,a(0),b(0),s(0),ct(0)); ul: fulladd port map(ct(0),a(1),b(1),s(1),ct(1)); u2: fulladd port map(ct(1),a(2),b(2),s(2),ct(2)); u3: fulladd port map(ct(2),a(3),b(3),s(3),cout); end b;

设计全加器电路文件 fulladd.vhd:

上一页 下一页

§4.3 相关技术基础知识与基本技能

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_ signed.all; entity fulladd is port( cin : in std_logic; ---来自低位的进位信号

当然,对于四位二进制加法器而言,此法并非最好的描写方法,但 对于学习VHDL层次化文件设计来说,这是一个简单的能说明问题的 例子。

上一页 下一页

§4.3 相关技术基础知识与基本技能

【例4.1】用VHDL层次化文件设计法设计一个四位二进制加法 器。

(1)电路模块划分 根据算法分析,四位二进制加法器可由4个全加器构成,其原理 方框图如图4-30所示。 (2)设计底层设计文件

(一)输人编辑VHDL文件 1.建立工程项目 打开 Quartus II 软件,执行File => New Project Wizard 命令,建立工程,如图4-5所示。 执行该命令后,在所弹出的图4-6界面中单击Next按钮。

下一页

§4.3 相关技术基础知识与基本技能

然后,在弹出的指定工程名称对话框中,填写第一、第一和第二个 文本框的内容,如图4-7所示,其中第一、第一和第二个文本框分别 是工程项目口录、工程项目和工程项目顶层设计实体的名称。 单击Next按钮,出现如图4-8所示的添加工程文件对话框。 这单没有文件击添加,单击Next按钮进行下一步,选择FP GA器件 的型号,如图4-9所示。

将“Add file to current project”选项选上,使该文件 添加到刚建立工程中去,如图4-14所示。 3.编辑VHDL文件

在VHDL编辑器下输入编辑下面源代码,并保存,如图4-15 所示。 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_ signed.all; entity fulladd is port( cin : in std_ logic;----来自低位的进位