FPGA 用verilog语言写的花样流水灯包含四种变换

verilog- HDL实现流水灯

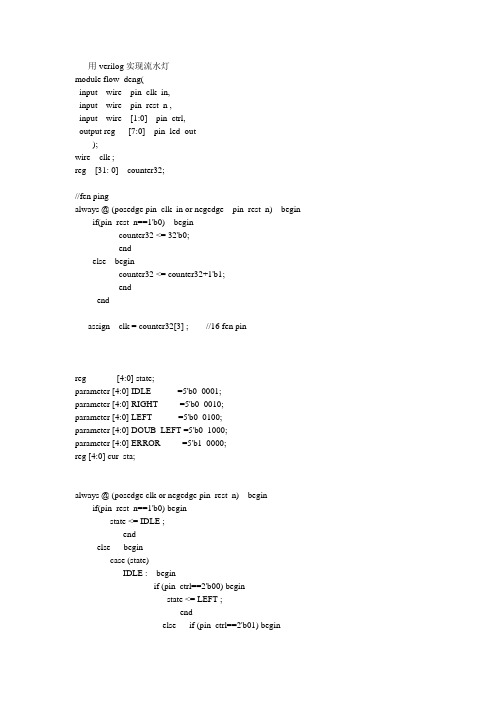

用verilog实现流水灯module flow_deng(input wire pin_clk_in,input wire pin_rest_n ,input wire [1:0] pin_ctrl,output reg [7:0] pin_led_out);wire clk ;reg [31: 0] counter32;//fen pingalways @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begincounter32 <= 32'b0;endelse begincounter32 <= counter32+1'b1;endendassign clk = counter32[3] ; //16 fen pinreg [4:0] state;parameter [4:0] IDLE =5'b0_0001;parameter [4:0] RIGHT =5'b0_0010;parameter [4:0] LEFT =5'b0_0100;parameter [4:0] DOUB_LEFT =5'b0_1000;parameter [4:0] ERROR =5'b1_0000;reg [4:0] cur_sta;always @ (posedge clk or negedge pin_rest_n) begin if(pin_rest_n==1'b0) beginstate <= IDLE ;endelse begincase (state)IDLE : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendLEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendRIGHT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendDOUB_LEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendERROR : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endenddefault: state <= IDLE ;endcaseendendalways @ (posedge clk or negedge pin_rest_n) beginif (pin_rest_n == 1'b0) beginpin_led_out[7:0]<=8'b0000_0000 ;endelse begincase (state)IDLE : beginpin_led_out [7:0] <=8'b0000_0000 ;endLEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out[7:0] <= 8'b0000_0001;endelse beginpin_led_out[7:1] <= pin_led_out[6:0];pin_led_out[0] <= pin_led_out[7];endendRIGHT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5 ]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out [7:0] <= 8'b0000_0001 ;endelse beginpin_led_out [6:0] <= pin_led_out [7:1] ;pin_led_out [7] <= pin_led_out [0] ;endendDOUB_LEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5] +pin_led_out[6]+pin_led_out[7])!=8'd2 ) beginpin_led_out [7:0] <= 8'b0000_0011 ;endelse beginpin_led_out [7:1] <= pin_led_out [6:0] ;pin_led_out [0] <= pin_led_out [7] ;endendERROR : beginpin_led_out [7:0]<=8'b1111_1111;enddefault : pin_led_out [7:0] <= 8'b0000_0000;endcaseendendendmodule。

基于FPGA的verilog的流水灯程序

基于FPGA的流水灯verilog程序`define cnt 17d7840 //cnt是计数量此处计时0.5s。

我调试的板子晶振频率是50MHZ。

32’h17d7840就是0.5s 。

这个十六进制的数值你可以用电脑自带的计数器转换的。

`define cnt_n 17d7841 //cnt值加一,用于下边的计数寄存器led_cnt的复位module led_new (clk,rest,led);input clk;input rest;output [7:0]led;reg [7:0]led;reg [7:0]led_n;reg [31:0] led_cnt;always@(posedge clk or negedge rest)beginif(!rest) led<=8'h80;else led<=led_n;endalways@(*)beginif(!rest) led_n=8'h00;else if(led_cnt==32'h`cnt) led_n={led[6:0],led[7]};else led_n=led;endalways@(posedge clk or negedge rest)beginif(!rest) led_cnt<=32'h0;else if(led_cnt==32'h`cnt_n) led_cnt<=32'h0;else led_cnt<=led_cnt+1'b1;endendmodule十进制数转换成十六进制的操作:先在电脑的开始》附件》计数器;打开计数器,点击“科学型”,窗口右边的键盘输入你想要的计数值,然后再点十六进制就行了QUARTUS II里面的引脚绑定其中clk是芯片内部时钟,仔细观察板子,观察晶振连进板子的那个引脚就是时钟引脚了。

我板子上边标示的是clk0/17。

注意:把程序复制进去的时候请把那些注释删掉,因为我写那些注释只是在WORD文档写而已的。

四种亮灯方式自由切换的跑马灯(用veriloghdl语言编写的跑马灯程序)

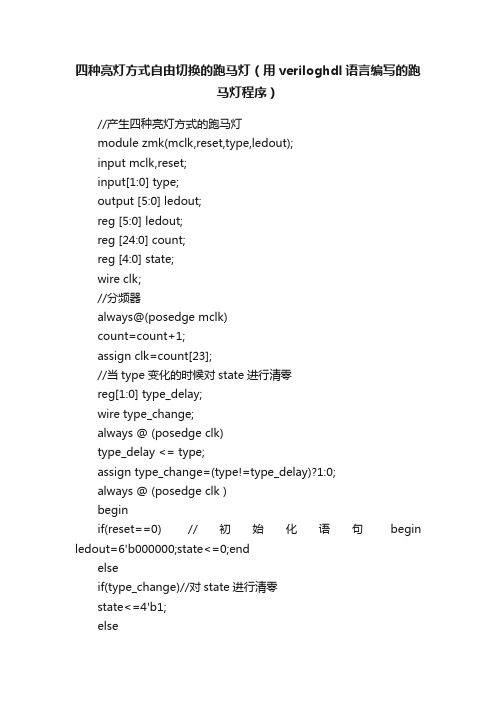

四种亮灯方式自由切换的跑马灯(用veriloghdl语言编写的跑马灯程序)//产生四种亮灯方式的跑马灯module zmk(mclk,reset,type,ledout);input mclk,reset;input[1:0] type;output [5:0] ledout;reg [5:0] ledout;reg [24:0] count;reg [4:0] state;wire clk;//分频器always@(posedge mclk)count=count+1;assign clk=count[23];//当type变化的时候对state进行清零reg[1:0] type_delay;wire type_change;always @ (posedge clk)type_delay <= type;assign type_change=(type!=type_delay)?1:0;always @ (posedge clk )beginif(reset==0) //初始化语句begin ledout=6'b000000;state<=0;endelseif(type_change)//对state进行清零state<=4'b1;elsebegincase(state)4'b0001:ledout=6'b011111;//第一个灯亮4'b0010:ledout=6'b101111;//第二个灯亮4'b0011:ledout=6'b110111;//第三个灯亮4'b0100:ledout=6'b111011;//第四个灯亮4'b0101:ledout=6'b111101;//第五个灯亮4'b0110:ledout=6'b111110;//第六个灯亮4'b0111:ledout=6'b111101;//第五个灯亮4'b1000:ledout=6'b111011;//第四个灯亮4'b1001:ledout=6'b110111;//第三个灯亮4'b1010:ledout=6'b101111;//第二个灯亮default :ledout=6'b000000;endcasestate=state+1; //计数器产生state的各种状态if(state==4'b1011)state=5'b00001;endelseif(type==2'b01)begincase(state)4'b0001:ledout=6'b101010;4'b0010:ledout=6'b010101;default :ledout=6'b000000;endcasestate=state+1;if(state==4'b0011)state=5'b00001;endelsebegincase(state)4'b0001:ledout=6'b110011;4'b0010:ledout=6'b101101;4'b0011:ledout=6'b011110;4'b0100:ledout=6'b101101; default :ledout=6'b000000; endcasestate=state+1;if(state==4'b0101)state=5'b00001; endelseif(type==2'b11)begincase(state)5'b00001:ledout=6'b111110;5'b00010:ledout=6'b111101;5'b00011:ledout=6'b111011;5'b00100:ledout=6'b110111;5'b00101:ledout=6'b101111;5'b00110:ledout=6'b011111;5'b00111:ledout=6'b001111;5'b01000:ledout=6'b010111;5'b01001:ledout=6'b011011;5'b01010:ledout=6'b011101;5'b01011:ledout=6'b011110;5'b01100:ledout=6'b011100;5'b01101:ledout=6'b011010;5'b01110:ledout=6'b010110;5'b01111:ledout=6'b001110;5'b10000:ledout=6'b000110;5'b10001:ledout=6'b001010;5'b10010:ledout=6'b001100;5'b10011:ledout=6'b001000;5'b10100:ledout=6'b000100;5'b10101:ledout=6'b001000;5'b10110:ledout=6'b000000;5'b10111:ledout=6'b111111;5'b11000:ledout=6'b000000;5'b11001:ledout=6'b111111;5'b11010:ledout=6'b000000;default :ledout=6'b000000;endcasestate=state+1;if(state==5'b11011)state=5'b00001; end endendmodule。

基于FPGA的流水灯

基于FPGA的流水灯概述流水灯是一种常见的电子实验项目,也是学习数字电路和FPGA编程的入门项目之一。

本文介绍了如何使用FPGA实现一个基于流水灯的电子项目。

需求流水灯项目的主要需求是将一组LED灯以一定的速率顺序点亮,然后逐个熄灭,再以同样的速率顺序点亮下一个LED 灯,如此循环。

硬件设计FPGA板在本项目中,我们使用一块支持FPGA编程的开发板。

可选的FPGA开发板包括Xilinx的Nexys 4或Digilent的Basys 3等。

LED灯流水灯需要一组LED灯来显示效果。

我们将使用FPGA开发板上的LED灯作为显示单元。

连接将LED灯的阳极连接到FPGA开发板的GPIO引脚上,并将其地连接到电路板上的公共地线。

软件设计硬件描述语言(HDL)HDL是一种用于描述数字电路和FPGA的语言。

常用的HDL包括VHDL和Verilog。

我们将使用Verilog作为本项目的HDL语言。

Verilog代码下面是一个基于FPGA的流水灯的Verilog代码示例:module led_shifter(input clk,output reg [7:0] leds);reg [25:0] counter;always @(posedge clk) begincounter <= counter + 1;if (counter == 26'd255) begincounter <= 0;leds <= leds << 1;endendendmodule上述Verilog代码中,我们定义了一个led_shifter模块,该模块接受一条时钟信号(clk)和一个用于控制LED灯的8位寄存器(leds)。

leds寄存器表示LED灯的状态,其中每个位代表一个LED灯。

在always块中,我们使用一个计数器counter来计算时钟脉冲的数量。

当计数器的值达到255时,即过了一定的时钟周期,我们将计数器重置为0,并将leds寄存器向左移动一位,即将下一个LED灯点亮。

最新verilog语言的FPGA变速花样流水灯设计

v e r i l o g语言的F PG A变速花样流水灯设计基于XILINX--XSE500E型FPGA的变速流水灯以及花样流水灯的verilog语言设计摘要临近大四毕业,诸多工科院校电子电科通信等专业会选择用FPGA项目作为课程设计的课题,笔者同样经历了这个过程,收获颇多,在此将设计成果在此分享,以帮助大家更好掌握FPGA设计。

FPGA种类繁多,时效性非常好,设计过程中十分注重实时性,在时间点控制上非常优秀。

此次设计采用XILINX的XSE500E型芯片的开发板,芯片采用FG320型接口,速度级别-4。

板载时钟50MHz,如需其他时钟周期,可采用IP 核中的clocking,其中的 DCM可以实现变频,引入DCM,输入频率50MHz,输出频率填入需要的频率即可,之后进行实例化。

此外,可以借助计数器进行延时减速,此次设计采用了计数器延时方法。

本次列举了四种流水灯相关设计:普通流水灯(向左和向右滚动),自动反复式流水灯(到最右端自动向左滚动,到左端自动向右滚动),花样流水灯,变速流水灯。

谢谢大家的支持!正文一,普通流水灯1,建模思想普通流水灯,可以向右滚动,到最右端返回最左端,也可以向左滚动,到最左端返回最右端。

普通流水灯模块涉及的端口有:clk,它是时钟输入,一般就是板载时钟,这里是50MHz,具体参照开发板说明。

还有复位输入rst,高电平有效。

此外就是led端口,这个端口有8根管脚,共8位,连接8个led灯。

采用verilog语言,端口定义格式如下:module led(input clk,input rst,output reg[7:0] led //此行定义说明led端口既是驱动管脚的,又是寄存器);采用过程建模,这里不采用行为建模和功能建模,因为这个过程就是一个大循环,规律性极强。

由于板载时钟50MHz,如果每个时钟周期都要滚动流水灯,那么速度是惊人的,人眼根本无法分辨。

所以采用计数器延时,当计数达到约4千万时候,驱动系统进行动作,可以判断,也可以进行流水灯动作。

verilog流水灯(注释版)

else

begin

count<=count+1; //开始计数

if(count==41'hff_ff_ff) //计数41 ’hff_ff_ff的时间结束,这时间是灯亮的持续时间

begin

led<=led>>1; //led移位输出

count<=0; //一个灯亮完归零,下一个灯重新计数

if(led==8'h0) //8个灯亮了个遍

led<=8'h80;//重新回到第一个灯

end

end

end

endmodule

// testbench.v

`timescale 1ns/1ns

module testbench();

reg clk;

reg rst;

wire [7:0] led;

parameter period = 20;//测试时钟频率

重新回到第一个灯endendendendmodule

verilog流水灯(注释版)

八个流水灯

/*功能描述:是八个led灯呈流水灯形式闪烁*/

module led(

clk48M, //48M时钟输入

RSTn, //复位信号,高电平复位?

led //led输出

);

input clk48M;

input RSTn;

always #(period/2) clk = ~c = 0;

rst = 0;

#10 rst = 1;

end

led led_0(.clk48M(clk),.RSTn(rst),.led(led)); endmodule

output[7:0] led;

verilog语言的FPGA变速花样流水灯设计

基于XILI NX--XSE500E型FPGA的变速流水灯以及花样流水灯的ve rilog语言设计摘要临近大四毕业,诸多工科院校电子电科通信等专业会选择用FP GA项目作为课程设计的课题,笔者同样经历了这个过程,收获颇多,在此将设计成果在此分享,以帮助大家更好掌握FP GA设计。

FPGA种类繁多,时效性非常好,设计过程中十分注重实时性,在时间点控制上非常优秀。

此次设计采用X ILINX的XSE500E型芯片的开发板,芯片采用FG320型接口,速度级别-4。

板载时钟50MHz,如需其他时钟周期,可采用IP核中的clo cking,其中的 DCM可以实现变频,引入DCM,输入频率50MHz,输出频率填入需要的频率即可,之后进行实例化。

此外,可以借助计数器进行延时减速,此次设计采用了计数器延时方法。

本次列举了四种流水灯相关设计:普通流水灯(向左和向右滚动),自动反复式流水灯(到最右端自动向左滚动,到左端自动向右滚动),花样流水灯,变速流水灯。

谢谢大家的支持!正文一,普通流水灯1,建模思想普通流水灯,可以向右滚动,到最右端返回最左端,也可以向左滚动,到最左端返回最右端。

普通流水灯模块涉及的端口有:clk,它是时钟输入,一般就是板载时钟,这里是50MHz,具体参照开发板说明。

还有复位输入r st,高电平有效。

此外就是le d端口,这个端口有8根管脚,共8位,连接8个le d灯。

采用veri log语言,端口定义格式如下:module led(inputclk,inputrst,output reg[7:0] led //此行定义说明l ed端口既是驱动管脚的,又是寄存器);采用过程建模,这里不采用行为建模和功能建模,因为这个过程就是一个大循环,规律性极强。

VHDL_fpga_数电实验_彩灯_LED_实验报告

彩灯VHDL设计在日常生活中,为了增加聚会或是过节氛围,经常要使用到彩灯循环点亮。

单一的循环可能无法起到理想的效果,通过不同花样的变换则能够很好的完成任务。

多路彩灯循环控制可以有多种实现方法,例如利用单片机可以实现,利用数字电路时序逻辑也可以实现。

我们这里利用VHDL语言实现对多路彩灯的控制。

彩灯的一种点亮方式经过足够长的延时后,转变为了其他的点亮方式。

这就需要一个CLK信号完成,CLK信号可以由晶体振荡器或者是振荡电路产生。

至于各种不同花样彩灯的变换,我们可以通过增加输入信号Sel来控制。

Sel为两位二进制数,分别为00,01,10,11,四种状态对应四种花样。

同时系统还需一个复位信号实现对电路的清零控制。

输出八位彩灯,我们这里用LED发光二极管代替。

当电路输出为“1”时,LED点亮。

当电路输出为“0”时,LED熄灭。

利用VHDL语言实现该功能程序如下:LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;USE IEEE.std_logic_ARITH.ALL;USE IEEE.std_logic_UNSIGNED.ALL;ENTITY cd ISport( clk,clk_use:in std_logic;rst:in std_logic;light:out std_logic_vector(7 downto 0));END cd;ARCHITECTURE control OF cd IStype states is (s0,s1,s2,s3,s4,s5);signal state:states;SIGNAL clk1ms:std_logic:='0';SIGNAL cnt1:std_logic_vector(3 downto 0):="0000";SIGNAL cnt2:std_logic_vector(3 downto 0):="0000";SIGNAL cnt3:std_logic_vector(2 downto 0):="000";SIGNAL cnt4:std_logic_vector(2 downto 0):="000";SIGNAL cnt5:std_logic_vector(3 downto 0):="0000";SIGNAL cnt6:std_logic_vector(3 downto 0):="0000";BEGINPROCESS(clk1ms)BEGINif clk1ms'event and clk1ms='1' thenif state=s0 then --第一种彩灯花样的程序if (cnt1="1111") thencnt1<="0000";else cnt1<= cnt1+1;end if;case cnt1 iswhen "0000"=>light<="10000000";when "0001"=>light<="10100000";when "0010"=>light<="10101000"; when "0011"=>light<="10101010"; when "0100"=>light<="11101010"; when "0101"=>light<="11111010"; when "0110"=>light<="11111110"; when "0111"=>light<="11111111"; when "1000"=>light<="11111110"; when "1001"=>light<="11111010"; when "1010"=>light<="11101010"; when "1011"=>light<="10101010"; when "1100"=>light<="10101000"; when "1101"=>light<="10100000"; when "1110"=>light<="10000000"; when others=>light<="00000000";end case;elsif state=s1 then -- 第二种彩灯花样的程序if cnt2="1111" thenCnt2<="0000";else cnt2<= cnt2+1;end if;case cnt2 iswhen "0000"=>light<="11111111"; when "0001"=>light<="01111111"; when "0010"=>light<="00111111"; when "0011"=>light<="00011111"; when "0100"=>light<="00001111"; when "0101"=>light<="00000111"; when "0110"=>light<="00000011"; when "0111"=>light<="00000001"; when "1000"=>light<="00000011"; when "1001"=>light<="00000111"; when "1010"=>light<="00001111"; when "1011"=>light<="00011111"; when "1100"=>light<="00111111"; when "1101"=>light<="01111111"; when "1110"=>light<="11111111"; when others=>light<="00000000";end case;elsif state=s2 then -- 第三种彩灯花样的程序if cnt3="100" thenCnt3<="000";else cnt3<= cnt3+1;end if;case cnt3 iswhen "000"=>light<="10000001"; when "001"=>light<="11000011"; when "010"=>light<="11100111"; when "011"=>light<="11111111"; when others=>light<="00000000";end case;elsif state=s3 then -- 第四种彩灯花样的程序if cnt4="100" thencnt4<="000";else cnt4<= cnt4+1;end if;case cnt4 iswhen "000"=>light<="00011000"; when "001"=>light<="00111100"; when "010"=>light<="01111110"; when "011"=>light<="11111111"; when others=>light<="00000000";end case;elsif state=s4 then --第五种彩灯花样的程序if cnt5="1111" thenCnt5<="0000";else cnt5<=cnt5+1;end if;case cnt5 iswhen "0000"=>light<="11000000"; when "0001"=>light<="01100000"; when "0010"=>light<="00110000"; when "0011"=>light<="00011000"; when "0100"=>light<="00001100"; when "0101"=>light<="00000110"; when "0110"=>light<="00000011"; when "0111"=>light<="00000110"; when "1000"=>light<="00001100"; when "1001"=>light<="00011000"; when "1010"=>light<="00110000"; when "1011"=>light<="01100000"; when "1100"=>light<="11000000"; when others=>light<="00000000";end case;elsif state=s5 then -- 第六种彩灯花样的程序if cnt6="1111" thenCnt6<="0000";else cnt6<=cnt6+1;end if;case cnt6 iswhen "0000"=>light<="00000011"; when "0001"=>light<="00000110"; when "0010"=>light<="00001100"; when "0011"=>light<="00011000"; when "0100"=>light<="00110000"; when "0101"=>light<="01100000"; when "0110"=>light<="11000000"; when "0111"=>light<="01100000"; when "1000"=>light<="00110000"; when "1001"=>light<="00011000"; when "1010"=>light<="00001100"; when "1011"=>light<="00000110"; when "1100"=>light<="00000011"; when others=>light<="00000000";end case;end if;end if;END PROCESS P1;P2:PROCESS(clk) --分频进程variable cnt:integer range 0 to 10; BEGINIF(RST='0')thencnt:=0;ELSIF(clk'EVENT AND clk='1')thenif cnt<9 thencnt:=cnt+1;clk1ms<='0';elsecnt:=0;clk1ms<='1';end if;end if;end PROCESS P2;process(rst)--循环beginif (rst='1') thenstate<=s0;elseif(clk_use'event and clk_use='1') thencase state iswhen s0 =>state<=s1;when s1=>state<=s2;when s2=>state<=s3;when s3 =>state<=s4;when s4=>state<=s5;when s5=>state<=s1;end case;end if;end if;end process;end control;本控制电路采用VHDL语言设计。