Verilog流水灯实验报告.pptx

verilog语言的FPGA变速花样流水灯设计

基于XILI NX--XSE500E型FPGA的变速流水灯以及花样流水灯的ve rilog语言设计摘要临近大四毕业,诸多工科院校电子电科通信等专业会选择用FP GA项目作为课程设计的课题,笔者同样经历了这个过程,收获颇多,在此将设计成果在此分享,以帮助大家更好掌握FP GA设计。

FPGA种类繁多,时效性非常好,设计过程中十分注重实时性,在时间点控制上非常优秀。

此次设计采用X ILINX的XSE500E型芯片的开发板,芯片采用FG320型接口,速度级别-4。

板载时钟50MHz,如需其他时钟周期,可采用IP核中的clo cking,其中的 DCM可以实现变频,引入DCM,输入频率50MHz,输出频率填入需要的频率即可,之后进行实例化。

此外,可以借助计数器进行延时减速,此次设计采用了计数器延时方法。

本次列举了四种流水灯相关设计:普通流水灯(向左和向右滚动),自动反复式流水灯(到最右端自动向左滚动,到左端自动向右滚动),花样流水灯,变速流水灯。

谢谢大家的支持!正文一,普通流水灯1,建模思想普通流水灯,可以向右滚动,到最右端返回最左端,也可以向左滚动,到最左端返回最右端。

普通流水灯模块涉及的端口有:clk,它是时钟输入,一般就是板载时钟,这里是50MHz,具体参照开发板说明。

还有复位输入r st,高电平有效。

此外就是le d端口,这个端口有8根管脚,共8位,连接8个le d灯。

采用veri log语言,端口定义格式如下:module led(inputclk,inputrst,output reg[7:0] led //此行定义说明l ed端口既是驱动管脚的,又是寄存器);采用过程建模,这里不采用行为建模和功能建模,因为这个过程就是一个大循环,规律性极强。

verilog实验报告流水灯数码管秒表交通灯

流水灯实验目的:在basys2开发板上实现LED灯的花样流水的显示,如隔位显示,依次向左移位显示,依次向右移位显示,两边同时靠中间显示。

实验仪器:FPGA开发板一块,计算机一台。

实验原理:当一个正向的电流通过LED时,LED就会发光。

当阳极的电压高于阴极的电压时,LED就会有电流通过。

当在LED上增添一个典型值为1.5V—2.0V之间的电压时,LED就会有电流通过并发光。

实验内容:顶层模块:输入信号:clk_50MHz(主时钟信号),rst(重置信号),输出信号:[7:0] led(LED灯控制信号)。

module led_top(clkin,rst,led_out);input clkin, rst;output [7:0] led_out;wire clk_1hz;divider_1hz d0(clkin, rst, clk_1hz);led l0(clk_1hz, rst, led_out);endmodule分频模块:module divider_1hz(clkin,rst,clkout);input clkin,rst;output reg clkout;reg [24:0] cnt;always@(posedge clkin, posedge rst)beginif(rst) begincnt<=0;clkout<=0; endelse if(cnt==24999999) begincnt<=0;clkout=!clkout; endelse cnt<=cnt+1;endendmodule亮灯信号模块:module led(clkin,rst,led_out);input clkin,rst;output [7:0] led_out;reg [2:0] state;always@(posedge clkin, posedge rst)if(rst) state<=0;else state<=state+1;always@(state)case(state)3'b000:ledout<=8'b0000_0001;3'b001:ledout<=8'b0000_0010;3'b010:ledout<=8'b0000_0100;3'b011:ledout<=8'b0000_1000;3'b100:ledout<=8'b0001_0000;3'b101:ledout<=8'b0010_0000;3'b110:ledout<=8'b0100_0000;3'b111:ledout<=8'b1000_0000;endcaseendmodule实验中存在的问题:1 芯片选择问题automotive spartan3EXA3S100E XA3S250E CPG132spartan3EXC3S100E XC3S250E CP1322 时序逻辑部分,阻塞赋值和非阻塞赋值混用always@(posedge clk)begina=b+c;d<=e+f;end3 UCF文件格式错误NET “CLK” LOC = “B8”;NET “a” LOC = “N11”;NET “b” LOC = “G13”;NET “c[0]”LOC =“K11;数码管实验目的:设计一个数码管动态扫描程序,实现在四位数码管上动态循环显示“1”、“2”“3”“4”;实验仪器:FPGA开发板一块,计算机一台。

FPGA入门系列实验教程——流水灯

FPGA入门系列实验教程——LED流水灯1.实验任务让实验板上的8个LED实现流水灯的功能。

通过这个实验,进一步掌握采用计数与判断的方式来实现分频的Verilog HDL的编程方法以及移位运算符的使用。

2.实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208C8增强版开发套件。

软件实验环境为Quartus II8.1开发软件。

3.实验原理流水灯,顾名思义就是让LED象水一样的点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮;然后,通过移位,在其右侧的灯,由左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

初始状态时,8个灯都不亮。

每来一个时钟脉冲CLK,计数器就加1。

每当判断出计数器中的数值达到25000000时,就会点亮一个灯,并进行移位。

FPGA输出的数据就应该首先是10000000,隔1秒钟变成11000000……一直变化到11111111,这样,依次点亮所有的灯,就形成了流水灯。

而当8个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态,即:灯都不亮。

然后,再一次流水即可。

如果是右移位,就出现向右流水的现象;反之,向左流水。

4.实验程序module ledwater(clk,led);//模块名及端口参数output[7:0]led;//输出端口定义input clk;//输入端口定义,50M时钟reg[8:0]led_out;//变量led_out定义为寄存器型reg[8:0]led_out1;//变量led_out1定义为寄存器型reg[25:0]buffer;//中间变量buffer定义为寄存器型always@(posedge clk)beginbuffer=buffer+1;if(buffer==26'd2*******)//判别buffer数值为25000000时,做输出处理beginled_out=led_out<<1;//led向左移位,空闲位自动添0补位if(led_out==9'b000000000)led_out=9'b111111111;led_out1=~led_out;//取反输出endendassign led=led_out1[7:0];endmodule5.实验步骤(1)建立新工程项目:打开Quartus II软件,进入集成开发环境,点击File→New project wizard建立一个工程项目ledwater。

verilog流水灯控制器++

verilog流水灯控制器//学习3 8译码器的原理,//拨码开关的 1 2 3作为输入//本实验采用拨码开关来作为输入,LED作为状态显示//当然如果你的学习板没有拨码开关,可以用key1 key2 key3 作为数据输入。

//视频教程适合我们21EDA电子的所有学习板module decoder_38(out,key_in);output[7:0] out; //3 8译码器输出有8钟状态,所以要8个LED灯。

input[2:0] key_in; //(1 2 3)key1 key2 key3 作为数据输入reg[7:0] out;always @(key_in)begincase(key_in)3'd0: out=8'b11111110; //LED作为状态显示,低电平有效3'd1: out=8'b11111101;3'd2: out=8'b11111011;3'd3: out=8'b11110111;3'd4: out=8'b11101111;3'd5: out=8'b11011111;3'd6: out=8'b10111111;3'd7: out=8'b01111111;endcaseendendmodule1位数码管动态显示//一位数码管试验//利用分频计数器得到数码管,效果//视频教程适合我们21EDA电子的所有学习板module SMG_LED (clk_50M,rst,led_bit,dataout);input clk_50M,rst; //系统时钟50M输入从12脚输入。

output [7:0] dataout; //我们这里用数码管,output led_bit; //一位数码管的位选择reg [7:0] dataout;reg led_bit;reg [27:0] count; //分频计数器//分频计数器always @ ( posedge clk_50M )begincount<=count+1; //计数器自加endalways @ ( posedge clk_50M or negedge rst)beginled_bit <= 'b0; //是数码管的位选择处于导通状态case ( count[27:24] )// case ( count[27:24] )这一句希望初学者看明白,// 也是分频的关键// 在数码管上面显示0到F0: dataout<=8'b11000000; //01: dataout<=8'b11111001;2: dataout<=8'b10100100;3: dataout<=8'b10110000;4: dataout<=8'b10011001;5: dataout<=8'b10010010;6: dataout<=8'b10000010;7: dataout<=8'b11111000;8: dataout<=8'b10000000;9: dataout<=8'b10010000;10:dataout<=8'b10001000;11:dataout<=8'b10000011;12:dataout<=8'b11000110;13:dataout<=8'b10100001;14:dataout<=8'b10000110;15:dataout<=8'b10001110; //fendcaseendendmodule7段数码管静态显示//本实验就是学习单个数码管的显示//视频教程适合我们21EDA电子的所有学习板module SMG_LED (clk_50M,led_bit,dataout);input clk_50M ; //系统时钟50M输入从12脚输入。

课程设计流水灯报告

大规模数字电路课程设计设计题目:流水灯设计专业:电子信息科学与技术班级:电信092学号:3学生姓名:***设计时间:2011-2012学年上学期教师评分:2011年 12 月 12日目录一、实验目的:.................................................................... 错误!未定义书签。

二、设计内容........................................................................ 错误!未定义书签。

三、实验用到的软件和器材................................................ 错误!未定义书签。

四、实验步骤........................................................................ 错误!未定义书签。

五、程序源代码.................................................................... 错误!未定义书签。

六、调试结果及分析............................................................ 错误!未定义书签。

1.在线调试:.............................................................. 错误!未定义书签。

2.管脚分配.................................................................... 错误!未定义书签。

3.分频器:.................................................................. 错误!未定义书签。

verilog程序-流水灯

/****************************************************程序功能:流水灯版本:1.1 版权:分享快乐*****************************************************/ module liu_shui_deng(input wire pin_clk_in,input wire pin_rest_n ,input wire [1:0] pin_ctrl,output reg [7:0] pin_led_out);wire clk ;reg [31: 0] counter32;always @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begincounter32 <= 32'b0;endelse begincounter32 <= counter32+1'b1;endendassign clk = counter32[3] ;reg [2:0] cur_sta,stateparameter [2:0] IDLE =3'b000;parameter [2:0] RIGHT =5'b001;parameter [2:0] LEFT =5'b010;parameter [2:0] DOUB_LEFT =5'b011;parameter [2:0] ERROR =5'b100;always @ (posedge clk or negedge pin_rest_n) beginif(pin_rest_n==1'b0) beginstate <= IDLE ;endelse begincase (state)IDLE : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginendelse beginstate <= ERROR ;endendLEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) begin state <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendRIGHT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) begin state <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendDOUB_LEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) beginendelse beginstate <= ERROR ;endendERROR : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endenddefault: state <= IDLE ;endcaseendendalways @ (posedge clk or negedge pin_rest_n) beginif (pin_rest_n == 1'b0) beginpin_led_out[7:0]<=8'b0000_0000 ;endelse begincase (state)IDLE : beginpin_led_out [7:0] <=8'b0000_0000 ;endLEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out[7:0] <= 8'b0000_0001;endelse beginpin_led_out[7:1] <= pin_led_out[6:0];pin_led_out[0] <= pin_led_out[7];endendRIGHT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out [7:0] <= 8'b0000_0001 ;endelse beginpin_led_out [6:0] <= pin_led_out [7:1] ;pin_led_out [7] <= pin_led_out [0] ;endendDOUB_LEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd2 ) beginpin_led_out [7:0] <= 8'b0000_0011 ;endelse beginpin_led_out [7:1] <= pin_led_out [6:0] ;pin_led_out [0] <= pin_led_out [7] ;endendERROR : beginpin_led_out [7:0]<=8'b1111_1111;enddefault : pin_led_out [7:0] <= 8'b0000_0000;endcaseendendendmodule。

流水灯实验报告

流水灯实验报告

今天,我们进行了一个有趣的实验 - 流水灯实验。

首先,让我们来谈一谈流水灯的原理。

简单来说,流水灯是一

组LED灯,它们像水一样从一端流向另一端,每个灯的状态依次

更改。

然后,我们开始制作流水灯。

首先,我们需要一块电路板和一

些LED灯。

我们将LED灯焊接在电路板上,并使用一些导线连接它们。

然后,在一端添加一个电缆,以便将电路板连接到电源。

接下来,我们需要使用一个可编程芯片来控制LED灯的闪烁

模式。

我们使用了Atmel AVR芯片作为我们的控制器,并编写了

一些简单的程序来控制LED灯的行为。

我们将程序上传到芯片中,然后将电路板连接到电源。

最后,我们观察了流水灯的行为。

在阳光明媚的白天,我们试

图让它在室内工作。

我们发现,在光线充足的情况下,灯的亮度

有些微弱,但在较暗的照明条件下,流水灯效果比较明显。

在实验中,我们学会了如何制作和控制流水灯。

这为我们了解电子设备的原理和工作方式提供了一个很好的机会。

我们也体会到了在实验过程中需要耐心和细心的重要性。

总的来说,这是一个乐趣和收获并存的实验。

我们期待着在将来的实验中探索更多有趣和有用的东西。

FPGA入门系列实验教程——LED流水灯

艾米电子工作室FPGA入门系列实验教程FPGA入门系列实验教程V1.0前言目前市场销售FPGA开发板的厂商很多,但大多只提供些简单的代码,没有详尽的文档和教程提供给初学者。

经验表明,很多学生在学习FPGA设计技术的过程中,虽然刚开始学习热情很高,但真正坚持下来一直到“学会”的却寥寥无几,除了学生个人毅力的因素外,另外一个更主要的原因就是所选的开发板缺少配套的说明文档和手把手系列的入门教程。

原本FPGA的学习门槛相对于单片机来说就高了不少,再加上缺少手把手系列教程资料,这就给初学者学习FPGA增添了更多的困难,很多初学者因为找不到入门的方法而渐渐失去了学习FPGA的兴趣和信心。

作者从接著到系统学习FPGA有两年多的时间了,学习FPGA的时间不长,期间因为没有专业的老师指导,自己摸索学习FPGA走了很多的弯路。

有过问题迎刃而解的快乐,也有过苦苦寻求结果和答案的痛苦历程,回想起自己学习FPGA的历程,从开始的茫然,到后来的疯狂看书,购买开发板,在开发板上练习各种FPGA实例,到最后能独立完成项目,一路走来,感受颇多。

发觉学习FPGA只要选择正确的方法是有捷径可走的,有很多人学习FPGA很长时间,因为没有找到正确的方法还是停留在入门阶段。

针对现状,作者从初学者的角度出发,结合作者学习FPGA的经验和亲身体会,遵循“宁可啰嗦一点,也不放过细节”的原则编写了详尽的实验教程作为艾米电子工作室开发套件的配套教程使用,主要面向FPGA初学者。

FPGA的学习只有通过大量的操作与实践才能很好并快速的掌握。

为此本实验教程从点亮LED 灯写起,深入浅出,以图文并茂的方式由易到难地列举了很多实例,采用手把手、Step by Step的方式让初学者以最快的方式掌握FPGA技术的开发流程以及Quartus II软件的使用,从而激起初学者学习FPGA的兴趣。

在教程中作者采用“授人以渔”的方式,努力做到不仅讲述怎样进行试验,而且分析为什么这样做,以便初学者深刻理解并快速掌握FPGA的学习方法。

流水灯实验报告

扬州大学广陵学院课程设计报告设计题目:流水灯设计姓名:z t y学号:100036137班级:微电81001时间:2013年7月4日目录一.设计任务与要求 (3)二.实验目的 (3)三.实验思路 (3)1系统逻辑设计 (3)2源程序代码 (3)⑴LED流水灯控制模块 (4)⑵分频器 (5)⑶四位选择器 (5)⑷六位计数器 (6)⑸2位计数器 (6)3实验原理调用 (7)4仿真结果与分析 (7)四.心得体会 (8)一.设计任务与要求随着大规模集成电路技术和EDA技术的迅速发展,使得数字系统的硬件设计如同软件设计那样方便快捷,而Verilog HDL 是当前应用最广泛的并成为IEEE 标准的一种硬件描述语言。

Verilog HDL是在C语言的基础上演化而来,具有结构清晰、文法简明、功能强大、高速模拟和多库支持等优点。

此次课程设计通过使用Verilog HDL硬件描述语言设计了一个程序,使得流水灯可以根据自己所期望的方式点亮,并能在、MAX+plusⅡ进行仿真测试,得出出仿真结果。

通过课程设计深入理解VHDL语言的精髓,加深对数字电路和VHDL基本单元的理解,理论联系实际,提高设计能力,提高分析、解决计算机技术实际问题的独立工作能力。

二、实验目的1、熟悉利用MAX+plusⅡ开发数字电路的基本流程和MAX+plusⅡ软件的相关操作。

2、掌握基本的设计思路、软件环境参数配置和仿真。

3、了解VerilogHDL语言设计或原理图设计方法。

4、通过本知识点的学习,了解流水灯的工作原理,掌握其逻辑功能设计方法。

三、实验思路根据时钟信号的脉冲输入,我们以改变每个LED点亮状态的保持的时间来改变LED的变换间隔时间,根据LED的循环点亮和时间间隔的改变设计成为一个直观的LED流水灯自动循环系统,由此思路我们就可以很容易的着手流水灯控制程序的设计。

1.系统逻辑设计:根据以上的设计要求,运用模块化的设计思路,我们在MAX+plusⅡ软件系统中设计了LED流水灯控制模块、分频器模块、4位选择器、6位计数器、2位计数器,并通过各个模块程序之间的端口合理连接和协调,成功设计出LED流水灯灯控制电路,得到逻辑结构原理图,即为整个流水灯控制电路的逻辑结构。

实验1_流水灯实验

实验1 流水灯实验一、实验目的1) 简单I/O 引脚的输出2) 掌握软件延时编程方法 3) 简单按键输入捕获判断 二、实验实现的功能1) 开机是点亮全部12个发光二极管,闪烁三下;2) 按下不同的按键12个发光二级管按照不同的方式显示。

具体显示规则如下:1) 1号键按下,按照顺时针循环依次点亮发光二极管; 2) 2号键按下,按照逆时针循环依次点亮发光二极管;3) 3号键按下,按照顺时针间隔1个依次点亮发光二极管; 4) 4号键按下,按照逆时针间隔1个依次点亮发光二极管; 5) 5号键按下,按照顺时针间隔2个依次点亮发光二极管; 6) 6号键按下,按照逆时针间隔2个依次点亮发光二极管;三、系统硬件设计 1、系统原理框图2、系统硬件原理图D 1D 2D 3R N 11k123456789101112242322212019181716151413D 4D 5D 6D 7D 8D 9D 10D 11D 12P 22P 21P 20P 26P 25P 24P 23P 06P 05P 04P 27P 07V C CR 21kR 31kP 36S W 1S W 2S W 3S W 4S W 5S W 6P 32P 33P 37P 34R 1710k R 1810k R 1910kV C C80C51时钟部分电源与复位部分12个发光二极管键盘系统四、系统软件设计本次实验的主要部分是:确定发光二级管点亮规律和检测按键的动作。

其中发光二级管点亮规律通过给定的数组来确定,而检测按键,采用查询方式实现,详细程序如下:#include<stc10.h>#define uint unsigned int #define uchar unsigned char bit flag1=0; uchar f1,f=0; void main() {void Delay1ms(uint ms);uchar key(uchar f);uchar led[12]={0xfe,0xfd,0xfb,0xf7,0xef,0xdf,0xbf,0x7f,0xef,0xdf,0xb f,0x7f}; //表示各发光二级管 uchar key_value[6]={0,1,2,3,4,5}; uint num[6]={0,0,0,0,0,0};char type[6]={1,-1,2,-2,3,-3}; //分别表示顺时针、逆时针、间隔一个正逆时针、间隔两个正逆时针 uchar i;P2=0xff; //关闭D1——D8 P0=P0|0xf0; //关闭D9——D12Delay1ms(100); //延时方便清晰看到LED 闪烁现象 for(i=0;i<3;i++) //亮灭3次,中间间隔若干时间 { P2=0;//点亮D1——D8U 1S T C 10F 08XP S E N29A L E 30V C C 40E A 31X 119X 218R S T 9P 0.0/A D 039P 0.1/A D 138P 0.2/A D 237P 0.3/A D 336P 0.4/A D 435P 0.5/A D 534P 0.6/A D 633P 0.7/A D 732P 1.0/T 21P 1.1/T 2E X 2P 1.2/E C I 3P 1.3/C E X 04P 1.4/C E X 15P 1.5/C E X 26P 1.6/C E X 37P 1.7/C E X 48P 2.0/A 821P 2.1/A 922P 2.2/A 1023P 2.3/A 1124P 2.4/A 1225P 2.5/A 1326P 2.6/A 1427P 2.7/A 1528P 3.0/R X D 10P 3.1/T X D 11P 3.2/IN T 012P 3.3/IN T 113P 3.4/T 014P 3.5/T 115P 3.6/W R 16P 3.7/R D17C 330pC 430p X 111.0592MX 1X 2R 151kR 2010k单片机最小系统部分C 110u FD 13C 2104V C CV C CV C CC 510u FC M A XJ1C O N 28C12345678910111213141920212223242526272815161718P 02P 01P 00P 06P 05P 04P 03P 07P 23P 22P 21P 20P 27P 26P 25P 24D 5D 6D 7D 8D 1D 2D 3D 4W 1D 9W 4W 3W 2D 12D 11D 10P 23P 22P 21P 20P 25P 24P 31P 30P 27P 26P 35P 34P 33P 32P 37P 36P 03P 02P 01P 00P 07P 06P 05P 04P 13P 12P 11P 10P 15P 14X 2X 1P 17P 16P 11P 10R S T P 15P 14P 13P 12P 17P 16P 35P 34P 33P 32H 1H 2P 37P 36L 1L 2L 3EFG D P CBADV C CJ6C O N 40A 12345678910111213141516171819202122232425262728293031323334353637383940S W 8R S TP0=P0&0x0f; //点亮D9——D12Delay1ms(500); //延时P2=0xff; //关闭D1——D8P0=P0|0xf0; //关闭D9——D12Delay1ms(500); //延时}while(1){f1=key(f); //传递键值if((f1!=f)||(flag1))//判断是否有键按下,不管两次按键的键值是否相等,只要有键按下,都从D0重新开始循环{f=f1; //交换新键值num[f]=0; //从D0开始循环flag1=0; //标志位清零}if(num[f]%12<8) //先依次亮前8个{P2=led[num[f]%12];P0=P0|0xf0; //关闭D9——D12}else //再依次亮后4个{P0|=0xf0;P0&=led[num[f]%12];P2=0xff; //关闭D1——D8}Delay1ms(100);//num[f]=num[f]+type[f]; //点亮type[f]所对应模式的下一个LEDswitch(num[f]) //保证循环连续一致{case 65535:num[f]=65531;break;case 65534:num[f]=65532;break;case 65533:num[f]=65529;break;default: break;}}}void Delay1ms(uint ms) //@11.0592MHz {uchar i,j;uint k;for(k=0;k<ms;k++){i = 11;j = 190;do{while (--j);} while (--i);}}uchar key(uchar s) //按键扫描子函数{uchar flag=s;uchar k,i,p3;flag1=0;k=0x7f; //行扫描初值for(i=0;i<2;i++) //扫描行{P3=k;Delay1ms(5);p3=P3; //判断哪一列的键按下switch(p3&0x1c){case 0x18: flag=i*3;flag1=1;break;case 0x14: flag=i*3+1;flag1=1;break;case 0x0c: flag=i*3+2;flag1=1;break;default: break;}if(flag1)break;else k=k>>1|0x80;}return flag;}五、实验过程中遇到的问题及解决方法1.由于这个实验是第一个实验因此遇到了不少的问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

initial begin clk = 0; rst_n = 0; #100 rst_n = 1; end

always #5 clk=~clk;

LSD LSD_inst( .clk(clk), .rst_n(rst_n),

学海无 涯

流水灯实验报告

实验二 流水灯

一、 实验目的

学会编写一个简单的流水灯程序并掌握分频的方法。熟悉 Modelsim 仿真软件的使用。

二、 实验要求

用 Quartus 编写流水灯程序,在 Modelsim 软件中进行仿真。

三、 实验仪器和设备

1、 硬件:计算机 2、 软件:Quartus、Modelsim、(UE)

四、 实验内容

1、 将时钟周期进行分频。 2、 编写 Verilog 程序实现 LED 等依次亮灭,用 Modelsim 进行仿真,绘制波形图。

五、 实验设计

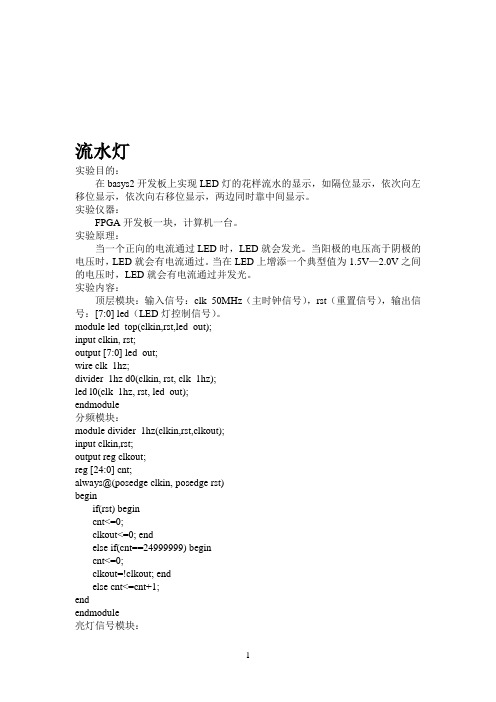

(一)分频原理 已知时钟周期f 为 50MHz,周期 T 为 1/f,即 20ns。若想得到四分频计数器,即周期为 80ns 的时钟,需要把时钟进行分频。即每四个时钟周期合并为一个周期。原理图如图 1 所示。

1

学海无 涯

clk LED

LED

FPGA

cnt

图 2 设计基本框图

(四)位拼接的用法 若输入 a=4'b1010,b=3'b101,c=4'b0101,想要使输出 d=5'b10001 用位拼接,符号“{ }”:d<={b[2:1],c[1],a[2:1]} 即把 b 的低 1~2 位 10,c 的低 1 位 0,a 的低 1~2 位 01 拼接起来,得到 10 0 01。 流水灯

always@(posedge clk_4 or negedge clk_4) if(rst_n==0)

led

<=

4'b0001;

else

led

<=

{led[2:0],led[3]};//位拼接

endmodule 2、 测试文件 `timescale 1ns/1ns module LSD(); reg clk;

if(rst_n==0)

clk_4 <=

0;

else if(cnt==24_999_999)

clk_4 <=

1;

else if(cnt==49_999_999)

clk_4 <=

0;

else clk_4 =

clk_4;

//异步复位 //复位为 0.clk_4 为 0 //当计数器为 24999999 时,时钟跳变为 1 //当计数器为 49999999 时,时钟跳变为 0

图 4 流水灯仿真结果

//模块名与文件名一致。定义端口列表, //输入线型

output reg );

clk_4

//输出定义为寄存器型

reg[3:0] cnt;

//中括号定义位宽,定义中间变量 cnt

always@(posedge clk)

if(rst_n==0)

cnt

<=

else if(cnt==3)

cnt

<=

else

cnt

<=

0; 0; cnt+1;

//复位为 0,计数器也为 0 //当计数器=3 时清零(可用else if)

//计数器自加 1

always@(posedge clk)

if(rst_n==0)

clk_4 <=

0;

else if(cnt==1)

//复位为 0.clk_4 为 0

3

clk_4 <=

4

学海无 涯

cnt

<=

0;

else if(cnt==49_999_999)

cnt

<=

0;

else

cnt

<=ຫໍສະໝຸດ cnt+1;//复位为 0,计数器也为 0 //当计数器=49999999 时清零(可用 else if)

//计数器自加 1

always@(posedge clk or negedge clk)

1;

else if(cnt==3)

clk_4 <=

0;

endmodule 2、测试文件

`timescale 1ns/1ns

module tb_div_clk();

reg

clk;

reg

rst_n;

wire clk_4;

initial begin clk rst_n #100 rst_n end

= 0; = 0;

= 1;

always #5 clk=~clk;

div_clk div_clk_inst( .clk(clk), .rst_n(rst_n),

.clk_4(clk_4) );

endmodule (二) 流水灯

1、 程序文件

module LSD(

input

wire

input

wire

clk, rst_n,

output reg[3:0] led );

reg[25:0] cnt;

reg

clk_4;

always@(posedge clk) if(rst_n==0)

学海无 涯

//当计数器为 1 时,时钟跳变为 1 //当计数器为 3 时,时钟跳变为 0

//模块名与文件名一致。定义端口列表, //输入线型 //中括号定义位宽,定义中间变量 cnt

(二)流水灯 1、编写分频程序。

图 3 分频仿真结果 2

学海无涯

3、 编写测试程序。 3、进行仿真,为了节约时间和方便观察波形,将计数器值分别改为 24、49 跳转。波 形如图 4 所示。

七、 实验参考程序

(一) 时钟分频 1、程序文件 module div_clk( input wire clk, input wire rst_n,

clk rst_n clk_4

图 1 四分频原理图

(二)流水灯设计思路 1、实现 4 盏 LED 灯依次隔 1s 亮灭,即周期为 1s; 2、计算出频率f 为 1/T=1Hz; 3、设置计数器cnt,当检测到 clk 上升沿时开始计数,当 cnt 计数到 24_999_999 时, clk_4 跳变为 1,LED 灯亮起,当 cnt 计数 49_999_999 时,clk_4 置 0,LED 灯熄灭。 4、给 LED 赋初值 4’b0001,第一盏灯亮。 5、利用位拼接,实现循环。 (三)设计框图

4'b0001 4'b0010 4'b0100 4'b1000 相当于把低三位左移,并最高位放在最低位。 用位拼接可写为:

led<={led[2:0], led[3]}; 低三位 最高位

六、 实验方法和步骤

(一)时钟分频 1、 编写分频程序。 2、 编写测试程序。 3、 进行仿真,波形如图 3 所示。