基于FPGA的等精度频率计

基于FPGA的等精度数字频率计设计(修订版)

基于FPGA的等精度数字频率计设计微电子学与固体电子学张嘉伟113114312目录摘要 (3)第一章课题背景 (4)第二章方案设计及原理 (4)1 多周期同步测频率测量原理 (4)2 设计实现 (6)2.1 FPGA程序设计 (6)2.2 DSP程序设计 (7)第三章主要模块的Verilog程序 (8)1 计数器 (8)2 除法器 (8)3 分频器 (11)4 BCD模块 (11)第四章仿真结果 (12)第五章设计总结 (13)参考文献 (13)摘要本文主要论述了利用FPGA进行测量频率计数,FPGA实施控制实现多功能频率计的设计过程。

该频率计利用等精度的设计方法,克服了基于传统测频原理的频率计的测量精度随被测信号频率的下降而降低的缺点。

等精度的测量方法不但具有较高的测量精度,而且在整个频率区域包成恒定的测试精度。

根据多周期同步测频率法的原则,选取了多周期同步测频法作为数字频率计的测量算法,提出了基于FPGA的数字频率计设计方案。

给出了该设计方案的实际测量效果,证明该设计方案切实可行,能达到较高的频率测量精度。

关键词:FPGA;等精度;频率计第一章课题背景随着大规模集成电路技术的发展及电子产品市场运作节奏的进一步加快,涉及诸如计算机应用、通信、智能仪表、医用设备、军事、民用电器等领域的现代电子设计技术已迈入一个全新的阶段。

专家预言,未来的电子技术时代将是EDA 的时代,PLD作为EDA技术的一项重要技术,是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。

在电子测量技术中,频率测量是最基本的测量之一。

工程中很多测量,如用振弦式测量力、时间测量、速度测量、速度控制等,都设计到频率测量,或可归结为频率测量。

而常用的直接测量方法在使用中有较大的局限性,其测量精度随着被测信号频率的下降而降低,并且对被测信号的计数要产生±1个数字误差。

采用等精度频率测量方法具有测量精度保持恒定,不随所测信号的变化而变化;结合FPGA,具有集成度高、告诉和高可靠性的特点,是频率的测频范围可达到0.1Hz-50MHz,测频全域相对误差恒为百万分之一。

基于FPGA的等精度频率计设计

基于FPGA的等精度频率计设计摘要频率计是实验室和科研、生产中最常用的测量仪器之一。

本文介绍了一种基于FPGA 芯片设计的等精度频率计。

对传统的等精度测量方法进行了改进,采用SOPC设计技术和基于NIOS II嵌入式软核处理器的系统设计方案,通过在FPGA芯片上配置NIOS II 软核处理器进行数据运算处理,利用液晶显示器对测量的频率进行实时显示,可读性好。

整个系统在一片FPGA芯片上实现,系统测量精度高,实时性好,具有灵活的现场可更改性。

本频率测量仪是以Altera公司生产的CycloneII系列EP2C35F672C6器件为核心实现高精度计数功能。

整个电路采用模块化设计,调试制作方便。

经过仿真并下载验证,能够实现等精度测频功能,频率测量范围为1HZ--200MHZ。

关键词:等精度,频率计,FPGA,SOPC,NiosIIDesign of Equal Precision Frequency MeterBased on FPGAABSTRACTFrequency meter is one of the most commonly used measuring instruments which can be used in laboratory, scientific research and production . An equal precision frequency meter designed with FPGA is introduced in this article. It adopts Very-High-Speed Integrated Circuit HardwareDescription Language to implement function module in frequency meter base on traditional frequency measurement. SOPC designing technique and system designing plan based on Nios II soft core CPU are used in the design. It also adopts Niosll soft core CPU as data processing unit, uses LCD 1602 equipment to display frequency in real- time. The whole system is in the realization of a FPGA chip. So it has a high- precision measurement, real- time and flexible change of scene.The frequency meter is based on CycloneII EP2C35F672C6 Altera device as the core to achieve high-precision counting. Because of the modular design of this circuit, it is facilitate to debug. After the simulation, and downloads the confirmation, can realize equal-precision frequency measurement function. Frequency measurement scope is 1--200MHZ.KEY WORDS:equal precision measurement, frequency meter, FPGA, SOPC, NiosII目录摘要 (I)ABSTRACT (II)1 绪论 (1)1.1 课题提出的背景 (1)1.2 课题选择意义 (1)2 EDA及其开发平台简介 (3)2.1 EDA的具体开发流程 (3)2.1.1设计输入 (3)2.1.2综合 (3)2.1.3 适配 (4)2.1.4 仿真 (4)2.1.5 编程下载和硬件测试 (4)2.2简介NIOS II IDE (4)2.2.1工程管理器 (5)2.2.2 编辑器和编译器 (6)2.2.3调试器 (6)2.2.4闪存编程器 (7)3 课题方案选择 (8)3.1 频率测量方案选择 (8)3.1.1 直接测频法 (8)3.1.2 间接测频法 (8)3.1.3 等精度测频 (9)3.2 基于单片机的测频方案 (10)3.3 基于FPGA的测频方案 (11)4 基于FPGA等精度频率计的单元模块设计 (13)4.1 放大整形模块设计 (13)4.2 标准信号产生模块设计 (14)4.3 FPGA芯片模块设计 (14)4.3.1 D型触发器的设计 (15)4.3.2 计数器的设计 (16)4.3.3 锁存器的设计 (19)4.3.4 NIOS II 软核CPU的设计 (20)IV4.4 LCD液晶显示模块 (23)5 系统综合及其测试 (24)5.1 放大整形模块 (24)5.2等精度计数模块 (24)5.3 整体系统 (25)5.4 软件编写与测试 (27)5.5 系统的扩展 (33)5.5.1 分频器设计 (33)5.5.2 选择器设计 (35)6 总结 (38)致谢 (39)参考文献 (40)基于FPGA的等精度频率计设计 11 绪论1.1 课题提出的背景现代数字系统的设计离不开各种先进的仪器,比如数字示波器、逻辑分析仪、频谱分析仪、信号发生器、数字频率计等。

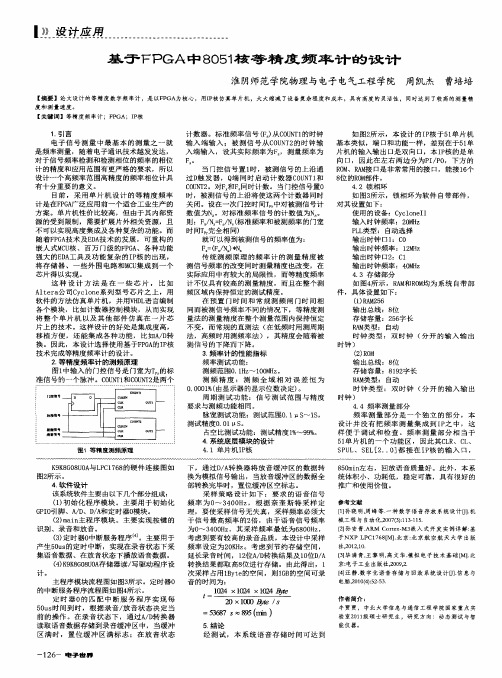

基于FPGA中8051核等精度频率计的设计

片 上 的 技 术 。 这 样 设 计 的 好 处 是 集 成 度 高 , 不变 ,而常规 的直 测法 (在低频 时用测周期

RAM类 型 : 自动

移 植 方 便 , 还 能 集 成 各 种 功 能 , 比 如A/D转 法 ,高频时用测频 率法 ),其精度 会随着被

时 钟 类 型 : 双 时 钟 (分 开 的 输 入 输 出

如 图 3所 示 , 锁 相 环 为 软 件 自带 部 件 ,

计是在FPGA广泛应用 前一个适合 工业 生产 的 关闭 。设在一次 门控时间T 中对被测信 号计 对 其 设 置 如 下 :

方案 。单片机性价 比较高 ,但 由于其 内部资 数值为N 。对标准 频率信 号 的计数值 为N 。

1.引言

计数 器 。标 准频率信 号 (F )从COUNT1的时钟

如 图2所示 ,本设计 的IP核 于51单片机

电 子 信 号 测 量 中 最 基 本 的 测 量 之 一 就 输 入端 输入 ;被测 信 号从 COUNT2的时 钟输 基 本类似 ,端 口和功能一样 ,差别在于51单

是频率测量 ,随着 电子通 讯技术越发发 达, 入端 输入 ,设其实 际频 率为F ,测量 频率为 片机的输入输 出 口是双 向口,本 IP核 的是单

(1)RAM256

各个 模块 ,比如计数器控 制模块 ,从而 实现 同而 被测信号频率 不同的情况下 ,等精度测

输 出总 线 :8位

将 整 个 单 片 机 以 及 其 他 部 件 仿 真 在 一 片 芯 量 法 的 测 量 精 度 在 整 个 测 量 范 围 内 保 持 恒 定

存 储 容 量 :256字 长

使 用 的 设 备 :CycloneII

基于FPGA的等精度数字频率计总结

作品总结智冰冰前几天做了数字频率计,虽然做的不是太好吧,但是还算是做出来了,我在这里就对大家分享一下我的制作过程,希望想做频率计的朋友能够少走一些弯路,如果有不好的地方请大家提出来,如果有更好的方法也可以和我交流交流。

拿到这个题目我首先看到题目要求频率计要能测频率、测周期、测占空比,所以我们要准备的东西就要有FPGA板,51开发板(主要利用数码管模块)、直流稳压电源、数字信号发生器。

准备好这些东西之后就要考虑作品方案问题了。

确立作品方案是整个作品中比较重要的一部分,如果作品方案不合理,就不会做出来比较好的作品。

在确立数字频率计设计方案的时候,首先就要确定用什么方法实现测频率、测周期、测占空比,查找了一些资料,大概知道了一下三种方法:(1)测频率法:测频率法是用脉冲信号产生一个固定的闸门时间t,在固定的闸门时间t内对被测信号进行计数,然后运算求出被测信号频率、周期,但是在闸门时间t内不能保证被测信号计数为整数个,这就会让被测信号产生±1的误差,所以当被测信号频率高时测量比较准确,但是测低频时误差就比较大了。

(2)测周期法:测频率法是用被测信号作为门控信号,在闸门时间t内对脉冲信号进行计数,然后运算求出被测信号频率、周期,但是同样的在闸门时间t内不能保证脉冲信号计数为整数个,这就会让脉冲信号产生±1的误差,所以当被测信号频率低时,相对来说比较准确,但对于高频来说误差就大了。

(3)等精度法:等精度测量是用脉冲信号产生一个预置闸门,然后在预置闸门时间内通过被测信号上升沿产生一个实际闸门,这样实际闸门刚好是被测信号的整数倍。

在计数允许时间内,同时对脉冲信号和被测信号进行计数,再通过数学公式推导得到被测信号的频率。

由于门控信号是被测信号的整数倍,就消除了对被测信号产生的±l周期误差,但是会产生对脉冲信号±1周期的误差。

但是相对测频率法来说误差相对较小。

确立好自己的设计方案后,就要设计自己的程序了。

基于FPGA的等精度频率计设计

设 计 和 编 程 变 得更 加 适 应 现 代 社 会 技 术 发 展 、更 加 快 速精 确 。

F P G A( 现场 可 编程 门 阵列 ) , 这 种可 编 程逻 辑 器件 是 在较 早 期 出 现 的逻 辑 器 件 的基础 上 逐 步 转 变 而来 的 , 其是 为 专 用集成 电路 范 围 中 的一 类部 分 设计 电路 而 出现 的 , 既 处理 了设 计 电路 的缺 点 , 也 战 胜 了早 期器 件 中的 门单 元 电路 数 量缺 少 的 毛病 。 设计 人 员能够 依 照各种 各样 的配置 模 式 , 选 择 使用 不 同 的编程 方 式 ,

2 0 1 3 年第2 4 期总第 1 4 4 期

S_率计设 计

高 锐 1 3 0 0 3 3 ) ( 长 春职业技 术 学 院 。 吉 林 长春 摘 要 本 文使 用 自上 而下 的 E D A 技 术设 计 方法 , 对 频 率计 的 总体设 计进 行 了功 能模块 和子 模 块划 分 。说 明了各功 能

1 等 精 度测 量方法 工 作原 理

频 率 是 电信 号 最常 用 特 性 , 它的 测 量 对于 电子 电路 来 说 也

是 最 必 需和 最 重要 的 。 因为 频 率 信号 本 身 的特 点决 定 了其 测量 结 果 大 都能 够 取到 较 高 的精 度 , 因而 频 率 信 号 的测 量方 法 的 实 现 在 实 践 中变 得越 来 越 重要 。在 实 际工 程 项 目里 , 也 需要 把相 应 的 物 理参 数和 相 关 参 数都 替变 为频 率 才 能 较好 的完成 测 量 工

(完整版)基于FPGA的等精度频率计的设计与实现毕业论文

第一章课题研究概述1.1课题研究的目的和意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

目前常用的测频方案有三种:方案一:完全按定义式F=N/T进行测量。

被测信号Fx经放大整形形成时标ГX,晶振经分频形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1/ГX=N/TR。

此方案为传统的测频方案,其测量精度将随被测信号频率的下降而降低。

方案二:对被信号的周期进行测量,再利用F=1/T(频率=1/周期)可得频率。

测周期时,晶振FR经分频形成时标ГX,被测信号经放在整形形成时基TX控制闸门。

闸门输出的计数脉冲N=ГX/TR,则TX=NГX。

但当被测信号的周期较短时,会使精度大大下降。

方案三:等精度测频,按定义式F=N/T进行测量,但闸门时间随被测信号的频率变化而变化。

如图1所示,被测信号Fx经放大整形形成时标ГX,将时标ГX经编程处理后形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1/ГX=N/TR。

此方案闸门时间随被测信号的频率变化而变化,其测量精度将不会随着被测信号频率的下降而降。

本次实验设计中采用的是第三种测频方案。

等精度频率计是数字电路中的一个典型应用,其总体设计方案有两种:方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但由于使用的器件较多,连线复杂,体积大,功耗大,焊点和线路较多将使成品稳定度与精确度大打折扣,而且会产生比较大的延时,造成测量误差、可靠性差。

方案二:采用可编程逻辑器件(CPLD)制作。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

基于FPGA的等精度频率计的设计与仿真

目录摘要 (I)ABSTRACT ...................................................... I I 引言.. (1)1概述 (2)1.1频率计在国内外的发展状况 (2)1.2频率计的发展趋势 (2)1.3本课题研究的目的、意义和要求 (3)1.4电子设计自动化(EDA)技术概述 (4)1.4.1EDA技术及其发展 (4)1.4.2Quartus II软件介绍 (5)1.4.3EDA工具使用流程 (7)1.5可编程逻辑门阵列简介 (9)1.5.1可编程逻辑器件的发展历程 (9)1.5.2FPGA的结构与工作原理 (10)2等精度频率计的设计 (11)2.1设计要求 (11)2.2设计方案的选择 (11)2.2.1系统方案的选择 (11)2.2.2测频方法的选择 (12)2.2.3等精度的测频原理 (13)3基于FPGA的等精度频率计的设计 (15)3.1系统方案 (15)3.2误差分析 (15)3.3系统原理框图 (16)3.4系统整体框图 (18)4等精度测频法各个模块的介绍 (19)4.1信号源模块 (19)4.2分频模块 (19)4.3计算模块 (19)4.3.1D触发器的设计 (20)4.3.2计数器的设计 (20)4.4显示模块 (21)4.5各模块方框图 (21)5整体步骤 (23)5.1创建工程 (23)5.2引脚锁定 (23)5.3硬件测试与仿真 (24)5.4等精度测量与周期法测量图片验证 (24)5.5等精度测量与周期法测量结果对比 (28)6结束语 (29)致谢 (30)参考文献 (31)附录源程序 (32)基于FPGA的等精度频率计的设计与仿真摘要本文主要讲述了等精度频率计的FPGA设计方法,它主要是针对传统频率计不能满足等精度测量要求的缺点而提出的。

实验结果表明,该系统可以实现在整个频段内的测量精度保持一致,测量误差小,达到了等精度的测量要求。

基于FPGA实现等精度数字频率计设计

摘要本文基于FPGA的等精度测频原理,给出了通过FPGA来设计等精度频率计的具体方法。

并在此基础上增加了测量周期、脉冲宽度、占空比的功能。

设计中,以Alteta FPGA 系列CycloneⅡ EP2C5T144C8器件为核心;运用VHDL语言设计功能模块;运用SOPC设计技术来配置NiosII系统,进行信号的控制、数据读取、运算处理、液晶的显示。

关键词:等精度频率计;FPGA;NiosⅡ;AbstractThe principle of cymometer of equal precision based on FPGA is introduced in this paper. The specific methods are given to design the system through the FPGA. It is also adds much more function such as cycle, pulse width, duty cycle measurement. It uses Altera Corporation CycloneII series ship--EP2C5T144C8 as a core; adopts Verilog Hardware Description Language to implement function module; adopts the SOPC technique to configuration NiosII system. the NiosⅡsystem is used for signal controlling, data processing , calculation, and display。

Key Word:equal precision frequency meter; FPGA; NiosⅡ;目录摘要 (I)Abstract (I)1 引言 (1)2 系统设计 (1)2.1设计要求 (1)2.2方案论证与比较 (2)2.3 设计思路 (2)2.4 系统的总体设计 (3)3 模块电路的设计 (4)3.1 CycloneⅡ SOPC Board 简介 (4)3.2 频率、周期测试模块 (5)3.2.1 等精度测频法原理 (5)3.2.2 等精度测周期法原理 (6)3.2.3 实现方法 (6)3.2.4 仿真 (7)3.3 脉宽、占空比测试模块 (8)3.3.1 脉宽测量原理 (8)3.3.2 占空比测量原理 (8)3.3.3 实现方法 (8)3.3.4 仿真 (8)3.4 液晶显示 (9)3.4.1 LCM128645ZK液晶概述 (9)3.4.2 液晶的控制 (9)4 NIOSⅡ系统的设计 (11)4.1 NIOSⅡ系统的分析 (11)4.2 基于NIOSⅡ IDE的软件设计 (12)4.2.1 主要的库函数说明 (12)4.2.2 系统流程图 (12)5 系统测试 (14)5.1 测试仪器 (14)5.2数据记录与分析 (14)5.2.1 频率、周期测试 (14)5.2.2 脉宽测试 (16)5.2.3 占空比测试 (17)5.3 设计不足 (17)6 结束语 (18)致谢 (19)参考文献 (20)附录 (21)1 引言在电子测量技术中,频率测量是最基本的测量之一。

基于FPGA的等精度数字频率计设计

摘要频率是常用的物理量,工程中很多物理量的测量,如时间测量、速度控制等,都可转化为频率测量。

此外,还经常遇到以频率为参数的测量信号,例如流量、转速等。

所以频率测量方法的研究越来越受到重视。

基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性, 而等精度频率计不但具有较高的测量精度, 而且在整个频率区域能保持恒定的测试精度。

本课题设计的等精度数字频率计是采用当今电子设计领域流行的EDA技术,以FPGA为核心,配合STC89C51单片机。

同时,采用等精度测频原理,实现了0.01Hz--50MHz信号频率的等精度频率测量。

此外,该系统还实现测量周期、脉宽、占空比等功能。

设计中用一块FPGA芯片EP2C5Q208C8完成各种时序逻辑控制、计数功能。

在Ouartus II平台上,用VHDL语言编程完成FPGA的软件设计、编译、调试、仿真和下载。

用STC89C51单片机作为系统的主控部件,实现整个电路的测试信号控制、数据运算处理、键盘扫描和控制数码管的显示输出。

系统将单片机STC89C51的控制灵活性及FPGA芯片的现场可编程性相结合,不但大大缩短了开发研制周期,而且使本系统具有结构紧凑、体积小,可靠性高,测频范围宽、精度高等优点。

关键词:频率计;EDA技术;FPGA;单片机AbstractFrequency is commonly used physical quantity, lots of measurement of physical quantity in the project, such as the measurement of time, the control of velocity, can be changed into the measurement of frequency. Besides, the measured signal with a frequency parameter, such as the rate of flow, the rotational speed, is often encountered. So the research of the method of measuring frequency has become more and more significant in the real application.According to the principles of traditional frequency measurement , the measurement accuracy of frequency meter will decrease with the signal frequency decrease .but it has more limitations in the real application, equal precision frequency meter not only has high accuracy, but also maintains constant test accuracy in the whole frequency region .With the help of FPGA and cooperating with the single chip computer STC89C51,The digital frequency design in our program has realized the precision measurement of 0.01Hz-50MHz signal frequency by adopting the current EDA technique prevailing in the electronic designs and using the principle of multi-period synchrony frequency measurement. Besides, the system can complete the cycle, pulse width, duty cycle measurement function .In this design, using an FPGA chip EP2C5Q208C8 completes a variety of temporal logic control and counting function. In the platform of Ouartus II, using VHDL language completes FPGA software design, compiler, debugging, simulation, and download. By use of the STC89C51 single chip computer as the main controlling parts, the control of the tested signal, the scan of keyboard and the output display of LED can be realized. The system combines the control flexibility of STC89C51 with programmable performance of FPGA, consequently,not only can it shorten the period of the development and research, but also it has the advantages of compact structure, little volume, high reliability, wide scope and high precision. Keywords:Frequency meter,EDA technique,FPGA, Single chip computer目录摘要 (I)Abstract (II)目录 (III)1 绪论 (1)1.1 本课题的研究背景及意义 (1)1.2 本课题的主要内容 (2)2 系统设计的相关理论 (3)2.1 频率测量方法的研究 (3)2.1.1 常用测频方案 (3)2.1.2 等精度测频原理 (3)2.1.3 等精度测频误差分析 (5)2.2 单片机模块理论及知识 (5)2.2.1 MCS-51单片机结构简介 (5)2.2.2 Keil μvision 3软件概述 (7)2.2.3 Proteus软件概述 (7)2.3 FPGA模块理论及知识 (8)2.3.1 FPGA原理概述 (8)2.3.2 Quartus II 软件概述 (9)2.3.3 VHDL语言简介及开发优点 (11)3 系统硬件电路设计 (13)3.1 系统顶层电路组成 (13)3.2 被测信号放大整形电路设计 (13)3.3 单片机模块设计 (14)3.3.1 单片机最小系统 (14)3.3.2 键盘接口电路 (15)3.3.3 LED数码管显示电路 (17)3.4 FPGA模块电路设计 (18)3.4.1 基本单元电路 (19)3.4.2 测量与自检选择电路 (23)3.4.3 脉宽控制电路 (24)3.4.4 测频与测周期电路 (25)3.5 单片机与FPGA的相互控制电路 (26)4 系统软件设计 (28)4.1 单片机主程序设计 (28)4.2 复位自检程序设计 (28)4.3 键盘程序设计 (29)4.4 测频子程序设计 (30)4.5 测周期子程序设计 (31)4.6 测脉宽子程序设计 (32)4.7 测占空比子程序设计 (32)4.8 LED数码管显示子程序设计 (33)5 系统性能分析 (34)5.1 测量范围分析 (34)5.2 测量精度分析 (34)5.3 被测信号幅值分析 (34)结论 (35)致谢 (36)参考文献 (37)附录一FPGA程序 (38)附录二单片机程序 (41)1绪论1.1本课题的研究背景及意义EDA(Electronic Design Automation——电子设计自动化)代表了当今电子设计技术的最新发展方向,通过VHDL(V ery High Speed Integrated Circuit Hardware Description Language)硬件描述语言的设计,用FPGA(Field-Programmable Gate Array——现场可编程门阵列)来实现小型电子设备的设计,是开发仪器仪表的主流。

基于FPGA数字等精度频率计的设计

设计研发2020.07基于FPGA数字等精度频率计的设计张洋(重庆幼儿师范高等专科学校,重庆,404047)摘要:等精度频率计是在数字逻辑电路中的典型应用,它也是现代微电子领域中不可缺少的测量仪器。

本设计就是根据等精度的测频基本原理,提出的整体设计方案。

以FPGA芯片为核心电路,釆用VHDL语言编写子电路程序组建出顶层原理图,通过运用Quartus II软件,进行编译仿真,最后下载到实验电路板。

依照实际中频率计的使用情况,设计了八位数码管显示的等精度频率计,能够提高频率测量的精准度,减少测量误差。

关键词:等精度;现场可编程门系列(FPGA);VHDL编程;频率计Design of digital equal precision frequency meter based on FPGAZhang Yang(Chongqing Preschool education College,Chongqing,404047)Abstract:Equal-precision frequency meter is a typical application in digital logic circuit,it is also an indispensable measuring instniment in modern microelectronics field.This design is basedon the basic principle of frequency measurement of equal precision,the overall design ing FPGA chip as the core circuit using nguage program set up a top-level sub-circuit schematics, through the use of Quartus II software,compiled Simulation,and finally downloaded to the breadboard.In accordance with the actual use of the frequency meter designed eight digital display precision frequency meter.Frequency measurement accuracy can be improved,to reduce measuremerrt errors. Keywords:precision;Field Programmable Gate series(FPGA);VHDL programming;frequency meter1概述数字等精度频率计是现代微电子领域中必不可少的测量仪器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

光电与通信工程学院课程设计报告书课设名称:等精度频率计年级专业及班级:姓名:学号:一、课程设计目的1、进一步熟悉 Quartus Ⅱ的软件使用方法,熟悉 keil 软件使用;2、熟悉单片机与可编程逻辑器件的开发流程及硬件测试方法;3、掌握等精度频率计设计的基本原理。

4、掌握独立系统设计及调试方法,提高系统设计能力。

实验设备EDA最小系统板一块(康芯)、PC机一台、示波器一台、信号发生器一台、万用表一个。

二、设计任务利用单片机与FPGA设计一款等精度频率计,待测脉冲的检测及计数部分由FPGA实现,FPGA的计数结果送由单片机进行计算,并将最终频率结果显示在数码管上。

要求该频率计具有较高的测量精度,且在整个频率区域能保持恒定的测试精度,具体指标如下:a)具有频率测试功能:测频范围 100Hz~5MHz。

测频精度:相对误差恒为基准频率的万分之一。

b)具有脉宽测试功能:测试范围 10μs~1s,测试精度:0.1μs。

c)具有占空比测试功能:测试精度1%~99%。

d)具有相位测试功能。

(注:任务a 为基本要求,任务 b、c、d 为提高要求)三、基本原理基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测试精度。

3.1 等精度测频原理等精度频率计主控结构如图 1 所示预置门控信号 CL 选择为 0.1~1s 之间(通过测试实验得出结论:CL 在这个范围内选择时间宽度对测频精度几乎没有影响)。

BZH 和 TF 分别是 2 个高速计数器,BZH 对标准频率信号(频率为 Fs)进行计数,设计数结果为 Ns;TF 对被测信号(频率为Fx)进行计数,计数结果为 Nx,则有MUX64-8 模块并不是必须的,可根据实际设计进行取舍。

分析测频计测控时序,着重分析 START的作用,完成等精度频率计设计。

3.2 FPGA 模块FPGA模块所要完成的功能如图 1 所示,由于单片机的速度慢,不能直接测量高频信号,所以使用高速 FPGA 为测频核心。

100MHZ 的标准频率信号由FPGA 内部的 PLL 倍频实现,待测信号 TCLK 为方波,由信号发生器给出待测方波信号(注意:该方波信号带有直流偏置,没有负电压,幅值3.3V)。

预制门控信号 CL 由单片机发出,BRNA 和 ENA 分别是 BZH 与 TF 两个计数器的计数允许信号端。

FPGA 将允许计数时间内的 BZH、TF 的运行结果送入单片机进行最后的计算。

顶层文件如下:2以下是把20M 5倍频的设置,利用FPGA内部的PLL。

电路需要100M标准频率信号,FPGA提供20M的频率,所以需要建立PLL模块,使之五杯频,得到所需的100M信号。

功能仿真设置:下图是波形仿真的结果:3.3 单片机模块单片机模块完成对整个测频系统的控制,包括对FPGA的控制以及数码管的显示控制。

测频允许信号由单片机发出,并且单片机的P0 口负责循环读取FPGA 发送过来的测频结果数据(BZH、TF两个计数器的计数结果,每次传送8位数据),P2负责发送控制信号,单片机可以通过结束信号了解测频记数是否结束,以确定何时开始读取数据。

附上康芯原理图截图:四、实验现象占空比五、心得体会这周课程设计的题目是等精度频率计的设计,由于书本上有一段程序,所以一开始只是将书上的程序和显示波形研究了一下。

当到课程设计的时候,将书上程序敲入并实现效果后有点茫然的感觉。

于是,我又仔仔细细地分析了一遍设计原理,从新改变了输入的代码,加上自己的思路,并能自己添加预置控制信息CL模块。

原本我还想将测试频率显示在数码管上,但是最终没能实现,这应该是我的一个遗憾吧。

设计中,我感受到了硬件描述语言的强大,我可以几乎不用考虑硬件条件,将代码导入就可实现功能。

不要总想着去依靠书本上的原题或者是他人,自己思考的做出来的,才算是自己真正收获的。

本次实验最大的收获莫过于,独立系统的去完成一项任务。

在其中我查阅了大量的资料,尤其是数字电路、quartersⅡ软件使用说明、EDA设计等方面的资料。

通过本次学习使我对时序电路有了更深的理解,具体体现在复位、计数、锁存多环节的控制上。

同时,在这次实验中,我第一次联合单片机和EDA一起完成一个项目。

EDA充分的发挥其高频工作的特点,使得频率测量的上限很高。

单片机则在整个系统中充当控制及数据处理的作用设计的优点及缺点本频率计最大优点在于它的高精度。

信号频率的测量,不受闸门信号精度的影响。

在被测信号送入计数器之前,先通过D触发器,使闸门信号和被测信号同步,有效地避免了±1误差。

不仅如此,本频率计对100HZ至5MHZ的全域相对误差均小于百万之一。

当然,本频率计也存在缺点。

在频率计的设计中,乘法器为32位,除法器采用64位,资源占用率太大。

单片机处理32位数据的方式有待改进,要是它变得更优化六、系统设计步骤及程序,结果FPGA:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY EQUALFRECOUNT ISPORT(BCLK,TCLK:IN STD_LOGIC;DATA_OUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);EN:IN STD_LOGIC;ADDRESS:IN STD_LOGIC_VECTOR(3 DOWNTO 0));END EQUALFRECOUNT;ARCHITECTURE ARCH OF EQUALFRECOUNT ISSIGNAL EN2,WIDE_TEST:STD_LOGIC;SIGNAL WIDE_COUNT,B_COUNT,T_COUNT:STD_LOGIC_VECTOR(31 DOWNTO 0);SIGNAL SAVE_WIDE,SAVE_B,SAVE_T:STD_LOGIC_VECTOR(31 DOWNTO 0); BEGINPROCESS(EN,TCLK)BEGINIF RISING_EDGE(TCLK) THENEN2<=EN;ELSE NULL;END IF;END PROCESS;PROCESS(EN2,TCLK,BCLK)BEGINIF EN2='1' THENIF RISING_EDGE(TCLK) THENIF T_COUNT=X"FFFF_FFFF" THENT_COUNT<=(OTHERS=>'1');ELSE T_COUNT<=T_COUNT+1;SAVE_T<=T_COUNT+1;--SAVE T_COUNTEND IF;ELSE NULL;END IF;IF FALLING_EDGE(TCLK) THENIF WIDE_TEST='0' THENWIDE_COUNT<=B_COUNT;WIDE_TEST<='1';ELSE SAVE_WIDE<=WIDE_COUNT;--SAVE WIDE_COUNTEND IF;END IF;IF RISING_EDGE(BCLK) THENIF B_COUNT=X"FFFF_FFFF" THENB_COUNT<=(OTHERS=>'1');ELSE B_COUNT<=B_COUNT+1;SAVE_B<=B_COUNT+1;--SAVE B_COUNT IN SAVE_BEND IF;ELSE NULL;END IF;ELSE--WHEN ENA=0,WE OUTPUT THE DATA AND RESET THE COUNTER.WIDE_COUNT<=(OTHERS=>'0');B_COUNT<=(OTHERS=>'0');T_COUNT<=(OTHERS=>'0');WIDE_TEST<='0';END IF;END PROCESS;PROCESS(ADDRESS,EN2,SAVE_T,SAVE_B,SAVE_WIDE,BCLK)BEGINIF RISING_EDGE(BCLK) THENIF EN2='0' THEN--USE SOME CONSTANTS TO TESTCASE ADDRESS ISWHEN X"0"=>DATA_OUT<=SAVE_T(7 DOWNTO 0);WHEN X"1"=>DATA_OUT<=SAVE_T(15 DOWNTO 8);WHEN X"2"=>DATA_OUT<=SAVE_T(23 DOWNTO 16);WHEN X"3"=>DATA_OUT<=SAVE_T(31 DOWNTO 24);WHEN X"4"=>DATA_OUT<=SAVE_B(7 DOWNTO 0);WHEN X"5"=>DATA_OUT<=SAVE_B(15 DOWNTO 8);WHEN X"6"=>DATA_OUT<=SAVE_B(23 DOWNTO 16);WHEN X"7"=>DATA_OUT<=SAVE_B(31 DOWNTO 24);WHEN X"8"=>DATA_OUT<=SAVE_WIDE(7 DOWNTO 0);WHEN X"9"=>DATA_OUT<=SAVE_WIDE(15 DOWNTO 8);WHEN X"A"=>DATA_OUT<=SAVE_WIDE(23 DOWNTO 16);WHEN X"B"=>DATA_OUT<=SAVE_WIDE(31 DOWNTO 24);WHEN OTHERS=>NULL;END CASE;ELSE NULL;END IF;ELSE NULL;END IF;END PROCESS;END ARCH;单片机:/* *.c文件,文件名:EqualFre_main.c*各模块的流程控制*/#include "EqualFre_main.h"int main(void){communicationInit_Ex();while(1){mode = getMode_Ex(); //确定选择的模式askForData_Ex(); //请求数据if(HOLD_DATA_MODE != mode){ //表示没有固定数据时,则载入数据loadData();}disData(); //数据显示}}//数据载入static void loadData(){fre = getFre_Ex();wide = getWide_Ex();duty = getDuty_Ex();}/***************************************数据显示中:wData(uchar) 传入的参数意义0 - 9 数字0-910 - 19 跟了点号的0-920 暗选***************************************/static void disDelay(){ //显示延时uchar data x,y;for(x=250;x>0;x--)for(y=50;y>0;y--);}//数据显示--总控static void disData(){switch(mode){case SHOW_FRE_MODE: disFre(); disDelay(); break;case SHOW_WIDE_MODE: disWide(); disDelay();break;case SHOW_DUTY_MODE: disDuty(); disDelay(); break;default:break;}}/*static void disFre(){uchar data i;for(i=0;i<8;i++)wData_Ex(1);}static void disWide(){uchar data i;for(i=0;i<8;i++)wData_Ex(2);}static void disDuty(){uchar data i;for(i=0;i<8;i++)wData_Ex(3);}*///数据显示--显示频率,单位Hz或MHz(双模式)static void disFre(){uchar data dataTemp[8],i;ulong data freTemp = fre;//为了显示1位小数,这里已经将频率扩大10倍uchar data flag = 0;//消零标志位if(1000000 <= freTemp){//当频率值大于1M时,使用兆显示模式freTemp /= 100000;//0.00MHzfor(i=2;i<8;i++){//数据从低位到高位装入数据暂存器dataTemp,这里保留2位,用于显示nH(即MHz)dataTemp[i] = (uchar)(freTemp%10);freTemp /= 10;}dataTemp[4] += 10;//取2位小数,这里是加入小数点dataTemp[1] = 21;//ndataTemp[0] = 22;//H}else{for(i=1;i<8;i++){dataTemp[i] = (uchar)(freTemp%10);freTemp /= 10;}dataTemp[2] += 10;dataTemp[0] = 22;//H}for(i=0;i<8;i++){//数据从高位到低位显示,并进行高位消零操作if(0 != dataTemp[7-i]){flag = 1;}if((0==dataTemp[7-i])&&(0==flag)){dataTemp[7-i] = 20;}wData_Ex(dataTemp[7-i]); //显示数据}}//数据显示--显示脉宽,单位us,意味着最大只能测1MHz的频率static void disWide(){uchar data dataTemp[8],i;ulong data wideTemp = wide;uchar data flag = 0;for(i=0;i<8;i++){dataTemp[i] = (uchar)(wideTemp%10);wideTemp /= 10;}for(i=0;i<8;i++){//数据从高位到低位显示,并进行高位消零操作if(0 != dataTemp[7-i]){flag = 1;}dataTemp[1]|=10;if((0==dataTemp[7-i])&&(0==flag)){dataTemp[7-i] = 20;}wData_Ex(dataTemp[7-i]);}}//数据显示--显示占空比static void disDuty(){uchar data dataTemp[4],i;uint data dutyTemp = duty;for(i=0;i<4;i++){dataTemp[i] = (uchar)(dutyTemp%10);dutyTemp /= 10;}dataTemp[2] += 10;wData_Ex(20);//补4个暗选wData_Ex(20);wData_Ex(20);wData_Ex(20);for(i=0;i<4;i++){wData_Ex(dataTemp[3-i]);}}/**.h文件,文件名:EqulaFre_SGMDisplay.h*SGM显示模块,用于显示由主程序传过来的数据*硬件资源:164时钟端--P3.1164数据端--P3.0*/#ifndef _EQUALFRE_SGMDISPLAY_H_H_#define _EQUALFRE_SGMDISPLAY_H_H_#include<reg52.h>#include<intrins.h>#define uchar unsigned charsbit sgm_clk=P3^1; //164时钟端sbit sgm_data=P3^0; //164数据端static uchar code num[] = {//从低位到高位,高电平有效0xfc,0x60,0xda,0xf2,0x66,0xb6,0xbe,0xe0,0xfe,0xf6,//数字0-90xfd,0x61,0xdb,0xf3,0x67,0xb7,0xbf,0xe1,0xff,0xf7,//带点号的0-90x00,0x2a,0x6e//暗选,n,h};//接口函数void wData_Ex(uchar ); //在数码管上显示数据#endif/**.c文件,文件名:EqualFre_SGMDisplay.c*/#include "EqualFre_SGMDisplay.h"//接口函数void wData_Ex(uchar index){uchar data i,byte;byte = num[index];for(i=0;i<8;i++){sgm_clk = 0;sgm_data = (bit)((byte>>i)&0x01);_nop_();sgm_clk = 1;_nop_();}}/**.c文件,文件名:EqualFre_modeFromKey.c*/#include "EqualFre_modeFromKey.h"//**************内部函数************//按键检测延时static void keyDelay(){uchar data x,y;for(x=100;x>0;x--);for(y=200;y>0;y--) ;}//按键扫描static void keyScan(){ //选择模式if(0 == Key_Mode){keyDelay();if(1 == Key_Mode) return ;switch(mode){case SHOW_FRE_MODE: //测频率mode = SHOW_WIDE_MODE; //下一次测的是脉宽break;case SHOW_WIDE_MODE: //测脉宽mode = SHOW_DUTY_MODE; //下一次测的是占空比break;case SHOW_DUTY_MODE: //测占空比mode = SHOW_FRE_MODE; //下一次测的是频率break;default:mode = SHOW_FRE_MODE;break;}while(0 == Key_Mode) ;keyDelay();}if(0 == Key_Hold_Data){keyDelay();if(1 == Key_Hold_Data) return ;mode = HOLD_DATA_MODE; //按下Key_Hold_Data,即为P1^1时,数据保持不变while(0 == Key_Hold_Data);keyDelay();}}//*******************接口函数**************uchar getMode_Ex(void){ //返回mode,确定选择的模式keyScan();return mode;}/**.h文件,文件名:equalFre.h*模式控制模块,通过键盘来控制模式的选择,并将所选模式传递给函数*所使用的硬件资源:频率显示、脉宽显示、占空比显示的切换建---P1.0测试值保持键-- P1^1*/#ifndef _EQUALFRE_MODEFROMKEY_H_H_#define _EQUALFRE_MODEFROMKEY_H_H_#include<reg52.h>#define SHOW_FRE_MODE 0#define SHOW_WIDE_MODE 1#define SHOW_DUTY_MODE 2#define HOLD_DATA_MODE 3#define uchar unsigned charsbit Key_Mode = P1^0; //实现频率显示,脉宽显示,占空比显示的转化sbit Key_Hold_Data = P1^1; //将测得的数值定住static uchar data mode;//内部函数static void keyDelay(); //按键检测延时static void keyScan(); //按键扫描//接口函数uchar getMode_Ex(void); //在数码管上显示数据#endif/**.h文件,文件名:EqulaFre_communication.h*通信模块,用于和FPGA通信,获取频率、脉宽、占空比的原始数据。