数字电路_第八章答案

基础电子技术 习题解答 第8章 组合数字电路习题解答

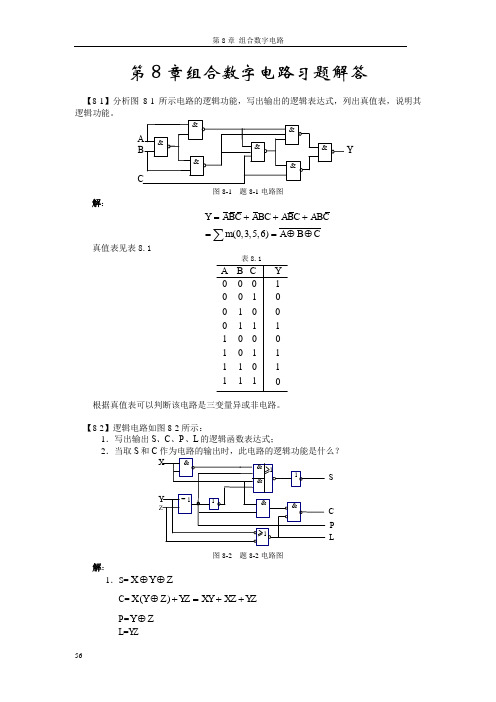

第8章组合数字电路习题解答【8-1】分析图8-1所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

A B &&&&&&&CY图8-1 题8-1电路图解:(0,3,5,6)Y ABC ABC ABC ABC m A B C=+++==⊕⊕∑真值表见表8.1表8.1Y C B A 10001000010011100101110111111000根据真值表可以判断该电路是三变量异或非电路。

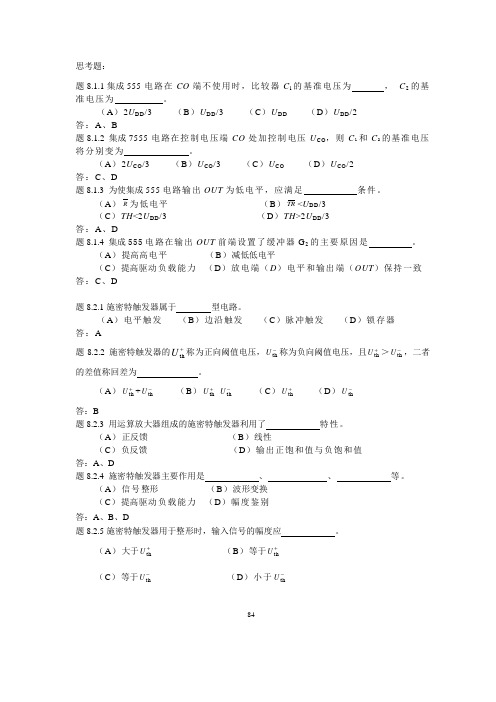

【8-2】逻辑电路如图8-2所示:1.写出输出S 、C 、P 、L 的逻辑函数表达式;2.当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?=1&&1&&11&1XYZSC P L图8-2 题8-2电路图解:1.S=X Y Z ⊕⊕C =()X Y Z YZ XY XZ YZ ⊕+=++ P =Y Z ⊕ L =YZ2.当取S 和C 作为电路的输出时,此电路为全加器。

【8-3】 图8-3为由三个全加器构成的电路,试写出其输出F 1,F 2,F 3,F 4的表达式。

A iB iC i-1S i C iA iB iC S i C iA iB iC i-1S i C iX YZ12F 3F 4i-1图8-3 题8-3电路图解:F 1=X Y Z ⊕⊕ 2()F X Y Z =⊕⋅3F XY Z =⊕ 4F XYZ =【8-4】图8-4为集成4位全加器74LS283和或非门构成的电路,已知输入DCBA 为BCD8421码,写出B 2 B 1的表达式,并列表说明输出''''A B C D 为何种编码?A 3A 2A 1A 0S 3 S 2S 1 S 0C 0C 4D' C' B' A'74LS283D C B AB 3 B 2B 1B 041>1>1>图8-4 题8-4电路图解:21B B D B A D C D CB CA ==++++=++若输入DCBA 为BCD8421码,列表可知D 'C 'B 'A '为BCD2421码。

数字电路第8章存储器

说,它的存储容量为2 n×m位。

存储器的容量=字数×位数 或门阵列来实现。

ROM的容量由

JHR

数字电路第8章存储器

2. 4×4ROM的电路结构和简化框图

JHR

数字电路第8章存储器

JHR

数字电路第8章存储器

单位有位、字节、字、字长等的基本概念。

(1)位

计算机系统中,一个二进制的取值单位称为 二进制位,简称“位”,用b表示(bit的缩写),是表 示信息的最小单位。

JHR

数字电路第8章存储器

(2)字节

通常将8个二进制位称为一个字节,即连续8个 比特,就是一个字节。简称B(Byte的缩写),是 表示的基本单元。在微型计算机中,往往以字节 为单位来表示文件或数据的长度以及存储器容量 的大小。除此之外,还可用K,M,G或T为单位。 例如,一台电脑的内存是128兆字节,就是说这台 电脑有128个百万字节的内存。

3. 4×4ROM电路的工作原理

(1)当使能控制S=1时,A0、A1在“00~11”中 取值,W0~W3中必有一根被选中为“1”。此时,若 位线与该字线交叉点上跨接有二极管,则该二极管 导通,使相应的位线输出为“1”;若位线与字线交叉 点无二极管,则相应的位线输出为“0”。

存储器(Memory ):是数字系统中记忆大量 信息的部件。

存储器的功能:是存放不同程序的操作指令及 各种需要计算、处理的数据,所以它相当于系统存 储信息的仓库。

典型的存储器:由数以千万计的有记忆功能的 存储单元组成,每个存储单元可存放一位二进制数 码和信息。

随着大规模集成电路制作技术的发展,半导体 存储器因其集成度高、体积小、速度快,目前广泛 应用于各种数字系统中。

数字电子技术基础课后习题答案第8章习题答案

84题8.1.1集成555电路在CO 端不使用时,比较器C l 的基准电压为 , C 2的基准电压为 。

(A )2U DD /3 (B )U DD /3 (C )U DD (D )U DD /2 答:A 、B题8.1.2 集成7555电路在控制电压端CO 处加控制电压U CO ,则C 1和C 2的基准电压将分别变为 。

(A )2U CO /3 (B )U CO /3 (C )U CO (D )U CO /2 答:C 、D题8.1.3 为使集成555电路输出OUT 为低电平,应满足 条件。

(A )R 为低电平 (B )TR <U DD /3 (C )TH <2U DD /3 (D )TH >2U DD /3 答:A 、D题8.1.4 集成555电路在输出OUT 前端设置了缓冲器G 2的主要原因是 。

(A )提高高电平 (B )减低低电平(C )提高驱动负载能力 (D )放电端(D )电平和输出端(OUT )保持一致 答:C 、D题8.2.1施密特触发器属于 型电路。

(A )电平触发 (B )边沿触发 (C )脉冲触发 (D )锁存器 答:A题8.2.2 施密特触发器的+th U 称为正向阈值电压,-th U 称为负向阈值电压,且+th U >-th U ,二者的差值称回差为 。

(A )+th U +-th U (B )+th U --th U (C )+th U (D )-th U答:B题8.2.3 用运算放大器组成的施密特触发器利用了 特性。

(A )正反馈 (B )线性(C )负反馈 (D )输出正饱和值与负饱和值 答:A 、D题8.2.4 施密特触发器主要作用是 、 、 等。

(A )信号整形 (B )波形变换 (C )提高驱动负载能力 (D )幅度鉴别 答:A 、B 、D题8.2.5施密特触发器用于整形时,输入信号的幅度应 。

(A )大于+th U (B )等于+th U (C )等于-th U(D )小于-th U题8.2.6 可将变化缓慢的输入信号变换为矩形脉冲信号。

《数电》教材习题答案 第8章习题答案

思考题与习题8-1 试问一个256字×4位的ROM应有地址线、数据线、字线和位线各多少根?8根地址线,4根数据线,字线即行选线,8根;位线即列选线,4根。

8-2 用一个2线-4线译码器和4片1024×8位的ROM组成一个容量为4096×8位的ROM,请画出连线图。

电路为字扩展方式。

2线-4线译码器的输出为低电平有效,分别接至四片1024×8位的ROM 的,将地址线、输出线对应连接。

图略。

8-3 确定用ROM实现下列逻辑函数所需的容量:(1)比较两个四位二进制数的大小及是否相等;(2)两个三位二进制数相乘的乘法器;(3)将8位二进制数转化为十进制数的转化电路。

(1) 根据题意,两个四位数比较的结果有相等,大于或者小于三种结果,因此输入为8位,输出为三位,ROM容量为:28×3=768(2)最大的三位二进制数为7×7=49=110001B,因此输出为6位;则ROM的容量为26×6=384(3)最大的八位二进制数为255,因此输出为3位,而输入为8位,则其ROM容量为28×3=7688-4 图8-4为256×4位RAM芯片的逻辑电路图,请用位扩展的方法组成256×8位的RAM,画出逻辑连线图。

将两片的地址输入信号分别相连,用同一个信号控制8个相同字数的RAM,输出分别为两片的4位输出,就可达到扩展输出的结果,图略。

8-5 试用EFPOM实现74LS49的功能。

74LS49为7段显示译码器,输入为4位,输出为7为,根据74LS49的功能表,可写出输出a,b,c,d,e,f,g的表达式。

用或阵列,经过输出缓冲器,得到输出a,b,c,d,e,f,g。

图略。

1。

数字电路答案第八章

第八章脉冲产生与整形在时序电路中,常常需要用到不同幅度、宽度以及具有陡峭边沿的脉冲信号。

事实上,数字系统几乎离不开脉冲信号。

获取这些脉冲信号的方法通常有两种:直接产生或者利用已有信号变换得到。

本章主要讨论常用的脉冲产生和整形电路的结构、工作原理、性能分析等,常见的脉冲电路有:单稳态触发器、施密特触发器和多谐振荡器。

第一节基本知识、重点与难点一、基本知识(一)常用脉冲产生和整形电路1. 施密特触发器(1)电路特点施密特触发器是常用的脉冲变换和脉冲整形电路。

电路主要有两个特点:一是施密特触发器是电平型触发电路;二是施密特触发器电压传输特性具有回差特性,或称滞回特性。

输入信号在低电平上升过程中,电路输出状态发生转换时对应的输入电平称为正向阈值电压U T+,输入信号在高电平下降过程中,电路状态转换对应的输入电平称为负向阈值电压U T-,U T+与U T-的差值称为回差电压ΔU T。

(2)电路构成及参数施密特触发器有多种构成方式,如:门电路构成、集成施密特触发器、555定时器构成。

主要电路参数:正向阈值电压U T+、负向阈值电压U T-和回差电压ΔU T。

(3)电路应用施密特触发器主要应用范围:波形变换、波形整形和幅度鉴别等。

2. 单稳态触发器(1)电路特点单稳态触发器特点如下:①单稳态触发器有稳态和暂稳态两个不同的工作状态;②在外加触发信号的作用下,触发器可以从稳态翻转到暂稳态,暂稳态维持一段时间,自动返回原稳态;③暂稳态维持时间的长短取决于电路参数R和C。

(2)电路构成及参数单稳态触发器有多种构成方式,如:门电路构成的积分型单稳态触发器、门电路构成的微分型单稳态触发器、集成单稳态触发器、555定时器构成的单稳态触发器等。

主要电路参数:暂稳态的维持时间t w、恢复时间t re 、分辨时间t d、输出脉冲幅度U m。

(3)电路应用单稳态触发器主要应用范围:定时、延时、脉冲波形整形等。

3. 多谐振荡器多谐振荡器是一种自激振荡器,接通电源后,就可以自动产生矩形脉冲,是数字系统中产生脉冲信号的主要电路。

(整理)《数字电子技术》康华光习题解答第八章半导体存储器和可编程逻辑器件.

第八章半导体存储器和可编程逻辑器件一、填空题1、一个10位地址码、8位输出的ROM,其存储容量为或。

2、将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有根地址线,有根数据读出线。

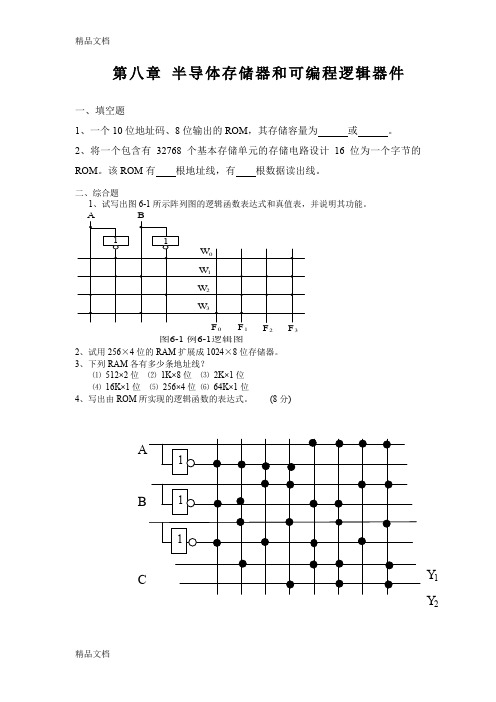

二、综合题1、试写出图6-1所示阵列图的逻辑函数表达式和真值表,并说明其功能。

01F2F3图6-1 例6-1逻辑图2、试用256×4位的RAM扩展成1024×8位存储器。

3、下列RAM各有多少条地址线?⑴512×2位⑵1K×8位⑶2K×1位⑷16K×1位⑸256×4位⑹64K×1位4、写出由ROM所实现的逻辑函数的表达式。

(8分)Y1Y25、四片16×4RAM 和逻辑门构成的电路如图6-7所示。

试回答:AB AB 4AB AB 0地址线数据线图6-7 多片RAM 级联逻辑图⑴单片RAM 的存储容量,扩展后的RAM 总容量是多少?⑵图6-7所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展? ⑶当地址码为00010110时,RAM0~RAM3,哪几片被选中?6.用ROM 设计一个组合逻辑电路,用来产生下列一组逻辑函数。

画出存储矩阵的点阵图。

D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=1 D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=2 D C B D B A Y ⋅⋅+⋅⋅=3D B D B Y ⋅+⋅=47、画出实现下面双输出逻辑函数的PLD 表示。

D C AB CD B A D C B A D C B A D C B A f ABCC B A C B A C B A f ),,,( ),,(21+++=++=三、简答题1、可编程逻辑器件是如何进行分类的?2、GAL16V8的OLMC 中4个数据选择器各有多少功能?3、ROM 和RAM 有什么相同和不同之处?ROM 写入信息有几种方式?4、为什么用ROM 可以实现逻辑函数式?第八章 习题答案一、填空题1、2138K 2、11 16 二、综合题1、解:根据与阵列的输出为AB 的最小项和阵列图中有实心点·为1,无·为0,可以写出AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图6-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

数字逻辑电路王秀敏第8章7.10

数字逻辑电路王秀敏第8章7.10第⼋章检测题⼀、可以⽤来暂时存放数据的器件叫寄存器。

⼆、移位寄存器除寄存数据功能外,还有移位功能。

三、某寄存器由D触发器构成,有4位代码要存储,此寄存器必须由 4 个触发器构成。

四、⼀个四位⼆进制加法计数器,由0000状态开始,问经过18个输⼊脉冲后,此计数器的状态为 0010 。

五、n级环形计数器的计数长度是n,n级扭环形计数器的计数长度是2n。

六、集成计数器的模值是固定的,但可以⽤清零法和置数法来改变它们的模值。

七、通过级联⽅式,把两⽚4位⼆进制计数器74161连接成为8位⼆进制计数器后,其最⼤模值是 256 ;将3⽚4位⼗进制计数器74160连接成12位⼗进制计数器后,其最⼤模值是4096 。

⼋、设计模值为38的计数器⾄少需要 6 个触发器。

习题[题8.1] 试画出⽤2⽚74LS194A 组成8位双向移位寄存器的逻辑图。

74LS194A 的功能表见表8.1.4。

解:电路逻辑图如图A8.1所⽰图A8.1[题8.2] 图P8.2所⽰电路是⽤8选1数据选择器74LS151和移位寄存器CC40194组成的序列信号发⽣器。

试分析在C P 脉冲作⽤下电路的输出序列信号(Y )。

图P8.2解:74LS194A 组成3位扭环形计数器210Q Q Q :000→001 →011 →111 →110 →100 →000,因此74LS151输出013764Y D D D D D D …=111100…。

[题8.3] 分析图P8.3的计数器电路,画出电路的状态转换图,说明这是多少进制计数器。

⼗六进制计数器74161的功能表如表8.2.2所⽰。

图P8.3解:采⽤同步预置数法,31LD Q Q =。

计数器起始状态为0011,结束状态为1010,所以该计数器为⼋进制加法计数器。

状态转换图略。

[题8.4] 分析图P8.4的计数器电路,说明这是多少进制的计数器,并画出电路的状态转换图。

⼗进制计数器74160的功能表如表8.2.6所⽰。

数字电子技术课后习题答案

ABACBC

BC

A

00 01 11 10

00

1

0

1

11

0

1

0

Y ABC

❖ 3.13某医院有一、二、三、四号病室4间,每室设有 呼叫按钮,同时在护士值班室内对应的装有一号、 二号、三号、四号4个指示灯。

❖ 现要求当一号病室的按钮按下时,无论其它病室的 按钮是否按下,只有一号灯亮。当一号病室的按钮 没有按下而二号病室的按钮按下时,无论三、四号 病室的按钮是否按下,只有二号灯亮。当一、二号 病室的按钮都未按下而三号病室的按钮按下时,无 论四号病室的按钮是否按下,只有三号灯亮。只有 在一、二、三号病室的按钮均未按下四号病室的按 钮时,四号灯才亮。试用优先编码器74148和门电路 设计满足上述控制要求的逻辑电路,给出控制四个 指示灯状态的高、低电平信号。

HP RI/BIN

I0

0/ Z1 0 10 ≥1

I1

1/ Z1 1 11

I2

2/ Z1 2 12 18

YS

I3

3/ Z1 3 13

I4

4/ Z1 4 14

YEX

I5

5/ Z1 5 15

I6

6/ Z1 6 16

I7

7/ Z1 7 17

Y0

V18

Y1

ST

E N

Y2

(b)

74148

(a)引脚图;(b)逻辑符号

A

00 01 11 10

00

0

0

1

11

1

0

1

Y AB BC AC

由于存在AC 项,不存在相切的圈,故无冒险。

❖ 4.1在用或非门组成的基本RS触发器中,已知 输入SD 、RD的波形图如下,试画出输出Q, Q

数字电子技术基础第8章可编程逻辑器件

数字电子技术基础第8章可编程逻辑 器件

PLD是70年代发展起来的新型逻辑器件,是一种通用大规模 集成电路,用于LSI和VLSI设计中,采用软件和硬件相结合的方 法设计所需功能的数字系统。相继出现了ROM、PROM、PLA、 PAL、GAL、EPLD和FPGA等,它们组成基本相似。

数字电子技术基础第8章 可编程逻辑器件

2020/11/21

数字电子技术基础第8章可编程逻辑 器件

传统的逻辑系统,当规模增大时 (SSI MSI)

焊点多,可靠性下降 系统规模增加成本升高 功耗增加 占用空间扩大

连接线与点增多 抗干扰下降

数字电子技术基础第8章可编程逻辑 器件

从逻辑器件的功能和使用方法看,最初的逻辑器件全部采用标准通用 片,后来发展到采用用户片和现场片。

通用片的功能是器件厂制造时定死的,用户只能拿来使用而不能改变 其内部功能。

通用片有门、触发器、多路开关、加法器、寄存器、计数器、译码器 等逻辑器件和随机读写存储器件。

用户片是完全按用户要求设计的VLSI器件。它对用户来讲是优化的, 但是设计周期长,设计费用高,通用性低,销售量少。用户片一般称为专 用集成电路(ASIC),但是它也向通用方向发展。

PROM----可编程存储器

P

PLA----可编程逻辑阵列

L

PAL----可编程阵列逻辑

D

GAL----通用可编程阵列逻辑

FPGA----现场可编程门阵列

ispLSI----在系统可编程大规模集成电路

数字电子技术基础第8章可编程逻辑 器件

1.与固定、或编程: 与阵列全固定,即全译码;ROM和PROM

数字电子技术基础第8章可编程逻辑 器件

数字电路课后题参考答案

习题参考答案注:参考答案,并不是唯一答案或不一定是最好答案。

仅供大家参考。

第一章习题2. C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=3. 设:逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4. 设:A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5. 设:10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

C AB Z BA B A Y ⋅=⋅=6.输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

D C A B A Y CB DC BD B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32107. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

C A B A C B A F ⋅+⋅+⋅⋅=8. D C B D A H DC B AD C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=第二章习题1. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时其值为1,灯灭时其值为0;输出报警信号用Y 表示,灯正常工作时其值为0,灯出现故障时其值为1。

AC AB C B A Y ⋅⋅=2. 设:烟、温度和有害气体三种不同类型的探测器的输出信号用A 、B 、C 表示,作为报警信号电路的输入,有火灾探测信号时用1表示,没有时用0表示。

报警信号电路的书躇用Y 表示,有报警信号时用1表示,没有时用0表示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8 数字系统设计基础习题解答 1自我检测题[T8.1] 什么是数字系统?数字系统是指对数字信息进行存储、传输、处理的电子系统。

只要包括控制单元和数据处理单元就称为数字系统。

[T8.2] 说明自顶向下的设计方法及步骤。

首先从系统设计入手,在顶层将整个系统划分成几个子系统,然后逐级向下,再将每个子系统分为若干功能模块,每个功能模块还可以继续向下划分成子模块,直至分成许多最基本模块实现。

练习题[P8.1] 采用“自顶向下”设计方法设计一4位数字频率计,测量范围为0~9999Hz,假设被测信号为标准的方波信号。

解:(1)4位数字频率计的顶层原理图AA[3..0]BB[3..0]CC[3..0]DD[3..0](2)底层功能模块的设计①CNT10模块设计根据顶层设计对CNT10模块的功能定义,其VHDL语言源程序编写如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cnt10 ISPORT(clk:IN STD_LOGIC;clr:IN STD_LOGIC;cs:IN STD_LOGIC;qq:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);8 数字系统设计基础习题解答 2co:OUT STD_LOGIC);END cnt10;ARCHITECTURE one OF cnt10 ISBEGINPROCESS(clk,clr,cs)BEGINIF (clr=‘1’) THENqq<=“0000”;ELSIF (clk'EVENT AND clk=‘1’) THENIF (cs=‘1’) THENIF (qq=9) THENqq<=“0000”;ELSEqq<=qq+1;END IF;END IF;END IF;END PROCESS;PROCESS(qq)BEGINIF (qq=9) THENco<=‘0’;ELSEco<=‘1’;END IF;END PROCESS;END one;根据频率计的原理图,前级计数器的进位输出作为下一级计数器的时钟输入。

由于计数器采用时钟的上升沿触发,因此,计数器模块的进位输出设为低电平有效,以免下级计数器提前进位。

②LOCK模块的设计LOCK模块的功能是在锁存信号的上升沿将输入数据锁存到输出端,其VHDL语言源程序为:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;8 数字系统设计基础习题解答 3ENTITY lock ISPORT(clk:IN STD_LOGIC;dd:IN STD_LOGIC_VECTOR(3 DOWNTO 0);qq:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END lock;ARCHITECTURE one OF lock ISBEGINPROCESS(clk,dd)BEGINIF (clk'EVENT AND clk=‘1’) THENqq<=dd;END IF;END PROCESS;END one;③CNT12模块的设计CNT12模块的功能比较简单,主要实现十二进制加法计数器,其VHDL语言源程序为:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cnt12 ISPORT(clk: IN STD_LOGIC;qq : BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END cnt12;ARCHITECTURE one OF cnt12 ISBEGINPROCESS(clk)BEGINIF (clk'EVENT AND clk='1') THENIF (qq=11) THENqq<=“0000”;ELSEqq<=qq+1;END IF;END IF;8 数字系统设计基础习题解答 4END PROCESS;END one;④CODE模块的设计CODE模块对12进制计数器的状态进行译码产生控制信号。

其VHDL语言源程序为:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY code ISPORT(dd:IN STD_LOGIC_VECTOR(3 DOWNTO 0);cs:OUT STD_LOGIC;clr:OUT STD_LOGIC;lock:OUT STD_LOGIC);END code;ARCHITECTURE one OF code ISBEGINPROCESS(dd)BEGINIF (dd=0) THENclr<=‘1’;ELSEclr<=‘0’;END IF;IF (dd=11) THENlock<=‘1’;ELSElock<=‘0’;END IF;IF ( (dd > 0 ) AND (dd < 9 )) THENcs<=‘1’;ELSEcs<=‘0’;END IF;END PROCESS;END one;[P8.2] 十字路口的示意图如图P8.2-1所示。

在主干道和支干道上两个方向上都安装红、黄、绿三色信号灯。

Cx和Cy分别是安装在主干道和支干道上的传感器,输出高电平说明有车需要通过。

技术要求为:8 数字系统设计基础习题解答 5(1)如果只有一个方向有车时,则保持该方向畅通;当两个方向都有车时,主干道和支干道交替通行;(2)在只有主干道有车时,主干道亮绿灯,支干道亮红灯;当只有支干道有车时,主干道亮红灯,支干道亮绿灯;(3)当两个方向都有车时,则轮流亮绿灯和红灯。

主干道每次亮绿灯40s ,支干道每次亮绿灯20s ,在由绿灯转红灯之间亮5s 的黄灯。

图P8.2-2所示为交通灯控制系统结构框图。

控制系统由控制器和定时器两部分组成,定时器用于亮灯时间控制。

CNT 是定时的值,LD 是定时值的同步预置信号,高电平有效。

ST 是定时器状态信号,当定时结束时,ST 输出为1。

clk 是周期为秒的时钟信号,reset 是复位信号,低电平有效。

CNT图P8.1-1 十字路口示意图 图8.2-2 交通灯控制系统结构图根据交通灯控制系统的技术要求和结构图,完成以下内容: (1)画出控制器的ASM 图;(2)用VHDL 语言对控制器和定时器进行描述; (3)设计交通灯控制系统的顶层原理图; (4)完成实际电路的制作。

解:(1)顶层设计traffic 的VHDL 语言程序 library ieee ;use ieee.std_logic_1164.all ; use ieee.std_logic_signed.all ;entity traffic isport (reset ,clk ,cx ,cy :in std_logic ;Ra ,Ya ,Ga ,Rb ,Yb ,Gb :out std_logic ); end ;architecture one of traffic iscomponent control port (reset ,clk ,ST ,cx ,cy :in std_logic ; Ra ,Ya ,Ga ,Rb ,Yb ,Gb ,LD :out std_logic ;8 数字系统设计基础习题解答 6CNT:OUT integer range 0 to 63);end component;component counter port(reset,clk,LD:in std_logic;CNT:in integer range 0 to 63;ST:out std_logic);end component;signal ST,LD:std_logic;signal CNT:integer range 0 to 63;beginu1:controlport map(reset,clk,ST,cx,cy,Ra,Ya,Ga,Rb,Yb,Gb,LD,CNT);u2:counterport map (reset,clk,LD,CNT,ST);end;(2)底层模块counter的VHDL语言程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity counter isport(reset,clk,LD:in std_logic;CNT:integer range 0 to 63;ST:out std_logic);end ;architecture one of counter issignal Q:integer range 0 to 63;beginprocess(reset,clk)beginif(reset='0')thenQ<=40;Elsif(clk'event and clk='1')thenIf(LD='1')thenQ<=CNT;Elsif(Q/=0)thenQ<=Q-1;end if;end if;8 数字系统设计基础习题解答7end process;process(Q)beginif(Q=0)thenST<='1',elseST<='0';end if;end process;end;(3)底层模块control的VHDL语言程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity control isport(reset,clk,ST,cx,cy:in std_logic;Ra,Ya,Ga,Rb,Yb,Gb,LD:out std_logic;CNT:OUT integer range 0 to 63);End;architecture one of control isconstant T1:integer:=40;constant T2:integer:=20;constant T3:integer::=10;;type state_type is (S0,S1,S2,S3);signal state:state_type;signal RYG:std_logic_vector(5 downto 0);beginprocess(reset,clk)beginif (reset='0')then state<=S0;elsif(clk'event and clk='1')thenif (ST='1')THENcase state iswhen s0=>if(cy='0')then state<=S0;else state<=S1;end if;when S1=> state<=S2;when S2=> if(cx='0')then state<=S2;8 数字系统设计基础习题解答8else state<=S3;end if;when S3=>state<=S0;end case;end if;end if;end process;process(state)begincase state iswhen S0=>RYG<="001100";when S1=>RYG<="010100";when S2=>RYG<="100001";when S3=>RYG<="100010";end case;end process;process(state,cx,cy)begincase state iswhen S0=>if (cy='0')then CNT<=T1;else CNT<=T3;end if;when S1=>CNT<=T2;when S2=>if(cx='0')then CNT<=T2;else CNT<=T3;end if;when S3=>CNT<=T1;end case;end process;LD<=ST;Ra<=RYG(5);Ya<=RYG(4);Ga<=RYG(3);Rb<=RYG(2);Yb<=RYG(1);Gb<=RYG(0);End;。