二选一多路选择器

二选一数据选择器

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (2)2.1 电路逻辑图 (2)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (5)3.1总体版图设计及DRC验证 (5)3.1.1数据选择器版图设计步骤 (5)3.1.2版图验证 (8)3.2版图仿真 (9)四数据选择器版图LVS对比 (10)五结论及体会 (12)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二电路逻辑功能2.1 电路逻辑图=+(S是数据选择控制端,S为0时选择A,为1时选S择B)Y SA SB要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SA SB =+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y 01 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

二选一数据选择器

郑州工商学院

实验报告册所属课程名称:EDA技术及应用

院部:工学院

专业:电子科学与技术

班级:1702班

学号:170508070246

姓名:刘应许

指导教师:靳世红

1.新建一个工程,为工程指定工作目录,分配工程名称以及指定是最高层设计实体名称.将设计文件加入工程中,选择目标器件,选择综合器和仿真器,结束设计.

2.输入源文件,选择源文件类型,之后出现原理图文件编辑界面,工程中出现Block1.vhd文件.

3.输入VHDL代码.

4.打开波形编辑器,输入信号节点,编辑输入信号波形,观察仿真结果.仿真完成后可查看输出波形.

5.查看电路图.

二选一数据选择器

三人表决器。

实验三4位2选1多路选择器的设计与实现

实验三 4位2选1多路选择器的设计与实现一.实验目的1.使用ISE软件设计并仿真;2.学会程序下载。

二.实验内容使用ISE软件进行4位2选1多路选择器的设计与实现。

三.实验步骤1. 编写文本文件并编译2. 软件仿真3. 进行硬件配置四.实验原理1. ISE软件是一个支持数字系统设计的开发平台。

2. 用ISE软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。

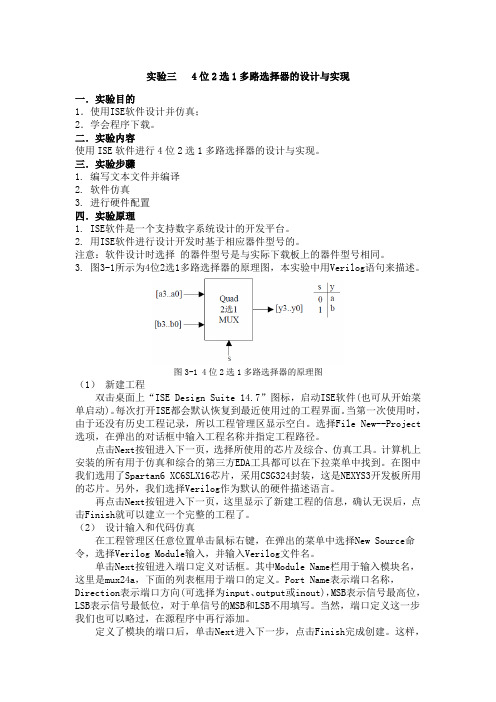

3. 图3-1所示为4位2选1多路选择器的原理图,本实验中用Verilog语句来描述。

图3-1 4位2选1多路选择器的原理图(1)新建工程双击桌面上“ISE Design Suite 14.7”图标,启动ISE软件(也可从开始菜单启动)。

每次打开ISE都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。

选择File New--Project 选项,在弹出的对话框中输入工程名称并指定工程路径。

点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到。

在图中我们选用了Spartan6 XC6SLX16芯片,采用CSG324封装,这是NEXYS3开发板所用的芯片。

另外,我们选择Verilog作为默认的硬件描述语言。

再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish就可以建立一个完整的工程了。

(2)设计输入和代码仿真在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,选择Verilog Module输入,并输入Verilog文件名。

单击Next按钮进入端口定义对话框。

其中Module Name栏用于输入模块名,这里是mux24a,下面的列表框用于端口的定义。

Port Name表示端口名称,Direction表示端口方向(可选择为input、output或inout),MSB表示信号最高位,LSB表示信号最低位,对于单信号的MSB和LSB不用填写。

二选一数据选择器

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (2)2.1 电路逻辑图 (2)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (5)3.1总体版图设计及DRC验证 (5)3.1.1数据选择器版图设计步骤 (5)3.1.2版图验证 (8)3.2版图仿真 (9)四数据选择器版图LVS对比 (10)五结论及体会 (12)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二电路逻辑功能2.1 电路逻辑图=+(S是数据选择控制端,S为0时选择A,为1时选S择B)Y SA SB要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SA SB =+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y 01 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

2选1多路选择器

EDA实验报告

通信三班

张晨明2012040161078

一、实验目的

熟悉quartusⅡ的VHDL文本设计全过程,学习简单组合电路的设计、多层次电路设计、仿真。

二、实验内容

实验内容:首先利用quartusⅡ完成2选1多路选择器(例4-3)的文本编译输入(mux21a.vhd)和仿真测试等步骤,最后在实验系统上硬件测试,验证此设计的功能。

将此多路选择器看成一个元件mux21a,利用元件例化语句描述成三选一,然后进行编译、综合、仿真。

引脚锁定以及硬件下载测试。

建议选实验电路模式5,用键1(PIO0)控制s0;用键2(PIO1)控制s1;a3、a2和a1分别接clock5、clock0和clock2;输出信号outy仍接扬声器spker。

通过短路帽选择clock0接256HZ 信号,clock5接1024HZ信号,clock2接8HZ信号。

最后选行编译、下载和硬件测试实验。

三、实验器材

Quartus II软件。

四、设计思路/原理图。

双二选一多路选择器课程设计

双二选一多路选择器课程设计1.实验目的2.电路设计过程2.1设计二选一多路选择器2.2设计双二选一多路选择器3.仿真结果3.1创建工程准备工作3.2创建新工程3.3编译前置3.4全程编译3.5时序仿真4.总结一、实验目的1、学会利用Quartus Ⅱ软件的原理图输入方法设计简单的逻辑电路;2、熟悉Quartus Ⅱ软件的VHDL文本设计流程全过程;3、学习简单组合电路的设计,层次化的设计方法4、熟悉利用Quartus Ⅱ软件对设计电路进行仿真的方法;二、电路设计过程1、设计2选1多路选择器a. 使用Quartus建立工程准备项目①新建一个文件夹。

在d盘中,路径为D:\wangchen 。

②打开Quartus软件③从【File】>>【New】>>【VHDL】新建文本编译窗口,出现新建项目框。

④输入源程序,编写2选1多路选择程序2选1多路源程序如下:ENTITY mux21a ISPORT (a,b,s:IN BIT;y:OUT BIT);END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGINPROCESS(a,b,s)BEGINIF s='0' THEN y<=a; ELSE y<=b; END IF;END PROCESS;END ARCHITECTURE one;⑤文件存盘选择File→Save As命令,找到已建立的文件夹D:\ wangchen,存盘文件名应与实体的名字一致,即mux21a,其界面窗口如下图所示。

b创建工程①打开建立新工程管理窗,选择File→New Preject Wizard工具选项创建设计工程命令,即弹出“工程设置”对话框如下图所示,单击对话框最上第一栏右侧的“…”按钮,找到文件夹D:\wangchen,选种已存盘的文件mux21a,再单击打开按钮,既出现如图所示的设置情况. 使用New Project Wizard可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称,还可以指定要在工程中使用的设计文件、其他源文件、用户库和EDA工具,以及目标器件系列和具体器件等。

二选一多路选择器原理

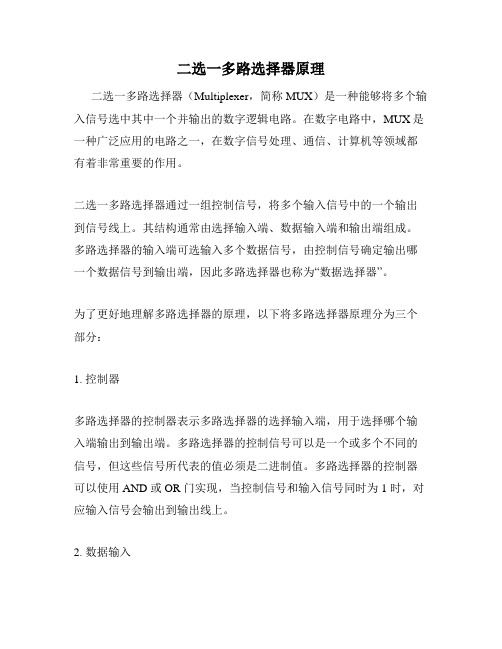

二选一多路选择器原理二选一多路选择器(Multiplexer,简称MUX)是一种能够将多个输入信号选中其中一个并输出的数字逻辑电路。

在数字电路中,MUX是一种广泛应用的电路之一,在数字信号处理、通信、计算机等领域都有着非常重要的作用。

二选一多路选择器通过一组控制信号,将多个输入信号中的一个输出到信号线上。

其结构通常由选择输入端、数据输入端和输出端组成。

多路选择器的输入端可选输入多个数据信号,由控制信号确定输出哪一个数据信号到输出端,因此多路选择器也称为“数据选择器”。

为了更好地理解多路选择器的原理,以下将多路选择器原理分为三个部分:1. 控制器多路选择器的控制器表示多路选择器的选择输入端,用于选择哪个输入端输出到输出端。

多路选择器的控制信号可以是一个或多个不同的信号,但这些信号所代表的值必须是二进制值。

多路选择器的控制器可以使用 AND 或 OR 门实现,当控制信号和输入信号同时为 1 时,对应输入信号会输出到输出线上。

2. 数据输入多路选择器的数据输入就是该选择器的多个输入端。

可以选择其中的一个输入端作为输出,这个输出端的值等于该输入端的值。

这些输入信号可以是数字信号、模拟信号或混合信号。

3. 输出多路选择器的输出端是计算机或其他设备使用的信号线。

多路选择器的输出值取决于选择输入端和输入端的状态。

当控制器的状态为0 时,多路选择器输出与第一个输入信号连接的值。

当控制器为 1 时,多路选择器输出与第二个输入信号相连的值。

这个选择过程由控制器完成。

综上所述,二选一多路选择器是一种能够将多个输入信号中的一个输出的数字逻辑电路。

其结构由选择输入端、数据输入端和输出端组成。

多路选择器通过一组控制信号,确定输出哪一个数据信号到输出端。

在数字信号处理、通信、计算机等领域中,多路选择器都有着广泛的应用,是非常重要的电路之一。

列表:1. 二选一多路选择器是什么?2. 多路选择器的控制器是如何实现的?3. 多路选择器的数据输入是什么?4. 多路选择器的输出是什么?5. 多路选择器在哪些领域有广泛的应用?。

2选1多路选择器数选器muxverilog

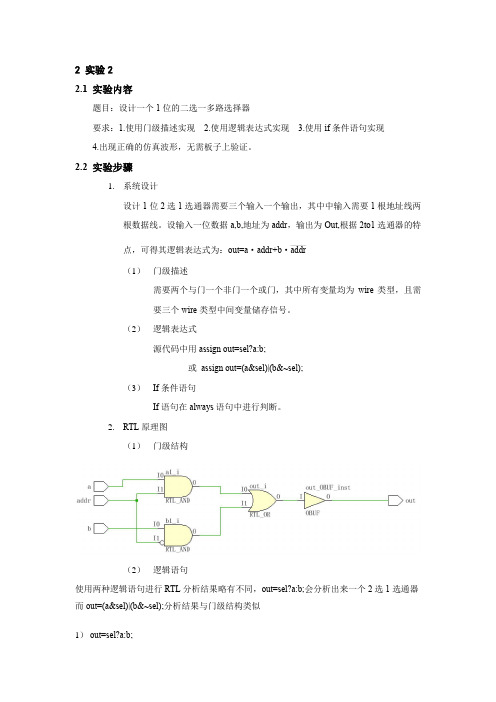

2 实验22.1 实验内容题目:设计一个1位的二选一多路选择器要求:1.使用门级描述实现 2.使用逻辑表达式实现 3.使用if条件语句实现4.出现正确的仿真波形,无需板子上验证。

2.2 实验步骤1.系统设计设计1位2选1选通器需要三个输入一个输出,其中中输入需要1根地址线两根数据线。

设输入一位数据a,b,地址为addr,输出为Out,根据2to1选通器的特_______点,可得其逻辑表达式为:out=a·addr+b·addr(1)门级描述需要两个与门一个非门一个或门,其中所有变量均为wire类型,且需要三个wire类型中间变量储存信号。

(2)逻辑表达式源代码中用assign out=sel?a:b;或assign out=(a&sel)|(b&~sel);(3)If条件语句If语句在always语句中进行判断。

2.RTL原理图(1)门级结构(2)逻辑语句使用两种逻辑语句进行RTL分析结果略有不同,out=sel?a:b;会分析出来一个2选1选通器而out=(a&sel)|(b&~sel);分析结果与门级结构类似1)out=sel?a:b;2)out=(a&sel)|(b&~sel);(3)if语句3.重要源代码及注释(1)门级结构module mux2_1(a,b,out,addr);input a,b,addr;output out;wire naddr,a1,b1;//定义中间变量not (naddr,addr);and (b1,b,naddr);and (a1,a,addr);or (out,a1,b1);endmodule(2)逻辑语句module luoji(input a,input b,input sel,output out);assign out=(a&sel)|(b&~sel);endmodule(3)if语句module mux2_1if(a,b,sel,out);input a,b,sel;output out;reg out;always@(a or b or sel)beginif(sel) out=a;else out=b;end2.3 结果分析1.Testbench代码(3种方式testbench 中代码类似,此处以if语句为例)module mux2_1if_tb();reg a,b,sel;mux2_1if m1(a,b,sel,out);initialbegina=0;b=0;sel=0;endalwaysbegin#10 a<=~a;endalwaysbegin#20 b<=~b;endalwaysbegin#15 sel<=1;#8 sel<=0;endendmodule2.仿真波形图(1)门级结构(2)逻辑语句(3)If语句3.说明三种方式均定义当选择端值为1时输出a,选择端值为0输出b;其中逻辑语句与if语句testbench部分代码相同,门级结构咯有不同,三种波形仿真图像均正确,符合2选1选通器功能。