二选一选择器仿真报告

EDA:实验六2选1和4选1多路选择实验

实验六 2选1和4选1多路选择实验班级:通信1121 姓名:王密学号:1121302230一、实验目的:1、了解2选1和4选1的工作原理和实现的方法。

2、实现两个多路选择器,一个2选1,一个4选1。

3、学会用于VHDL语言进行程序设计。

二、实验原理:2选1当选择输入S为L时,Y输出A, 当S为H时,Y输出B。

当选择输入AB为LL时,Y输出D0, 当AB为LH时,Y输出D1, 当AB为HL时,Y输出D2,当AB为HH时,Y输出D3。

说明:sw1选择是控制4选1,还是2选1,sw1=1,为4选1,sw1=0,为2选1。

sw3,sw2为4选1的地址,sw4为2选1的地址。

三、实验连线:1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG口连接起来,万用下载区右下角的电源开关拨到 SOPC下载的一边。

2、请将JPLED1短路帽右插,JPLED的短路帽全部上插。

3、将实验板左端的JP103全部用短路帽接上(共八个)。

四、实验内容与步骤:(程序:EP2C5\muxsel\muxsel.sof)1、打开Quartus II 6.0软件,点击“File→OpenP roject”出现如下的对话框(图9.1),选中muxsel,点打开即可;图9.12、点击“Tools-Programmer”后出现如下的对话窗口,3、在点”Edit→Add File………”出现如下对话框(图9.2),在图9.3对话框中,选中EP2C5/muxsel/muxsel.sof项目后点击打开回到Programmer对话框, 在下载对话窗口中“选中Program/ Configure”,点击“Start”即进行下载。

图9.2图9.3现将muxsel.vhd原程序作如下说明:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY liu123 ISPORT (SW1:IN BOOLEAN;SW2:IN STD_LOGIC;SW3:IN STD_LOGIC;SW4:IN BOOLEAN;LED:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END liu123;ARCHITECTURE ADO OF liu123 ISSIGNAL RST_MUXSEL: STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL RST_MUXSEL2: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINPROCESS(SW1,SW2,SW3)beginIF (SW2='0' AND SW3 ='0') THEN RST_MUXSEL<="10101010";ELSIF (SW2='0' AND SW3='1' )THEN RST_MUXSEL<="01010101";ELSIF (SW2='1' AND SW3='0')THEN RST_MUXSEL<="10001000";ELSIF (SW2='1' AND SW3='1') THEN RST_MUXSEL<="01110111";ELSE RST_MUXSEL<="XXXXXXXX";END IF;E ND PROCESS;PROCESS (SW4)BEGINIF SW4 THENRST_MUXSEL2<="10100101";ELSERST_MUXSEL2<="01011010";END IF;END PROCESS;PROCESS(SW1,RST_MUXSEL,RST_MUXSEL2)BEGINcase sw1 iswhen true => LED<=RST_MUXSEL;when false => LED<=RST_MUXSEL2;END case;END PROCESS;END ADO;引脚分配(Cyclone EP2C5Q208C8):sw1-P43,sw2-P44,sw3-P45,sw4-P46,led0-P13,led1-P14,led2-P15,led3-P30,led4-P3 1,led5-P33,led6-P34,led7-P35,管脚标号led0到led7分别接到8位的LED流水灯上,使用高低电平观察输出的结果,sw1到sw4接到拨码开关上,。

实验三4位2选1多路选择器的设计与实现

实验三 4位2选1多路选择器的设计与实现一.实验目的1.使用ISE软件设计并仿真;2.学会程序下载。

二.实验内容使用ISE软件进行4位2选1多路选择器的设计与实现。

三.实验步骤1. 编写文本文件并编译2. 软件仿真3. 进行硬件配置四.实验原理1. ISE软件是一个支持数字系统设计的开发平台。

2. 用ISE软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。

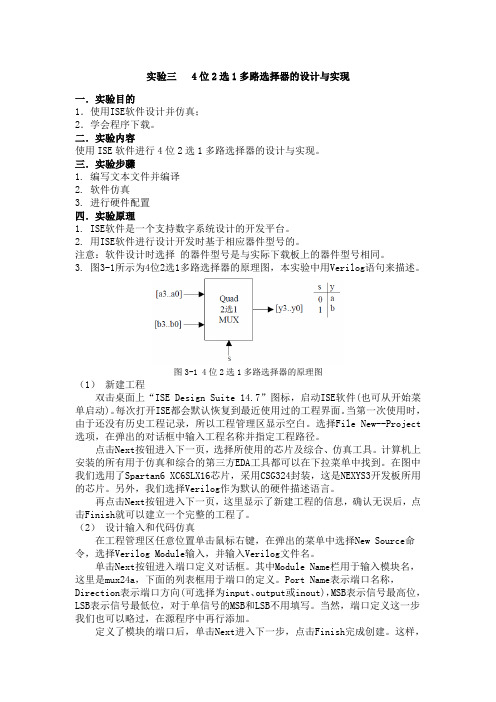

3. 图3-1所示为4位2选1多路选择器的原理图,本实验中用Verilog语句来描述。

图3-1 4位2选1多路选择器的原理图(1)新建工程双击桌面上“ISE Design Suite 14.7”图标,启动ISE软件(也可从开始菜单启动)。

每次打开ISE都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。

选择File New--Project 选项,在弹出的对话框中输入工程名称并指定工程路径。

点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到。

在图中我们选用了Spartan6 XC6SLX16芯片,采用CSG324封装,这是NEXYS3开发板所用的芯片。

另外,我们选择Verilog作为默认的硬件描述语言。

再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish就可以建立一个完整的工程了。

(2)设计输入和代码仿真在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,选择Verilog Module输入,并输入Verilog文件名。

单击Next按钮进入端口定义对话框。

其中Module Name栏用于输入模块名,这里是mux24a,下面的列表框用于端口的定义。

Port Name表示端口名称,Direction表示端口方向(可选择为input、output或inout),MSB表示信号最高位,LSB表示信号最低位,对于单信号的MSB和LSB不用填写。

二选一数据选择器

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (2)2.1 电路逻辑图 (2)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (5)3.1总体版图设计及DRC验证 (5)3.1.1数据选择器版图设计步骤 (5)3.1.2版图验证 (8)3.2版图仿真 (9)四数据选择器版图LVS对比 (10)五结论及体会 (12)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二电路逻辑功能2.1 电路逻辑图=+(S是数据选择控制端,S为0时选择A,为1时选S择B)Y SA SB要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SA SB =+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y 01 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

数据选择器及其应用实验报告

数据选择器及其应用实验报告实验目的:

本实验的目的是通过实现数据选择器的功能,加深对于数字电路的理解,并提升对于数字电路实现的实践能力。

实验原理:

数据选择器是一种能够从多个数据信号中选择特定信号输出的数字电路,通常它有一个或多个数据输入线、一个或多个控制输入线、一个输出线和一个使能输入线。

在数据选择器输出线上的输出值,取决于控制输入线上的值以及选择从哪一个数据输入线接收数据信号。

在本次实验中,我们使用的是双二选一的数码开关。

“双”指的是它一共有两个信道供选择,“二选一”则代表只会选择其中一个信道作为输出。

实验步骤:

1.根据实验原理和实验材料的提供,搭建实验电路。

2.设置信号源,对选择器进行输入数据和控制信号的测试。

3.根据信号源输出的数据,通过实验电路计算出数据选择器输出的结果。

4.逐一更改控制信号的值,反复测试并记录数据。

并对实验记录进行整理和比较分析,以达到理解、检验和加深对数据选择器的认识。

实验结果:

在实验中我们完成了数据选择器的搭建和调试,并通过多次实验数据的记录与比较,成功实现了数据选择器的功能。

实验结论:

通过本次实验,我们深入学习了数据选择器的工作原理和实现方式,并从中进一步了解了数字电路的基本概念和实现方式。

通

过反复实验和分析,我们成功完成了数据选择器的功能调试,提升了我们的实践能力和对数字电路的理解。

Verilog入门训练3—二选一数据选择器

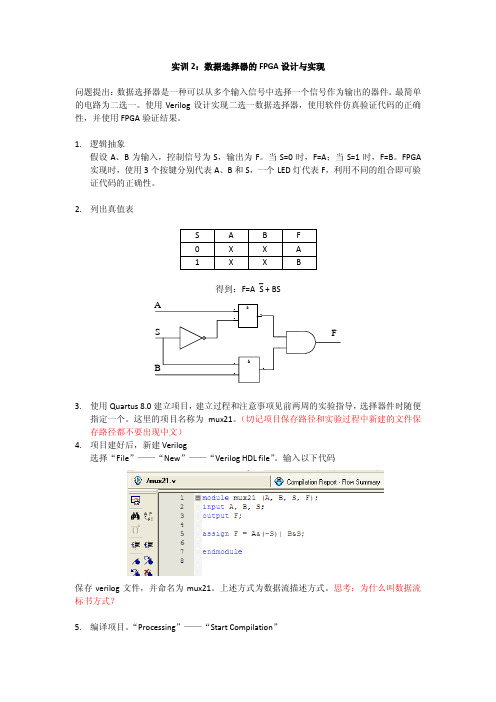

得到:F=AS + BS

A S

0

&

0

0

F

&

0 0

B

0

3. 使用 Quartus 8.0 建立项目, 建立过程和注意事项见前两周的实验指导, 选择器件时随便 指定一个。这里的项目名称为 mux21。 (切记项目保存路径和实验过程中新建的文件保 存路径都不要出现中文) 4. 项目建好后,新建 Verilog 选择“File”——“New”——“Verilog HDL file” 。输入以下代码

仿真成功后,回到波形文件,会弹出提示如下:

选择“是”来更新仿真结果,如下图所示:

根据仿真结果分析,例如在红线所在位置,S=1,因此 F 应该等于 B。这时候 B 的值为 0,因 此 F=0,结果正确。也可以从其他任意位置分析,看电路是否符合要求。 7. 指定引脚 点击“File”——“Save Project” ,然后关闭 quartus 8.0。打开 Quartus 11.0,选择“Open Project” ,找到上面保存的项目。项目打开后,首先更换器件,方法如下:点击项目中 器件(刚才随便指定的) ,右键,选择“Device”

在出现的编辑界面左侧右键,选择如下:

在“Insert Node or Bus”里选择“Node Finder…”

在弹出来的 “Node Finder” 中 ,首先 在“Filter” 中 选择 “Pins: Unassigned” , 然 后点 击“list” ,

在“Nodes Found”中会列出所有的引脚,第三步选择全部引脚(鼠标拉) ,点击“>>” , 最 后点击“OK”即可。在回到的“Insert Node or Bus”界面点击“OK” 。

[Word]二选一数据选择器

![[Word]二选一数据选择器](https://img.taocdn.com/s3/m/cd2d6a68a36925c52cc58bd63186bceb19e8edf9.png)

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (3)2.1 电路逻辑图 (3)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (6)3.1总体版图设计及DRC验证 (6)3.1.1数据选择器版图设计步骤 (6)3.1.2版图验证 (9)3.2版图仿真 (10)四数据选择器版图LVS对比 (11)五结论及体会 (13)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二 电路逻辑功能2.1 电路逻辑图Y SA SB =+(S 是数据选择控制端,S 为0时选择A ,为1时选S 择B )要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SA SB=+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y1 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

二选一数据选择器

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (2)2.1 电路逻辑图 (2)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (5)3.1总体版图设计及DRC验证 (5)3.1.1数据选择器版图设计步骤 (5)3.1.2版图验证 (8)3.2版图仿真 (9)四数据选择器版图LVS对比 (10)五结论及体会 (12)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二电路逻辑功能2.1 电路逻辑图=+(S是数据选择控制端,S为0时选择A,为1时选S择B)Y SA SB要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SASB =+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y 01 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

EDA实验1lxm二选一数据选择器

实验一二选一数据选择器VHDL设计Quartus II 6.0开发环境与EDA实验箱使用一实验目的1.熟悉在Quartus II 6.0环境下原理图输入方法。

2.熟悉Quartus II 6.0环境下编辑、编译综合、仿真的操作方法。

3、掌握利用EDA软件进行电路设计的详细流程;4、熟悉EDA实验箱的基本使用方法。

学会对实验板上的FPGA/CPLD进行编程下载,硬件验证自己的设计项目。

二实验仪器PC机、Quartus II 6.0软件三实验内容1.详细解读教材117页。

2.在QuartusⅡ上输入该设计的原理图,并进行编辑、编译、综合、适配、仿真。

3.给出其所有信号的时序仿真波形。

四实验原理及步骤1.启动Quartus II 6.0软件在桌面上双击Quartus II 6.0图标或者在开始—>所有程序—>Altera—> Quartus II 6.0,如下图2.建立工作库文件夹及工程任何一次设计都是一项工程(Project),所有此工程相关的所有设计文件都需要放在同一个文件夹里。

不同的设计放在不同的文件夹中。

在E盘下建立一个存放本次设计的工程文件夹,比如“shiyan1”。

注意不要使用中文文件夹,文件夹的存放路径也不要包含中文。

注意本实验室计算机C盘和D盘是重启后复原,不要将任何文件和文件夹放置在桌面或者C、D盘下。

初次打开Quartus II 6.0,会有如图提示:选择是的情况下,首先是新工程向导:介绍下一步下一步下一步,选择目标芯片,首先在Family栏选择ACEX1K系列,然后选择此系列的具体芯片:EP1K30TC144-3。

注意不要选成了EP1K30TC144-3。

下一步就点完成。

3.建立文本程序文件选择File菜单下的New或者直接点击工具栏中的新建图标,选择新建文件类型为VHDL File。

接下来另存文件:保存时需更改文件名与项目名称一样,注意保存在同一个工程文件夹下面。