双4选1数据选择器74LS153

74LS153译码器组合逻辑电路设计案例分析

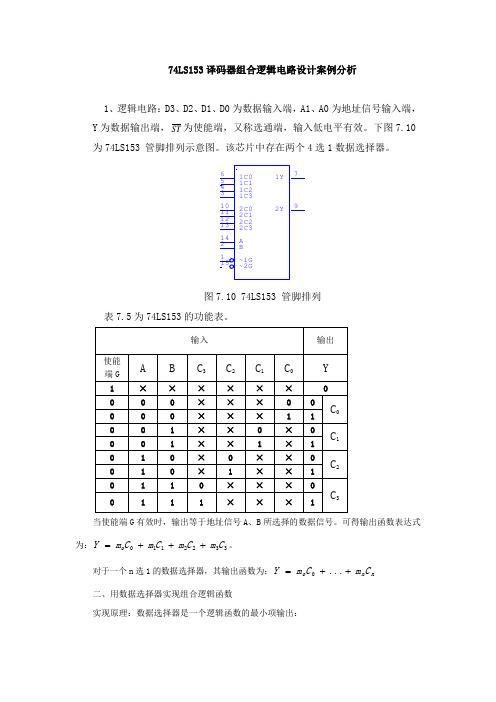

74LS153译码器组合逻辑电路设计案例分析1、逻辑电路:D3、D2、D1、D0为数据输入端,A1、A0为地址信号输入端,Y 为数据输出端,ST 为使能端,又称选通端,输入低电平有效。

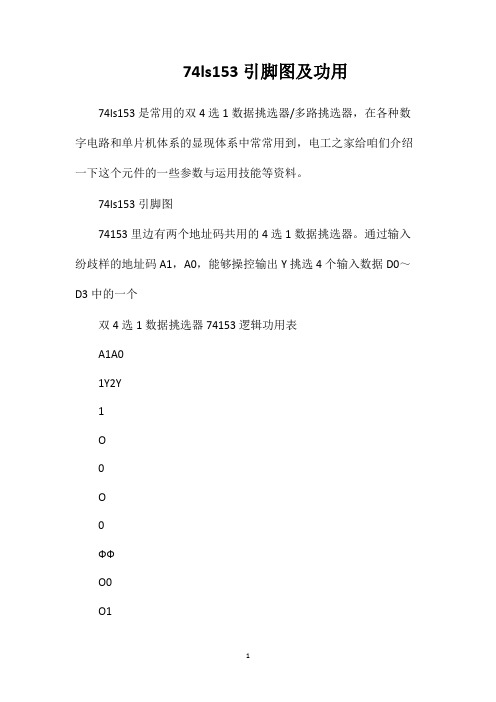

下图7.10为74LS153 管脚排列示意图。

该芯片中存在两个4选1数据选择器。

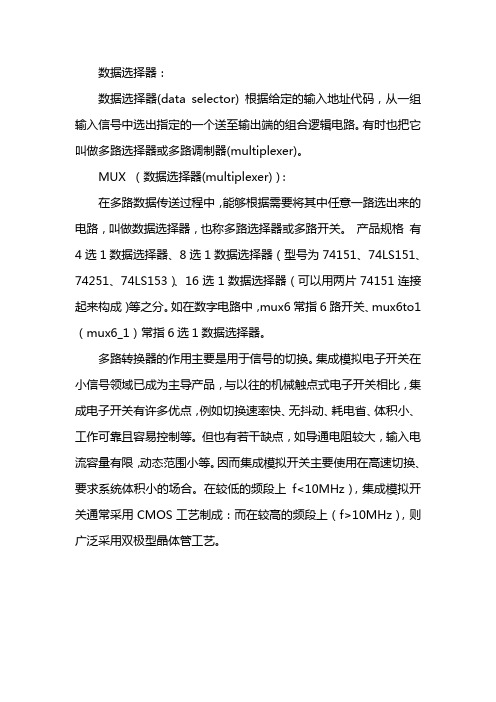

2Y92C0102C1112C2122C313A 14B 2~1G 11Y71C061C151C241C33~2G15图7.10 74LS153 管脚排列表7.5为74LS153的功能表。

当使能端G 有效时,输出等于地址信号A 、B 所选择的数据信号。

可得输出函数表达式为:3322110C m C m C m C m Y o +++=。

对于一个n 选1的数据选择器,其输出函数为:n n o C m C m Y ++=...0 二、用数据选择器实现组合逻辑函数实现原理:数据选择器是一个逻辑函数的最小项输出:∑-===++=1200...n i ii n n o c m C m C m Y 而任何一个n 位变量的逻辑函数都可变换为最小项之和的标准式。

对照函数表达式和相应的数据选择器输出函数表达式,可以实现用数据选择器来表示逻辑函数。

实现步骤:(1)根据函数变量选择合适的数据选择器,一般变量个数n 个,选择2n 选1的数据选择器。

(2)将被表示的函数转换成标准与或表达式。

(3)写出选择的数据选择器的输出函数。

(4)对比两函数,使数据选择器的地址端和函数变量一一对应(高位对高位),表达式中出现的最小项相应的输入数据C 为1,否则为0。

(5)画逻辑电路图。

例:用数据选择器和门电路实现AC AB Y +=的组合逻辑电路。

(1) 选择数据选择器:选8选1数据选择器74LS151。

(2) 标准与或表达式756m m m ABC C B A C AB AC AB Y '+'+'=++=+=' (3)写出数据选择器输出函数776655443322110C m C m C m C m C m C m C m C m Y o +++++++=(4)对照上述两表达式,令A=A2,B=A1,C=A0,则n n m m '=,所以,C 0=C 1=C 2=C 3=C 4=0;C 5=C 6=C 7=1。

四选一数据选择器

数据选择器:

数据选择器(data selector) 根据给定的输入地址代码,从一组输入信号中选出指定的一个送至输出端的组合逻辑电路。

有时也把它叫做多路选择器或多路调制器(multiplexer)。

MUX (数据选择器(multiplexer)):

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。

产品规格有4选1数据选择器、8选1数据选择器(型号为74151、74LS151、74251、74LS153)、16选1数据选择器(可以用两片74151连接起来构成)等之分。

如在数字电路中,mux6常指6路开关、mux6to1(mux6_1)常指6选1数据选择器。

多路转换器的作用主要是用于信号的切换。

集成模拟电子开关在小信号领域已成为主导产品,与以往的机械触点式电子开关相比,集成电子开关有许多优点,例如切换速率快、无抖动、耗电省、体积小、工作可靠且容易控制等。

但也有若干缺点,如导通电阻较大,输入电流容量有限,动态范围小等。

因而集成模拟开关主要使用在高速切换、要求系统体积小的场合。

在较低的频段上f<10MHz),集成模拟开关通常采用CMOS工艺制成:而在较高的频段上(f>10MHz),则广泛采用双极型晶体管工艺。

数电组合逻辑电路习题含答案)

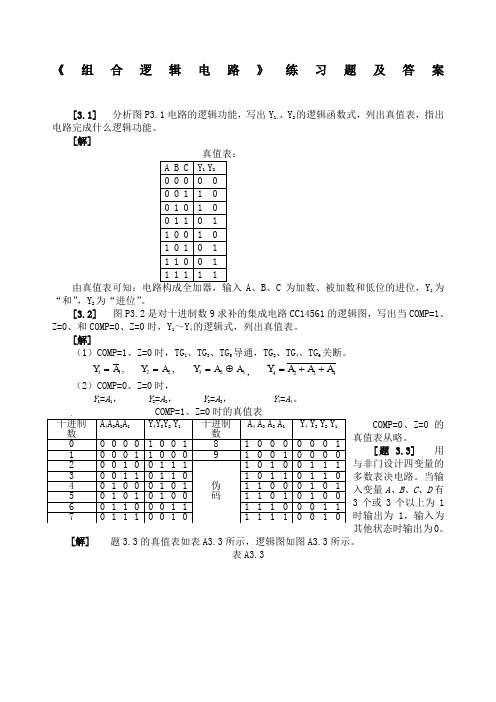

《组合逻辑电路》练习题及答案[3.1] 分析图P3.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]A 、B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[3.2] 图P3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++= (2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP=1、Z=0时的真值表 COMP=0、Z=0的真值表从略。

[题 3.3] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题3.3的真值表如表A3.3所示,逻辑图如图A3.3所示。

表A3.3[3.4] 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解] 题3.4的真值表如表A3.4所示。

真值表中的C B A 、C B A 、C B A 、C AB 为约束项,利用卡诺图图A3.4(a)化简后得到: C B A M S +=, B M L =(M S、M L的1状态表示工作,0状态表示停止)。

数字电子技术基础(第四版)课后习题答案_第三章

第3章[题3.1] 分析图P3.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]BCAC AB Y BCAC AB C B A ABC Y ++=+++++=21)(B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题3.2] 图P3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++=(2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP =0、Z=0的真值表从略。

[题3.3] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题3.3的真值表如表A3.3所示,逻辑图如图A3.3所示。

ABCD D ABC D C AB CD B A BCD A Y ++++= BCD ACD ABC ABC +++=B C D A C D A B D A B C ⋅⋅⋅=[题3.4] 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解] 题3.4的真值表如表A3.4所示。

组合逻辑电路 课后答案

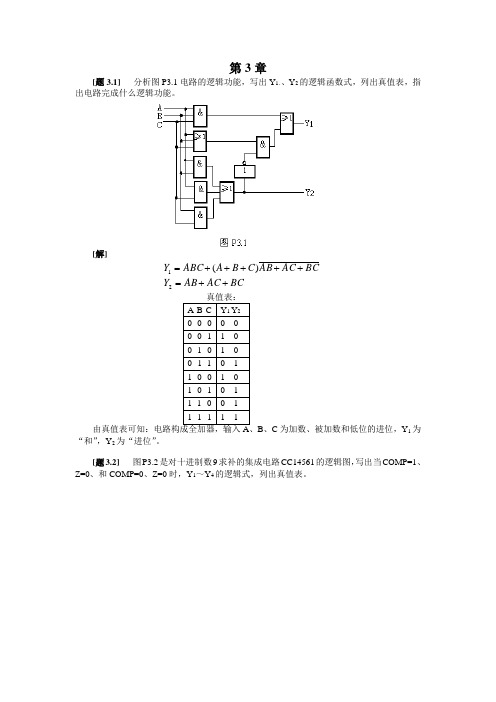

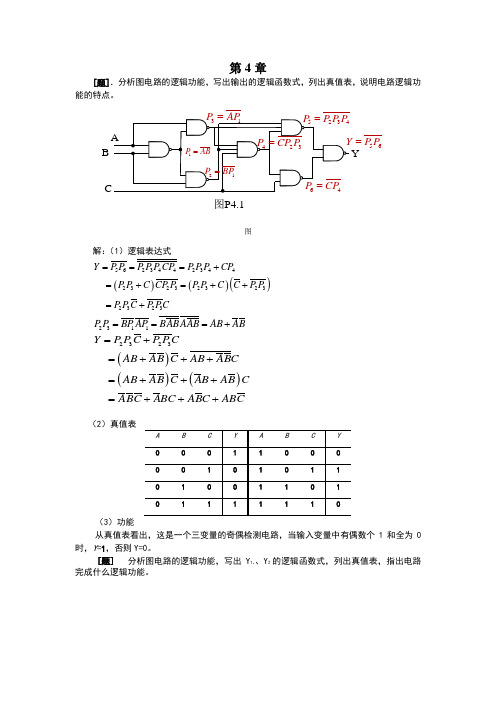

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] 用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题的真值表如表所示,逻辑图如图(b)所示。

74ls153引脚图及功用

74153里边有两个地址码共用的4选1数据挑选器。通过输入纷歧样的地址码A1,A0,能够操控输出Y挑选4个输入数据D0~D3中的一个

双4选1数据挑选器74153逻辑功用表

A1A0

1Y2Y

1

O

0

O

0

ФФ

O0

O1

2D20

1D112D21

1D122D22

1D132D23

74ls153引脚图及功用74ls153是常用的双4数据挑选器多路挑选器在各种数字电路和单片机体系的显现体系中常常用到电工之家给咱们介绍一下这个元件的一些参数与运用技能等资料

74ls153引脚图及功用

74ls153是常用的双4选1数据挑选器/多路挑选器,在各种数字电路和单片机体系的显现体系中常常用到,电工之家给咱们介绍一下这个元件的一些参数与运用技能等资料。

74ls153功用表

74ls153逻辑图

74ls153封装:

74LS系列IC管脚图大全

74LS390 双十进制计数器

74LS624 压控振荡器

74LS625 压控振荡器

74LS626 压控振荡器

74LS627 压控振荡器

74LS628 压控振荡器

74LS629 压控振荡器

两片74LS283构成的8位加法器

74LS289 64位随机存取存储器

74LS289 64位随机存取存储器

74LS290异步2—5—10进制计数器

74LS290异步2—5—10进制计数器

74LS292 可编程分频器/数字定时器

74LS293 4位二进制计数器

74LS294 16位可编程模块

74LS374 八D触发器(三态同相)

74381

符号

A0 A1 A2 A3

B0 B1 B2 B3

C -1

S0 S1 S2

引脚排列

A 1 1 20 VCC

F0

B1

A2

F1

A0

B2

F2

B0

F3

S0

A3 B3

7 43 81

S1

C -1

S2

P

P

F0

G

G

F1

F3

GND 1 0 1 1 F 2

74LS381算术逻辑单元

74LS181 算术逻辑单元/功能发生器

74LS181 四位算术逻辑运算器

7 4 18 2

G 1 1 16 V cc

P1

P2

G0

G2

P0

C -1

G3

C0

P3

C1

P

G

G ND 8 9 C 2

74LS182先行进位发生器/超前进位产生器

VCC 2Ai 2Bi 2Ci-1 2Ci 2Si VCC2A 2B 2CIn 2COn+1 2F 74LS183 1COn+1 1A 1B 1CIn 1F GND 1Ai 1Bi 1Ci-1 1Ci 1Si 地

[说明]数电数据选择器

![[说明]数电数据选择器](https://img.taocdn.com/s3/m/d3b61ced760bf78a6529647d27284b73f24236f9.png)

数据选择器一.实验目的1.熟悉中规模集成数据选择器的逻辑功能及测试方法。

2.学习用集成数据选择器进行逻辑设计。

二.实验原理数据选择器是常用的组合逻辑部件之一。

它由组合逻辑电路对数字信号进行控制来完成较复杂的逻辑功能。

它有若干个数据输入端0D 、1D 、…,若干个控制输入端0A 、1A 、…和一个输出端O Y 。

在控制输入端加上适当的信号,即可从多个输入数据源中将所需的数据信号选择出来,送到输出端。

使用时也可以在控制输入端上加上一组二进制编码程序的信号,使电路按要求输出一串信号,所以它也是一种可编程的逻辑部件。

中规模集成芯片74LS153为双四选一数据选择器,引脚排列如图7—1所示,其中0D ,1D ,2D ,3D 为四个数据输入端,Y 为输出端,0A ,1A 为控制输入端(或称地址端)同时控制两个四选一数据选择器的工作,G 为工作状态选择端(或称使能端)。

74LS153的逻辑功能如表7—1所示,当1)2(1==G G 时电路不工作,此时无论1A 、0A 处于什么状态,输出Y 总为零,即禁止所有数据输出,当0)2(1==G G 时,电路正常工作,被选择的数据送到输出端,如0101=A A ,则选中数据1D 输出。

图7—1 图7—2当G =0时,74LS153的逻辑表达式为31020__1101__00__1__D A A D A A D A A D A A Y +++=中规模集成芯片74LS151为八选一数据选择器,引脚排列如图7—2所示。

其中D 0—D 7为数据输入端,)(Y Y 为输出端,2A 、1A 、0A 为地址端,74LS151的逻辑功能如表7—2所示。

逻辑表达式为 701260__12501__240__1__23102__20__12__101__2__00__1__2__D A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A Y +++++++=数据选择器是一种通用性很强的中规模集成电路,除了能传递数据外,还可用它设计成数码比较器,变并行码为串行码及组成函数发生器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

双4选1数据选择器74LS153

所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。

其引脚排列及逻辑符号如下所示:

1G、2G为两个独立的使能端;B、A为

公用的地址输入端;1C0~1C3和2C0~2C3

分别为两个4选1数据选择器的数据输入端;

Y1、Y2为两个输出端。

①当使能端1G(2G)=1时,多路开关

被禁止,无输出,Y=0。

②当使能端1G(2G)=0时,多路开关

正常工作,根据地址码B、A的状态,将相

应的数据C0~C3送到输出端Y。

B A=00 则选择CO数据到输出端,即

Y=C0。

B A=01 则选择C1数据到输出端,即Y=

C1,其余类推。

其功能表如下:

选择输入数据输出选通输入输出

B A C0 C1 C2 C3 G Y

L L L ×××L L

××××××H L

L L H ×××L H

L H ×L ××L L

L H ×H ××L H

H L ××L ×L L

H L ××H ×L H

H H ×××L L L

H H ×××H L H。