Viterbi算法与实现

译码器得到了有最大路径度量的路径Viterbi算法R=10

卷积码的逐比特概率译码—— BCJR译码

y y1N ( y1 , y2, yk ,, yN )

yk

(

y

s k

,

y

p k

)

Le (uk ) 是关于uk的先验信息, 是关于uk的对数似然比。

Le (uk )

ln

P(uk P(uk

1) 0)

L(uk

)

ln

P(uk P(uk

p(s, yk |s' )

p(

y

N k 1

|

s)

k1(s' ) k (s' , s) k (s)

k (s) p(Sk s, y1k ) 为前向递推

k (s)

p(

y

N k 1

|

S

k

s) 为后向递推

k (s' , s) p(Sk s, yk |Sk1 s' )为s’和s之间的分支转移概率

Viterbi算法

01 00 10 01

11

2 d M’ 2 (00) 2 (01)

1 (10)

3 (11)

Viterbi算法

R=10, 10, 00

01 00 10 01

11

2

3 d M’

2 (000)

1 (101)

3 (010)

3 (011)

Viterbi算法

R=10, 10, 00, 01

p(Sk

s,

y

N k

| Sk 1

s' )

p(

y

N k 1

|

S

GMSK信号的维特比算法与FPGA实现

GMSK信号的维特比算法与FPGA实现康超;陈丽婷;陈建斌【摘要】GMSK信号与FSK信号相比具有更高的频带利用率,在遥测通信领域得到了广泛应用.因GMSK的基带信号经过高斯滤波整形,相当于加入了码间干扰导致接收灵敏度下降.采用基于最佳似然准则(MLSE)的维特比(Viterbi)算法实现GMSK信号的解调.针对所需匹配滤波器消耗过多FPGA硬件资源问题提出了优化方法,将匹配滤波器数量从256个降至64个.针对路径度量LS值发散导致FPGA无法实现问题进行了分析并提出了解决方法,使LS收敛在460附近.实测结果表明,FPGA实现后充分发挥了Viterbi算法的最佳译码性能,接收灵敏度与未采用多符号检测技术(MSD)的FSK信号相比提升了3 dB.【期刊名称】《无线电工程》【年(卷),期】2018(048)007【总页数】5页(P541-545)【关键词】最佳似然准则;维特比;GMSK;FSK;FPGA【作者】康超;陈丽婷;陈建斌【作者单位】上海航天电子技术研究所, 上海 201109;上海航天电子技术研究所, 上海 201109;上海航天电子技术研究所, 上海 201109【正文语种】中文【中图分类】TN9110 引言GMSK信号[1]的调制指数为0.5,相位连续,可以理解为一种特殊的FSK信号。

GMSK的基带信号经高斯滤波后提高了频带利用率但同时也引入了码间干扰。

本文采用通用数字环+Viterbi算法完成GMSK信号的相干解调。

文献[2-4]指出,存在码间干扰时使用最佳似然准则(MLSE)可以达到最佳译码性能,通常选择用Viterbi算法[5]实现GMSK信号解调来提升接收灵敏度。

Viterbi算法对载波环的相位误差要求较高,本文通过Matlab仿真得出相位误差要求控制在6°。

文献[6-8]分析了GMSK相干解调载波同步的方法和性能,文献[9]的通用数字环是一种适于数字化处理的低运算量锁相环,性能可以满足Viterbi算法的要求。

一种高速Viterbi译码器的设计与实现

第30卷 第5期2007年10月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.5Oct.2007Design and Implementation o f a High Speed Viter bi DecoderL I Ga n g ,H E I Y o ng ,Q IAO Sh u 2s ha n ,Q IU Yu 2l i n(Inst it ute of Microelect roni cs of Chi nese Aca demy of Sciences ,B ei j i ng 100029,Chi na)Abstract :Vit erbi decoding algorit hm is an opti mal decoding al gori t hm for co nvol utional code.A hi gh speed (3,1,7)Vit erbi decoder ,which incl ude s B MU ,A CSU ,SMU a nd CU ,i s designed a nd i mple ment ed.The Vit erbi decoder i s impl ement ed and verified in St rat ix II FP GA.The verificat ion resul t s show t hat t he dat a t hroughput of t he Vit erbi decoder is 231Mbit /s and t he Bit Error Rat e (B ER )is close to t hat of t heory si mula tion re sult in AW GN pared to ot her Vi terbi decoders ,t he propo sed Vit erbi decoder has hi gher speed and lower ha rdware impl eme nt ation co st.K ey w or ds :Vit erbi decoder ;hi gh speed design ;FP GA ;A WGN EEACC :6120B一种高速Viter bi 译码器的设计与实现李 刚,黑 勇,乔树山,仇玉林(中国科学院微电子研究所,北京100029)收稿日期:2006211215作者简介:李 刚(19772),男,博士研究生,目前从事信道编解码、低功耗数字基带芯片的设计研究,ligang @ ;黑 勇(2),男,研究员,主要从事可重构数字信号处理器,低功耗数字基带芯片的设计研究;乔树山(82),男,博士研究生,目前从事低功耗数字基带芯片的设计研究;仇玉林(2),男,研究员,博士生导师,主要从事深亚微米VLSI 集成电路高性能和低功耗设计研究摘 要:Vite rbi 算法是卷积码的最优译码算法.设计并实现了一种高速(3,1,7)Vite rbi 译码器,该译码器由分支度量单元(BMU)、加比选单元(ACSU)、幸存路径存储单元(SMU)、控制单元(CU)组成.在St ratix II FP G A 上实现、验证了该Viter bi译码器.验证结果表明,该译码器数据吞吐率达到231Mbit/s ,在加性高斯白噪声(AWGN )信道下的误码率十分接近理论仿真值.与同类型Vite rbi 译码器比较,该译码器具有高速、硬件实现代价低的特点.关键词:Viter bi 译码器;高速设计;FP G A ;AWG N中图分类号:TN 492 文献标识码:A 文章编号:100529490(2007)0521886204 在无线通信系统中,为了提高通信性能,需要采用信道编码技术.它使传输信号能够更好地抵抗各种信道噪声、干扰以及衰落的影响,以一定程度的冗余代价降低了通信系统的误码率.卷积码性能较高、实现复杂度适中、实时性好,因此得到了广泛应用.在数字视频广播(DVB)、数字音频广播(DA B)、卫星通信、无线局域网(WLAN)、超宽带(UWB)、3G 等技术领域都采用了卷积码.卷积码的编码实现比较简单,相关的研究主要集中在译码算法和硬件实现上.与其它卷积码的译码算法相比,Viterbi 算法采用最大似然译码(MLD )准则,是一种最优算法.目前,无线通信对通信速率提出越来越高的要求,如MB 2O FDM UWB 系统最高工作速率为480Mbit /s ,相应的卷积码编码器、译码器也需要工作在这样高的速率下.同时,U WB 、WL AN 等模块属于无线附属设备,其成本和功耗的要求需要尽可能降低实现的复杂度.因此,本文提出了一种高速、低复杂度的Vit erbi 译码器的设计.1 原理1.1 卷积码卷积码常用(n ,k ,N )表示,k 个信息元输入对19741911942.应n个码元的输出,码率R=k/n衡量编码的效率, N称为约束长度.卷积码的一个重要特征就是编码的记忆性,即编码产生的n元组不仅是k元组的函数,而且还是前面N-1个k元组的函数.本文使用码率R=1/3,约束长度N=7的(3,1,7)卷积码,其编码生成多项式可以表示为g1=1338,g2=1658, g3=1718,1.2 V iter bi算法Vit erbi算法是一种最大似然译码,它利用了编码网格图(Trellis)的特殊结构,从而降低了计算的复杂性[1].在网格图上,该算法计算t时刻到达各个状态的路径和接收序列之间的距离,去除掉不可能成为最大似然选择对象的路径.如果有两条路径到达同一状态,则具有最小度量的路径被选中,称为幸存路径.对所有状态都将进行这样的选择操作,译码器不断在网格图上深入,通过去除可能性最小的路径实现判决.较早地舍弃不可能的路径降低了译码的复杂度.Vit erbi译码器的结构如图1所示,包括分支度量单元(B MU)、加比选单元(A CSU)、幸存路径存储单元(SMU)、控制单元(CU).图1 Viterbi译码器的结构2 高速Viter bi译码器设计2.1 分支度量单元(BM U)BMU计算到达各个状态的期望发送序列和接收序列之间的距离,这个距离反映了所有可能的传输码字的后验概率.有两种常用距离判决方法:基于汉明距离的硬判决、基于欧几里德距离的软判决.在硬判决中,经过解调器(如QP SK解调器)量化得到的接收数据仅用1bit表示一个码符号,而软判决用多个比特表示一个码符号.与无限比特量化方式相比,硬判决有2dB的译码增益损失,3bi t的软判决仅有0.25dB 的译码增益损失.而大于3bit的量化方式与3bit 的量化方式相比只能带来很小的性能提升.所以本设计选用3bit量化值的软判决.欧几里德距离的计算如下式[]=∑=()()这里r i是送至译码器的3bit接收符号,c i是期望被传输码字.如果直接使用该公式进行软判决,硬件实现复杂度较高.本设计采用汉明距离进行软判决,降低了硬件实现的复杂度,提高了工作速度,而且对性能的影响不大.由于码率R=1/3,译码器共有3个数据输入端,每次分别收到3bit数据.网格图上的c i的值0和1分别用000和111来表示,然后分别计算得到其汉明距离.2.2 加比选单元(ACS U)2.2.1 结构设计Vi ter bi算法根据最大似然估计准则,在网格图上选择接收距离最短的一条路径作为结果输出,而这部分核心功能就是由ACSU完成的.在图2中给出网格图中的一个子网格图,它描述了(t-1)时刻的两个状态到t时刻发生状态变化的规律,这样的子网格图共有2N-2个.根据输入的不同,这两个状态转换到下一时刻的两个状态之一.在t时刻的状态S的状态路径度量是:PM p utt=min(PM0t-1+B M0t-1,PM1t-1+B M1t-1)(2)图3给出了一个ACSU块的实现结构.在t时刻,ACSU分别计算得到两个t-1时刻的路径度量值(PM0,PM1)与相应分支度量值(BM0,B M1)的和,然后比较并选择其中小的值作为本时刻的路径度量值(PM out)输出,而比较结果作为判决比特输出到SMU.图2 子网格图 图3 一个ACSU块的实现结构ACSU的非线性反馈环是影响Vi ter bi译码器工作速率的瓶颈.基于速率与硬件实现成本的权衡,实现结构有:串行结构、部分并行结构、全并行结构.出于高速设计的考虑,本设计选用了全并行结构,即每个状态都对应一个ACSU块,一共需要2N-1=64个ACSU块.基4算法是一种提高Vit erbi译码器数据吞吐率的有效算法[2].在网格图中,基4算法合并基2算法两次状态转换为一步在理论上,实现复杂度提高了一倍,V译码器的数据吞吐率也提高了一倍但是,硬件实现中并非如此,其硬件复杂度提高了一倍,7881第5期李 刚,黑 勇等:一种高速Vit erbi译码器的设计与实现1:d2Eni1r i-c i21.iterbi.译码器吞吐率却不会提高一倍.尤其是在网格图状态数较大时,由于各个ACSU块之间的连接关系的复杂性带来了硬件实现时连线延迟很大,影响了基4算法的吞吐率.所以,本设计选用了基2算法.2.2.2 位宽设计在A CSU块中,路径度量值的精度影响到整个Vit erbi译码器的性能.高精度需要高的数据位宽,但是会消耗更多的硬件资源.反之,降低位宽能节省硬件资源,但是可能会降低译码器性能.所以需要设计合理的位宽,在性能与实现复杂度之间进行权衡.位宽选择依据如下公式[2]:PM bits=[log2(r max+k BM max)]+1(3)其中:BM max:分支度量的最大值,r max:路径度量之差的最大值k:基2k算法本设计中:BM max=21,r max=126,k=1,所以需要9bi t的位宽.2.2.3 溢出控制在Vit erbi译码过程中,随着网格图的推进,每个状态不断累加的路径度量值也不断增大.对于给定的有限字长的位宽,当路径度量值大于该位宽所能表示的最大数值时,就会发生溢出.有两种常用的溢出控制方法:一种是每次找到幸存路径度量的最小值,然后将每个幸存路径度量减去这个最小值.另一种是定义一个幸存路径度量值的门限值,当有一个幸存路径度量大于这个门限值时,在下一时刻,所有的幸存路径度量都减去这个门限值.本设计使用了不同的溢出控制方法.在译码中,设置一个门限值为384,当路径度量值大于384(即110000000b)后,将所有路径度量值的最高位置0,即相当减去了256.由于未使用减法器,硬件开销更小,工作频率更高.2.3 幸存路径存储单元(SMU)SMU根据ACSU的判决比特不断更新SMU 中的幸存路径,并选择其中一个状态的幸存路径输出,就是译码结果.有两种经典的SMU实现算法:回溯算法(TB:Trace Back)、寄存器交换算法(R E: Regi st er Exchange).TB算法将判决比特存储在RAM中,在一定时间后,按照所存储的判决比特顺着网格图开始向回搜索出一条译码路径,并输出译码结果随着回溯的进行,各个状态的幸存路径开始结合,并最终结合于一条幸存路径根据某一状态向前回溯L时刻,会回到相同的状态点,L称为回溯深度,L的大小通常选定为5~10倍的约束长度N.比较高效的TB算法有三种[3]:k2pointer Even算法、k2poi nt er Odd算法和one2pointer算法.R E算法根据判决比特不断交换更新SMU中的幸存路径.其实现结构图如图4所示,这里有2N-1个长度为L的移位寄存器,每个都对应网格图中一个状态.寄存器交换就是将某一旧状态的幸存路径拷贝到当前状态所对应的寄存器中,再加上前面的跳转路径就是当前状态的幸存路径.图中多路开关根据判决比特的值,交换拷贝对应的幸存路径.当存储的数据深度大于回溯深度L时,可以进行译码输出.图4 R E算法实现结构图TB算法没有路径交换,它依靠路径回溯单元来译码,在一定的实现复杂度下,具有较低的功耗.缺点是对RAM的地址操作较复杂,译码吞吐率较低,输出延时较大.在高速Vit erbi译码器中,采用TB算法的SMU单元会成为关键路径.R E算法采用寄存器实现,而且连线关系规则、控制简单,速度快、输出延迟小,而且实现所需硬件资源较小.缺点是每次状态更新,寄存器都要翻转,在状态数多、回溯深度大的情况下,功耗相对较高.这里,出于高速设计和低复杂度的考虑,根据了R E算法设计了SMU,并选择回溯深度L=6×N=42.3 F P GA实现与验证该Vite rbi译码器采用Ve rilog HDL语言编写代码,使用Quart us5.1综合、布线,并在AL TERA 公司的St rat ix II FP GA上完成验证.表1是实现结果,以及该译码器与3种最新高速Vite rbi译码器的比较在回溯深度L=的条件下,本文设计的V译码器最高数据吞吐率达到3M,使用了个LU T8881电 子 器 件第30卷. ..42iter b i21bit/s 4490A s.表1 本设计Viter bi译码器与其它高速V iter bi译码器的比较比较项目本设计Altera IP核[4]文献[5]文献[6]卷积码特性(3,1,7)(2,1,7)(3,1,7)(3,1,7)实现结构细节全并行,基2,R E全并行,基2,TB全并行,基2,R E全并行,基4,TB 回溯深度(L)42425442F PG A型号Alter a Stratix IIEP2S15F484C3Altera St ratix IIEP2S15F484C3Xilinx x2v6000Ff1152-5Xilinx Virtex-II6000-6硬件资源14490ALU Ts(2681regi ster s)3224AL U Ts2个M512,9个M4K5859Slice s5110Slices(5675register s)最高工作频率/M Hz23123122092.5最高吞吐率/Mbit/s2312312201851:slice s是X ilinx F P G A的逻辑单元,每个slices包括两个可编程4输入LU T、两个触发器.M512及M4K是Altera FP G A内嵌存储器,容量分别为512、4k. 从表1的比较可以看出:(1)本设计数据吞吐率与Alte ra IP核相同,使用的ALU T比后者多,而后者使用了多块内部存储器.由于采用了(3,1,7)卷积码,前者误码率性能优于后者的(2,1,7)卷积码.(2)与文献[5]相比,本设计数据吞吐率略高、硬件资源略少,但前者的回溯深度为54.(3)与采用基4算法的文献[6]相比,本设计数据吞吐率高,节省了大量硬件资源.可见基2算法很适合高速、约束长度长的卷积码译码.为了验证所设计Vi ter bi译码器的性能,对硬件实现结果进行了误码率测试.用于测试的随机测试向量长度为107,调制采用Q PS K,信道为加性高斯白噪声(AW G N).在同样回溯深度下,采用Mont e Carlo方法仿真分析了(3,1,7)码Vi ter bi译码器的理论浮点性能.这两个仿真结果如图5所示.对比可以发现,本设计译码器的硬件实现性能与理论性能仅有很小的差距.图5 Viter bi译码器的误码率4 结论本文设计了一种高速、低复杂度的Vi ter bi译码器,在St rati x II FP GA上实现、验证了该Vit erbi译码器.验证结果表明,该译码器数据吞吐率达到231 Mbit/s,在加性高斯白噪声(A W G N)信道下的误码率十分接近理论仿真值.与同类型Vite rbi译码器比较,该译码器具有高速、硬件实现成本低的特点.该译码器可以直接应用到高速无线通信系统的基带ASIC芯片设计中.参考文献:[1] 王新梅,肖国镇.纠错码-原理与方法[M].西安电子科技大学出版社.2001.[2] Black P J.A1402Mb/s,322St at e,Radi x24Vit erbi Deco der[J].IEEE Jo urnal of S oli d2Stat e Circui t s,December,1992,27(12):187721992.[3] Feygi n G and Gulak P G.Archit ect ure Tradeoffs for Survi vor Se2quence Mem ory Managem ent in Viterbi Decoders[J].IEEE T rans2 actions on Communicat i o ns,March1993,41(3):4252429.[4] www.al t era.co m,“MegaCore:Vit er bi C o m pi ler User G ui de”,Versio n4.4.0,Ap ri l2006,pp.15.[5] Haene S,Bu rg A and Per rl s D.FP GA Implement at ion of Vit2erbi Decoders for M IMO2B IC M[C]//Thirt y2Ni nt h Asilo m ar co nference on Signal,Syst em and C o mput ers,2005:7342738.[6] Sung Woo Choi and Sang su ng Choi.200M bi t/s Vit erbi decod2er for UWB[C]//ICAC T2005:9042907.9881第5期李 刚,黑 勇等:一种高速Vit erbi译码器的设计与实现。

通过Viterbi译码算法实现译码器优化实现方案

通过Viterbi译码算法实现译码器优化实现方案

1 引言

由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。

卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。

从工程应用角度看,对Viterbi译码器的性能*价指标主要有译码速度、处理时延和资源占用等。

本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。

测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。

2 卷积编码网格图特点

图1所示为卷积编码网格图结构,图中每一状态有两条输入支路和两条输出支路。

2.1 输入支路的特点

任意一个状态节点Si都有两条输入支路,且这两条输入支路对应的源节点分别为:

此外,i为偶数时,两条输入支路的输入信息都为‘1’;i为奇数时,两条输入支路的输入信息都为‘0’。

2.2 输出支路的特点

任意一个状态节点Si都有两条输出支路,且两条输出支路对应的目的节点分别为:

此外,目的节点是Sj1的输出支路对应的输入信息都为‘0’;目的节点是Sj2的输出支路对应的输入信息都为‘1’。

3 Viterbi译码器的优化算法

3.1 判决信息比特与路径信息向量同步存储算法。

维特比算法(Viterbi)及python实现样例

维特⽐算法(Viterbi)及python实现样例维特⽐算法(Viterbi)维特⽐算法维特⽐算法shiyizhong 动态规划算法⽤于最可能产⽣观测时间序列的-维特⽐路径-隐含状态序列,特别是在马尔可夫信息源上下⽂和隐马尔科夫模型中。

术语“维特⽐路径”和“维特⽐算法”也被⽤于寻找观察结果最有可能解释的相关dongtai 规划算法。

例如在统计句法分析中动态规划可以被⽤于发现最有可能的上下⽂⽆关的派⽣的字符串,有时被称为“维特⽐分析”。

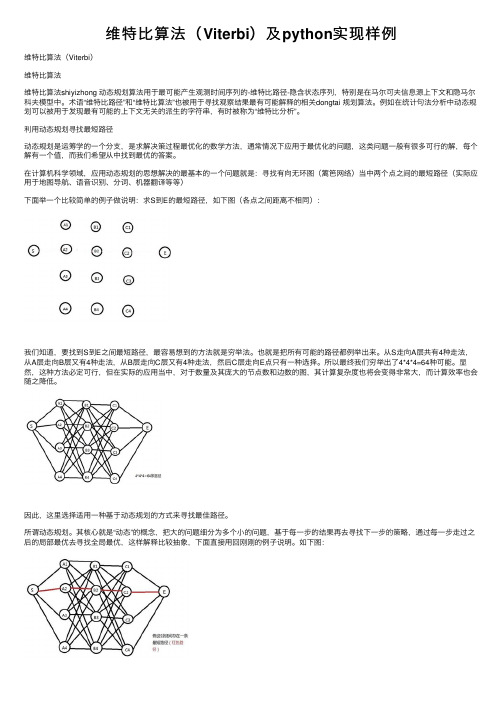

利⽤动态规划寻找最短路径动态规划是运筹学的⼀个分⽀,是求解决策过程最优化的数学⽅法,通常情况下应⽤于最优化的问题,这类问题⼀般有很多可⾏的解,每个解有⼀个值,⽽我们希望从中找到最优的答案。

在计算机科学领域,应⽤动态规划的思想解决的最基本的⼀个问题就是:寻找有向⽆环图(篱笆⽹络)当中两个点之间的最短路径(实际应⽤于地图导航、语⾳识别、分词、机器翻译等等)下⾯举⼀个⽐较简单的例⼦做说明:求S到E的最短路径,如下图(各点之间距离不相同):我们知道,要找到S到E之间最短路径,最容易想到的⽅法就是穷举法。

也就是把所有可能的路径都例举出来。

从S⾛向A层共有4种⾛法,从A层⾛向B层⼜有4种⾛法,从B层⾛向C层⼜有4种⾛法,然后C层⾛向E点只有⼀种选择。

所以最终我们穷举出了4*4*4=64种可能。

显然,这种⽅法必定可⾏,但在实际的应⽤当中,对于数量及其庞⼤的节点数和边数的图,其计算复杂度也将会变得⾮常⼤,⽽计算效率也会随之降低。

因此,这⾥选择适⽤⼀种基于动态规划的⽅式来寻找最佳路径。

所谓动态规划。

其核⼼就是“动态”的概念,把⼤的问题细分为多个⼩的问题,基于每⼀步的结果再去寻找下⼀步的策略,通过每⼀步⾛过之后的局部最优去寻找全局最优,这样解释⽐较抽象,下⾯直接⽤回刚刚的例⼦说明。

如下图:⾸先,我们假设S到E之间存在⼀条最短路径(红⾊),且这条路径经过C2点,那么我们便⼀定能够确定从S到C2的64条(4*4*4=64)⼦路经当中,该⼦路经⼀定最短。

Viterbi译码的Matlab实现

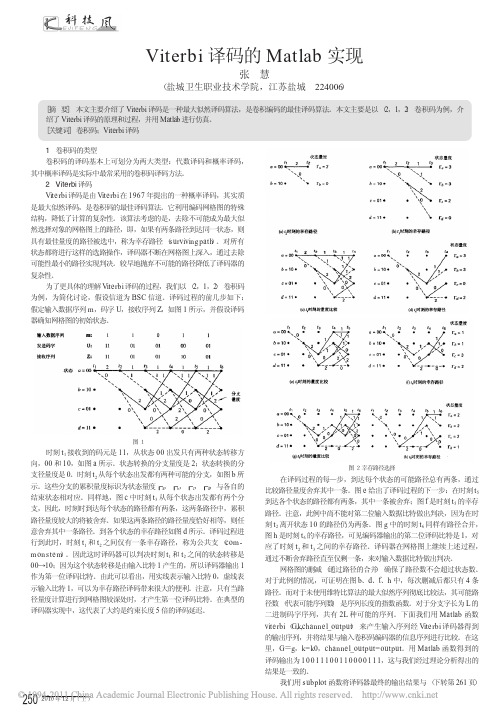

2010年12月(上)Viterbi 译码的Matlab 实现张慧(盐城卫生职业技术学院,江苏盐城224006)[摘要]本文主要介绍了Viterbi 译码是一种最大似然译码算法,是卷积编码的最佳译码算法。

本文主要是以(2,1,2)卷积码为例,介绍了Viterbi 译码的原理和过程,并用Matlab 进行仿真。

[关键词]卷积码;Viterbi 译码1卷积码的类型卷积码的译码基本上可划分为两大类型:代数译码和概率译码,其中概率译码是实际中最常采用的卷积码译码方法。

2Viterbi 译码Viterbi 译码是由Viterbi 在1967年提出的一种概率译码,其实质是最大似然译码,是卷积码的最佳译码算法。

它利用编码网格图的特殊结构,降低了计算的复杂性。

该算法考虑的是,去除不可能成为最大似然选择对象的网格图上的路径,即,如果有两条路径到达同一状态,则具有最佳量度的路径被选中,称为幸存路径(surviving path )。

对所有状态都将进行这样的选路操作,译码器不断在网格图上深入,通过去除可能性最小的路径实现判决。

较早地抛弃不可能的路径降低了译码器的复杂性。

为了更具体的理解Viterbi 译码的过程,我们以(2,1,2)卷积码为例,为简化讨论,假设信道为BSC 信道。

译码过程的前几步如下:假定输入数据序列m ,码字U ,接收序列Z ,如图1所示,并假设译码器确知网格图的初始状态。

图1时刻t 1接收到的码元是11,从状态00出发只有两种状态转移方向,00和10,如图a 所示。

状态转换的分支量度是2;状态转换的分支径量度是0。

时刻t 2从每个状态出发都有两种可能的分支,如图b 所示。

这些分支的累积量度标识为状态量度┎a ,┎b ,┎c ,┎d ,与各自的结束状态相对应。

同样地,图c 中时刻t 3从每个状态出发都有两个分支,因此,时刻时到达每个状态的路径都有两条,这两条路径中,累积路径量度较大的将被舍弃。

如果这两条路径的路径量度恰好相等,则任意舍弃其中一条路径。

列表 Viterbi 译码算法及其应用

List Viterbi Decoding Algorithm and Its Application

15

HAO Fangfang, NIU Kai

(Beijing University of Posts and Telecommunications, College of Information and

PLVA 中很多不必要的计算。本论文采用通过求两个序列度量差来确定最佳序列的方法[5]。 90 该算法的主要思想是第二条最佳路径肯定是与第一条最佳路径在某些时刻离开,然后又在后

面某一时刻汇入最佳路径。如图 3 所示。在 t0 时刻可能次佳路径离开最佳路径,又在 t1 时

刻汇合,之后再也没有离开过。不可能出现次佳路径与最佳路径再次重合两次的情况。因此

concatenated system that uses Cyclical Redundancy Check(CRC) as the outer encoder and 25 convolutional code as the inner encoder is considered. The system's performances using VA and

校验正确,否则超过最佳路径数量 L 时报错。很明显这样误帧率就会降低很多。

本论文的结构如下:第一章介绍列表 Viterbi 译码算法,第二章对并行 LVA 和串行 LVA 的算法复杂度进行分析和比较,第三章结合 CRC 校验给出级联码仿真结果并对结果进行相 应分析,第四章对论文进行总结。

50

图 1 级联码系统框架

t0

t1

图 3 第二条最佳路径的产生

120

图 4 第三条最佳路径的产生

2 算法复杂度分析

从FPGA实现的角度对大约束度Viterbi译码器

从FPGA实现的角度对大约束度Viterbi译码器1 引言Viterbi译码算法是一种最大似然译码算法,目前广泛应用于各种数据传输系统,特别是卫星通信和移动通信系统中。

近年来随着FPGA技术的迅速发展,使得基于FPGA实现Viterbi译码的算法成为研究的热点。

由于Viterbi译码器的复杂性随约束长度k成指数增加,大约束度不但使Viterbi译码器硬件复杂度大为增加,同时也限制了译码速度。

而其中以加比选(Add Compareselect,ACS)运算为最主要的瓶颈,的递归运算使流水线结构的应用变得困难。

本文以(2,1,9)卷积码为例,用FPGA实现大约束度Viterbi译码器,其中ACS设计采用串并结合的方法来兼顾面积和速度,并用流水线结构来提高译码速度,对路径度量存储则采用同址存储方法,实现了在占用少量硬件资源的前提下,提高译码速度。

2 算法简述及系统结构分析Viterbi译码原理详见文献[1,2],下面仅作简要说明。

图1为(2,1,9)卷积码的2个状态之间的状态转移图。

根据输入路径的不同(图中实线表示输入为0,虚线表示输入为1),仅仅首位不同的两个状态可转移到仅仅末位不同的两个状态。

将所有状态的状态转移图按时间往前衍生,即可得到(2,1,9)卷积码的网格(Trellis)图。

Viterbi译码过程就是:根据接收序列,按照最大似然法则,分段地在网格图上计算寻找有最大度量的路径的过程。

一般来说,维特比泽码器主要有4个单元所组成,其结构框图如图2所示。

分支度量单元(BMU) 主要是计算分支度量值。

所谓分支度量值就是码字与接收码之间的距离。

加-比较-选择单元(ACSU) 主要是做路径度量值与分支度量值的叠加,并决定幸存路径度量值及决定位元(decision bit)。

路径度量存储单元(PMMU) 主要用来存储幸存路径度量值。

幸存路径存储单元(SMU) 主要用来存储决定位元。

如图2所示,接收序列先通过分支度量单元计算出各状态所有分支度量,然后经过ACS单元,将上一时刻的路径度量值与当前时刻的分支度量值作加-比较-选择等运算,计算出当前时刻的幸存路径和路径度量值,并找出决定位元(decision bit),把新的路径度量值存储到路径度量存储单元(PMMU),并把相应的幸存路径的决定位元(de-cision bit)存储到幸存路径存储单元(SMU),当译码到译码深度后,判决输出单元输出译码序列。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Viterbi算法Viterbi算法是一种动态规划算法,用来寻找由观测信息产生(Observed Event)的最可能隐状态序列(Viterbi路径),这种方法通常用在隐马尔可夫模型中。

向前算法是一个类似的算法,用来计算一串观测事件发生的概率。

这些算法都属于信息论的范畴。

这个算法做一连串的假设。

首先,观测事件和隐事件必须处于序列中。

这个序列通常是关于时间的。

第二,这两个序列需要对应,一个观测事件的实例必须与一个隐事件相关联。

第三,计算在特定时间点t的最可能隐序列必须只依赖于位于t的观测事件,和t-1处的最可能序列。

这些假设在一阶隐马尔可夫模型中都要被满足。

Viterbi路径和Viterbi算法同时遵循寻找单一最可能观测解释的相关动态规划算法。

例如,在统计分析中的动态规划算法能应用于寻找一个字符串的单个最相似上下文无关推导,即“Viterbi推导”。

Viterbi算法是由Andrew Viterbi 在1967年提出的,是一种用于有噪声的数据链路中错误纠正的模型,并广泛应用在卷积码的解码中,例如CDMA/GSM数字蜂窝,拨号调制解调器,卫星通信,深空通信和802.11无线局域网等。

现在也广泛的应用在语言理解,关键词匹配,计算机语言学,生物信息学等。

例如,在语音理解中,听觉信号被认为是观测事件的序列,文字串被认为是“潜在的原因”。

Viterbi算法能够找到对应听觉信号的最可能文字序列。

概要前面提到的假设可以被如下概括。

Viterbi算法在一个状态机的假设上做操作。

也就是说,在任何时间系统被抽象为一些状态。

这些状态是有限的,尽管很大。

每个状态被表示为一个节点。

多个状态的序列(路径)往往都能产生同一个给定的状态,但其中只有一条是最可能产生这个状态的,被称作“生存路径”。

这是一个最基础的假设,因为这个算法会检测所有的可能路径并只保留一个最可能的路径。

这种策略并不需要计算所有的路径,只需要一个状态一个路径而已。

第二个关键的假设是前一个状态到一个新状态的转移被一个递增的度量描述,通常是一个数字。

这种转移是从实践中计算而来的。

第三个假设是事件在一个路径上是累加的。

所以整个算法的关键是计算每个状态的数值。

当发生了一个事件,算法结合上一个可能状态与转换产生的增量度量,并从中选择一个最优的,据此来检测向前的新状态。

增量度量由事件触发,并由旧状态与新状态间的转换决定。

例如,在数据交换中,可能发生一半的符号由奇状态转换,而另一半由偶状态开始转换。

同时,在很多例子中,状态转换图是不连续的。

一个简单的例子,一个汽车有三个状态,向前,停止和向后,状态从向前倒向后是不允许的。

他必须先进入停止状态。

在计算出增量度量和和状态度量后,只有最好的幸存,而其他的被舍弃。

这种基础算法有一个改进,允许向前搜索和向后搜索。

路径历史必须被储存。

在一些实例中,搜索历史是完整的,因为状态机在编码端是从一个已知的状态开始的,而且有充足的空间来维持这些路径。

再另一些例子中,需要一个在资源有限条件下的解决方案:一个例子是卷积编码,解码器必须在性能能允许的前提下尽量缩短对历史的记录。

尽管Viterbi算法是非常高效的,而且有很多降低计算压力的改进,但它对空间的要求仍然趋向常量。

实现Alice知道Bob三天来的活动,第一天出去散步,第二天去购物,第三天清洁了公寓。

Alice有两个问题:观测序列的整体概率是什么样的?这几天的天气是什么,最能给出观测序列这样的结果。

第一个问题由向前算法计算;第二个问题由Viterbi算法计算。

这两个算法在结构上是相似的,事实上,他们是同一种抽象算法的两个不同实例,所以他们可以在一个函数中实现。

def forward_viterbi(obs, states, start_p, trans_p, emit_p):T = {}for state in states:## prob. V. path V. prob.T[state] = (start_p[state], [state], start_p[state])for output in obs:U = {}for next_state in states:total = 0argmax = Nonevalmax = 0for source_state in states:(prob, v_path, v_prob) = T[source_state]p = emit_p[source_state][output] *trans_p[source_state][next_state]prob *= pv_prob *= ptotal += probif v_prob > valmax:argmax = v_path + [next_state]valmax = v_probU[next_state] = (total, argmax, valmax)T = U## apply sum/max to the final states:total = 0argmax = Nonevalmax = 0for state in states:(prob, v_path, v_prob) = T[state]total += probif v_prob > valmax:argmax = v_pathvalmax = v_probreturn (total, argmax, valmax)函数“forward_viterbi”需要如下几个输入参数,“obs”是观测序列,比如[`walk`,`shop`,`clean`];“states”是隐状态的集合;“start_p”是初始的概率,“trans_p”是转移概率;“emit_p”是产生概率。

这个算法在位图T和U上做操作,每个都是一个从一个状态到一个三元组(prob,v_path,v_prob)的映射,其中prob表示从开始到现在这个状态的概率之和;v_path是到当前状态的Viterbi路径,v_prob是到当前状态的Viterbi路径的概率。

位图T保存保存一个给定时间点t的信息,主循环结构U,保存t+1的相似信息。

因为马尔可夫性,任何早于时间t的信息是不需要的。

算法初始化T为开始的概率:一个状态的总概率是这个状态开始的概率;到一个开始状态的Viterbi路径是一个单独的路径,并只包含这个状态;Viterbi路径的概率与起始概率是相同的。

主循环考量“obs”中的观测值序列。

T包含正确的信息但排除当前观测的点。

算法继续计算下一个可能状态的三元组(prob,v_path,v_prob)。

一个给定状态的总概率,total,为所有到达这个状态的概率的和。

更确切的说,算法迭代所有可能的源状态。

对每一个愿状态,T保存到某各状态所有路径的概率和。

这个概率然后乘以当前观测的产生概率和从当前状态转换到下一状态的转换概率。

产生的结果“prob”加入“total”中。

“Viterbi”路径的概率用一种类似的方法求得,但用一个离散的最大值代替了累加所有的路径。

起始时,最大值valmax为零。

对每个原状态,“Viterbi”路径的概率是已知的。

这也由产生概率,转移概率的乘积获得,如果大于现有值,就取代“valmax”。

通过拓展从下一状态指向当前状态的“Viterbi”路径,“Viterbi”路径被当作对应最大值的“argmax”来计算的。

在这种模式下得到的三元组(prob,v_path,v_prob)被储存在U中,一旦得到所有可能的下一状态的U,就取代T,然后保证在迭代的最后循环的不变量得到该值。

在最后,使用另一个总结/最大化的过程(当然,这一步也可以在主循环的内部进行,添加一个条件语句并在最后一次迭代中执行这一过程)。

在执行的例子中,算法的使用方法如下:def example():return forward_viterbi(observations,states,start_probability,transition_probability,emission_probability)print example()这个表明[`walk`,`shop`,`clean`]的概率和为0.033612,‘Viterbi’路径为[`Sunny`,`Rainy`,`Rainy`,`Rainy`],概率为0.009408. ‘Viterbi’路径包含四个状态,因为第四个观测值是由第第三个状态产生,并转移到第四个状态。

换句话说,一个已知的观测动作,当Bob出去散步时天气最可能是晴天;第一天下雨而接着那天也下雨。

在实现这个算法时,需要注意到很多语言用浮点数,因为p是很小的,这可能会造成读取空缓存。

一个常用的技巧是取概率的对数并用它贯穿整个计算。

这个技巧通常也用在对数系统中。

一旦算法结束,正确的结果可以通过指数运算得到。

如果你希望实现这算法,使它能接受任意状态,观测值,和概率值,用下面的代码代替上文的声明部分:states = []number_of_states=input('how many states? Please write an integer different from 0 or 1')index=0while index<number_of_states:states.append(str(raw_input('give a name to the statenumber'+str(index))))index=index+1observations = []number_of_observations=input('how many observations? Please write an integer different from 0 or 1')index=0while index<number_of_observations:observations.append(str(raw_input('give a name to the observation number '+str(index))))index=index+1start_probability = {}for state in states:start_probability[state] = input('give a value for the start probability of the state '+state)transition_probability = {}for initial_state in states:transition_probability[initial_state] = {}for final_state in states:transition_probability[initial_state][final_state]=input('give a value for the transition probability from the state '+initial_state+'to the state '+final_state)emission_probability = {}for state in states:emission_probability[state]= {}for observation in observations:emission_probability[state][observation]=input('give a value for the emission probability from the state '+state+' to the observation '+observation)。