第二章 基本MOS元件物理

第2章MOS器件物理基础

❖ 版图、电容、小信号模型等

第2章MOS器件物理基础

10

2.2 MOMSO的SI管/V工特作性-原工作理原理与阈值电压

当VG=0,MOS管相当于两个反偏的二极管,截止 当VG稍微增大时,在正的栅源电压作用下,产生电场,

这个电场排斥空穴而吸引电子,因此,使栅极附近的p型 衬底中的空穴被排斥,留下不能移动的受主离子(负离 子),截止。

第2章 MOS器件物理基础

2.1 基本概念

❖ 简化模型-开关 ❖ 结构

2.2 I/V特性

❖ 阈值电压 ❖ I-V ❖ 跨导

2.3 二级效应

❖ 体效应、沟道长度调制效应、亚阈值导电性

2.4 器件模型

❖ 版图、电容、小信号模型等

第2章MOS器件物理基础 1

2.1 基本概念-MOSFET开关

NMOS管三端器件,栅(G)、源(S)、 漏(D)。 通常作为开关使用,VG高 电平,MOS管导通,D、S连接。

nCox

W L

(VGS

Vth )VDS

1 2

VD2S

K N 2(VGS Vth )VDS VD2S

VGS-Vth:MOS管的“过驱动电压”

L:指沟道的有效长度

W/L称为宽长比,K N

1 2

nC,ox WL

称为NMOS管的导电因子,

μn载流子迁移率。

ID的值取决于工艺参数:μn、Cox、器件尺寸W和L、VDS及VGS。

第2章MOS器件物理基础 14

2.2 MOS的I/V特性-阈值电压

0 栅与衬底功函数差

COX

OX

TOX

单位面积栅氧化层电容

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH第02章就MO固S器定件物了理基,础 设计者无法改变

MOS器件物理基础

西安电子科技大学

17

MOS管在饱和区电流公式

西安电子科技大学

18

西安电子科技大学

Thanks!

19

MOS管所有pn结必须反偏: *N-SUB接VDD!

4 *P-SUB接VSS! *阱中MOSFET衬底常接源极S,why?

电路中的符号表征

西安电子科技大学

MOS管等效于一个开关!

5

西安电子科技大学

(a)栅压控制的MOSFET (b)耗尽区的形成(c)反型的开始

6 (d)反型层的形成

西安电子科技大学

西安电子科技大学

MOS器件物理基础

西安电子科技大学 刘术彬

1

西安电子科技大学

2

基本结构

西安电子科技大学

Ldrawn:沟道总长度 LD:横向扩散长度

*D、S是对称的,可互换? *所有pn结必须反偏!

Leff:沟道有效长度, Leff= Ldrawn-2 LD

3

西安电子科技大学

CMOS结构 (P、N基于同一衬底)

沟道单位长度电荷(C/m) 电荷移 动速度 (m/s)

12

I/V特性的推导(3)

西安电子科技大学

13

I/V特性的推导(4)

西安电子科技大学

14

西安电子科技大学 NMOS管VGS>VT、VDS> VGS+VT时的示意图

15

I/V特性的推导(5)

西安电子科技大学

16

饱和区MOSFET的I/V特性

NMOS管VGS>VT、VDS=0时的示意图

7

西安电子科技大学 NMOS管VGS>VT、0<VDS< VGS-VT时的示意图

8

CMOS器件基础

第二章MOS器件物理基础⏹在现代IC工业中,必须充分掌握半导体器件的知识,这一点对于模拟电路的设计比数字电路更为重要。

⏹模拟电路设计中,我们不能把晶体管等效为一个简单的开关,晶体管的许多二级效应直接影响其性能。

⏹IC技术的发展,使得器件尺寸按比例缩小,这些效应变得更加重要。

⏹设计者往往必须确定哪种效应在给定的电路中可以被忽略,因此,深入了解器件的工作情况是非常有价值的。

主要内容★基本概念简化模型结构符号★I/V特性阈值电压I-V关系式跨导★二级效应体效应、沟道长度调制效应、亚阈值导电性★器件模型版图、电容、小信号模型等一、基本概念G(Gate)栅极漏极MOSFET 开关MOSFET 问题:导通时V G 的值(阈值电压)?源漏之间的电阻?源漏电阻与各端电压的关系?…※三个端口:栅、源、漏。

※器件是对称的,源漏可以互换。

※作为开关工作时,栅电压为高电压,则源漏相连;栅电压为低,源漏断开。

NMOS管的简化结构⏹NMOS制作在P型衬底上,两个重掺杂N区形成源区和漏区,重掺杂多晶硅区(poly)作为栅极,一层薄SiO2绝缘层作为栅极与衬底的隔离。

⏹NMOS管有效作用发生在栅氧下的衬底表面的导电沟道(channel)上。

衬底:沟道总长度:沟道有效长度,Leff =Ldrawn -2 LD MOSFET 的结构:横向扩散长度(bulk 、body )漏极:收集载流子技术的发展主要的推动力就是在保证电性能的前提下,一代一代的缩小L 和toxN阱及PMOS阱:局部衬底Metal-Oxide Semiconductor Field-Effect,金属氧化物半导体场效应管MOS:载流子为电子;p型MOSFET :载流子为空穴MOS管正常工作的基本条件寄生二极管管正常工作的基本条件是: 所有衬源(B、S 、D)pn结必须反偏同一衬底上的NMOS和PMOS器件MOS管所有pn结必须反偏:寄生二极管MOS管符号(b)(c)四端器件,一般在模拟电需要明确衬底电位!省去了衬底,默认为衬底与源极相连。

MOS器件物理2-精选文档

I 2 K V V V D N GS th DS

上式表明在VDS较小时,ID是VDS的线性函数,即这时MOS管可 等效为一个电阻,其阻值为: V 1 DS R on I 2 K V V D N GS th

即:处于深三极管区的MOS管可等效为一个受过驱动电压控制 的可控电阻,当VGS一定时,沟道直流导通电阻近似为一恒定的 电阻。

IDS

I DS

IDS

Vthn

VGS

Vthn

VGS

0 Vthn Vth

VGS

增强型NMOS转移特性

耗尽型NMOS转移特性

转移特性的另一种表示方式

转移特性曲线

在实际应用中,生产厂商经常为设计者提供的参数 中,经常给出的是在零电流下的开启电压V th' 0 ' ' 注意 Vth , V 为无衬偏时的开启电压,而 V V th 0 th0 0 th0 是在与VGS特性曲线中与VGS轴的交点电压,实际上 为零电流的栅电压 从物理意义上而言, V th' 0 为沟道刚反型时的栅电压, 仅与沟道浓度、氧化层电荷等有关;而Vth0与人为 定义开启后的IDS有关。

漏极电流随栅源电压的变化率,即:

I D gm VGS V 2KN VGS Vth

D SC

2I D 2 KN I D VGS Vth

VGS-Vth:MOS管的“过驱动电压” L:指沟道的有效长度

W/L称为宽长比 1 W KN nC ,称为NMOS管的导电因子 ox 2 L ID的值取决于工艺参数:μnCox、器件尺寸W和L、VDS及VGS。

MOS管的电特性-输出特性(I/V特性)

第2章MOS器件物理基础

0.5 m nwell:p=100cm2/V-s, n=350cm2/V-s

西电微电子学院-董刚-模拟集成电路设计

24

跨导gm

VGS对IDS的控制能力

IDS对VGS变化的灵敏度

gm

ID V GS

W L

gm

VDS cons tan t

2 nC ox

W L

ID

n C ox

ID

n C ox W

2 L

(V GS V TH )

2

在ID一定时,W逐渐增大会导致VGS逐渐接近VTH ; 再增大时会进入亚阈值区

西电微电子学院-董刚-模拟集成电路设计 11

本讲

基本概念

简化模型-开关 结构 符号

I/V特性

阈值电压 I-V关系式 跨导

二级效应

体效应、沟道长度调制效应、亚阈值导电性

器件模型

版图、电容、小信号模型等

西电微电子学院-董刚-模拟集成电路设计 12

沟道电荷的产生

当VG大到一定 程度时,表面 势使电子从源 流向沟道区 VTH定义为表面 电子浓度等于衬 底多子浓度时的 VG

MOS管工作在哪个区?

Active

Active

西电微电子学院-董刚-模拟集成电路设计

27

本讲

基本概念

简化模型-开关 结构 符号

I/V特性

阈值电压 I-V关系式 跨导

二级效应

体效应、沟道长度调制效应、亚阈值导电性

器件模型

版图、电容、小信号模型等

西电微电子学院-董刚-模拟集成电路设计 28

34

沟长调制效应

g m nC ox W L (V GS V TH )(1 V DS )

第2章MOS器件物理基础

模拟CMOS集成电路设计

2011-9-2

MOS器件物理基础

13

饱和区MOS器件的I/V特性曲线

模拟CMOS集成电路设计

2011-9-2

MOS器件物理基础

14

PMOS

ID参考电流方向

截止区 三极管区(线性区)

饱和区

模拟CMOS集成电路设计

2011-9-2

MOS器件物理基础

15

4)跨导的定义 漏电流的变化量除以栅源电压的变化量,数学表达式为:

模拟CMOS集成电路设计

2011-9-2

MOS器件物理基础

7

阈值电压(VTH)定义 NMOS的VTH通常定义为界面的电子浓度等于P型衬 底的多子浓度时的栅压。

多晶硅栅和硅衬底的功函数之差

反型层与氧化硅层的表面势

(q是电子电荷,Nsub是衬底掺杂浓度,Qdep是耗尽区电荷) Cox是单位面积的栅氧化层电容

模拟CMOS集成电路设计

εsi表示硅介电常数。

2011-9-2

MOS器件物理基础

8

“本征”阈值电压

通过以上公式求得的阈值电压,通常称为“本征(native)”阈值 电压,典型值为-0.1V. 在器件制造工艺中,通常通过向沟道区注入杂质来调整VTH 对于NMOS,通常调整到0.7V(依工艺不同而不同)

模拟CMOS集成电路设计

2011-9-2

MOS器件物理基础

33

MOS SPICE模型

在电路模拟(simulation)中,SPICE要求每个器件都有一 个精确的模型。 种类

1st 代:Level1,Level2,Level3; 2nd代:BSIM,HSPICE level=28,BSIM2 3rd代:BSIM3,MOS model9,EKV(Enz-Krummenacher-Vittoz)

ch2 MOS器件物理基础

漏极流入衬底。

MOS器件物理基础 Ch. 2 # 14

2013-7-29华大信息科学与工程学院

MOS管的工作原理

(a) Vgs>Vth, Vds=0V

(b) Vgs>Vth, Vds<Vgs-Vth

(c) Vgs>Vth, Vds>Vgs-Vth

MOS器件物理基础 Ch. 2 # 15

2013-7-29华大信息科学与工程学院

电荷移 动速度 (m/s)

Qd (x) WCox (VGS V (x) VTH )

Qd:沟道电荷密度 Cox:单位面积栅电容

WCox:MOSFET单位长度的总电容 Qd(x):沿沟道点x处的电荷密度 V(x):沟道x点处的电势 V(x)|x=0=0, V(x)|x=L=VDS

MOS器件物理基础 Ch. 2 # 19

MOS器件物理基础 Ch. 2 # 13

2013-7-29华大信息科学与工程学院

MOS管的工作原理

– 当VGS≥Vth时,外加较小的VDS,ID将随VDS上升迅速增大,此时为线性区,但由 于沟道存在电位梯度,因此沟道厚度是不均匀的。

– 由于ID通过沟道形成自漏极到源极方向的电位差,因此加在“平板电容器”上的

MS

Qss Cox

MOS器件物理基础 Ch. 2 # 16

2013-7-29华大信息科学与工程学院

• “本征”阈值电压

通过以上公式求得的阈值电压,通常成为“本征(native)”阈 值电压.

在器件制造工艺中,通常通过向沟道区注入杂质来调整VTH

对于NMOS,通常调整到0.7V(依工艺不同而不同)

同一衬底上的NMOS和PMOS器件

MOS管所有pn结必须反偏: *N-SUB接VDD! *P-SUB接VSS! *阱中MOSFET衬底常接源极S

模拟CMOS

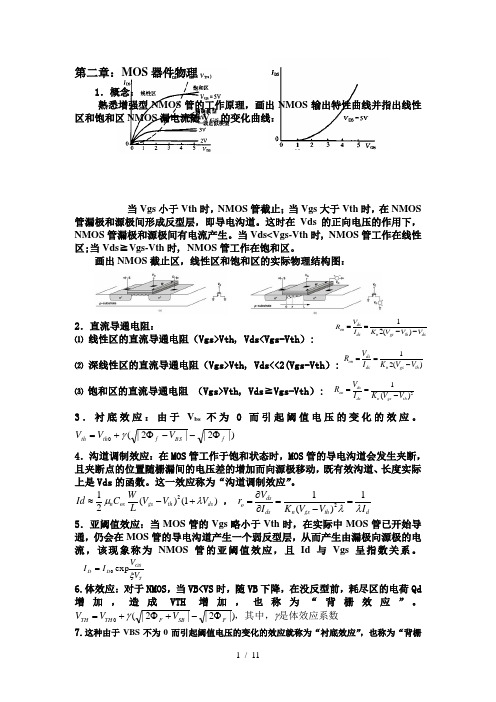

21()ds on ds n gs thV R I K V V ==-12()ds on ds n gs th V R I K V V ==-12()ds on dsn gs th dsVR I K V V V ==--第二章:MOS 器件物理1.概念:熟悉增强型NMOS 管的工作原理,画出NMOS 输出特性曲线并指出线性区和饱和区NMOS 漏电流随V GS 的变化曲线:当Vgs 小于Vth 时,NMOS 管截止;当Vgs 大于Vth 时,在NMOS管漏极和源极间形成反型层,即导电沟道。

这时在Vds 的正向电压的作用下,NMOS 管漏极和源极间有电流产生。

当Vds<Vgs-Vth 时, NMOS 管工作在线性区;当Vds ≧Vgs-Vth 时, NMOS 管工作在饱和区。

画出NMOS 截止区,线性区和饱和区的实际物理结构图:2.直流导通电阻:⑴ 线性区的直流导通电阻(Vgs>Vth, Vds<Vgs-Vth ):⑵ 深线性区的直流导通电阻(Vgs>Vth, Vds<<2(Vgs-Vth ):⑶ 饱和区的直流导通电阻 (Vgs>Vth, Vds ≧Vgs-Vth ):3.衬底效应:由于V bs 不为0而引起阈值电压的变化的效应。

)|2||2|(0f BS f th th V V V Φ--Φ+=γ4.沟道调制效应:在MOS 管工作于饱和状态时,MOS 管的导电沟道会发生夹断,且夹断点的位置随栅漏间的电压差的增加而向源极移动,既有效沟道、长度实际上是Vds 的函数。

这一效应称为“沟道调制效应”。

21()(1)2n ox gs th ds W Id C V V V L μλ≈-+ , 211()ds o ds n gs th d V r I K V V I λλ∂===∂- 5.亚阈值效应:当MOS 管的Vgs 略小于Vth 时,在实际中MOS 管已开始导通,仍会在MOS 管的导电沟道产生一个弱反型层,从而产生由漏极向源极的电流,该现象称为NMOS 管的亚阈值效应,且Id 与Vgs 呈指数关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例題 2.7

繪出 VX 由 0 變至 3V 時,圖2.34中 M1 之電容圖。假設 VTH= 0.6V 且 λ=γ= 0。

例題 2.7〈續〉

解: 為避免混淆,如圖2.34所示,我們將三個端點標上記號。當 VX≒ 0 時, M1 操作於三極管區,CEN≒CEF=(1/2)WLCox+WCov,且 CFB 為最大值, CNB 則和 VX 無關。當 VX 超過 1V 時,源極和汲極的角色會互換[圖 2.35(a)];而當 VX ≧ 2V-0.6V 時,M1 將會脫離三極管區。其電容變化 如圖2.35(b)和(c)所示。

5. 因為 ID 在通道中為一常數

三極管區汲極電流電壓關係圖

(Triode)

拋物線峰值發生於 VDS=VGS-VTH, 此時電流為 I 1 C W (V V ) 2 D n ox GS TH 2 L

深三極管區之電阻特性

(Deep triode)

VDS≦VGS-VTH 時稱元件操 作於三極管區或線性區。 若 VDS<<2(VGS-VTH ) ,可 得

MOS元件電容

(1) C1 WLC ox (2) C2 WL q si N sub / 4( F ) (3) C3 和 C4 不可寫成 CLDCox,應以重 疊電容 Cov 表示。

(4) 下板電容 Cj 和側邊電容 Cjsw。

C j C j 0 /[1 VR / B ]m

例題 2.6

2.2 MOS I/V特性圖

2.2.1 臨界電壓 2.2.2 I/V特性圖之推導

2.3 二階效應

學習積體電路設計的方法

1. 以量子力學開始,並了解固態物理、半導體元件物 理、元件模型,最後則是電路的設計。 2. 將每個半導體元件視為一黑盒子,其特性皆以端點 電壓和電流表示,因此不需要注意元件內部運作更 可設計電路。

飽和區時,電流由 x= 0 積分至 x=L’ ,L’ 為 Qd 降至 0 之處, 因此可得電流為

飽和MOSFET做為連接汲極和源極之電流源,將電流送至接 地端或由VDD處吸引電流,換句話說只有一端是浮動的。

PMOS元件之電流公式

三極管區: VDS < (VGS-VTH)

飽和區: VDS (VGS-VTH)

以MOSFET做為開關

MOS元件的簡單示意圖。閘極電壓 VG 為高 電壓時,電晶體將連接源極與汲極;而當 VG 為低電壓時,電晶體則隔絕源極與汲極。

MOSFET結構

Leff = Ldrawn-2LD

Leff 為等效長度,Ldrawn 為全長,LD 為擴散長度。

對於源極和汲極來說,結構是對稱的。

鳥瞰示意圖和MOS上視圖。

例題 2.5

繪出圖2.29(a)中電路佈線設計圖 (Layout design)

解: 注意 M1 和 M2 在節點 C 分享同一個源極/汲極接面,而 M2 和 M3 在節點 N 分享同一個 S/D 接面。我們猜測三個電晶體可以如圖2.29(b)之佈線圖, 將其餘端點連接起來,便可得到圖2.29(c)之佈線圖。注意 M3 之閘極多 晶矽層無法直接連至 M1 之源極,因此需要另一條金屬連線。

基板效應對輸入輸出電壓的影響

(a)源極-基板電壓隨輸入電壓改變之電路。 (b)無基板效應時,如果 I1 為常數,Vin-Vout 亦為常數。

(c)有基板效應時,VTH 升高,為了保持 ID 為常數,Vin-Vout 值必須增加。

通道長度調變效應

(Channel Length Modulation (Early) Effect)

為基板效應係數。

例題 2.3

如圖2.23(a)所示,繪出 VX 從 -∞ 至 0 之汲極電流圖。假設 VTH0= 0.6V, γ= 0.4V1/2,2ΦF= 0.7V。

解:

如果負 VX 值夠大時,M1 臨界電壓將會超過 1.2V 且元件為關閉狀態, 也就是說

因此 VX1=-4.76V。當 VX1 < VX < 0 時,ID 將會增加。根據下式 圖2.23(b)顯示了其特性結果。

MOS元件設計

The layout of a MOSFET is determined by: 1. Electrical properties required of the device in the circuit. 2. “Design rules” imposed by the technology. Ex: To minimize capacitance of S and D, W is the channel width, the other dimension must be large enough to accommodate the contact windows and is specified by the technology (diffusion encloses contact rule).

考慮一攜帶電流 I 之半導體柱,沿著電流方 向之電荷密度為 Qd,其電荷速度為 v。則 I=Qd〃v

I/V特性圖之推導(二)

(a)源極和汲極電壓相同之通道電荷; (b)源極和汲極電壓不同之通道電荷。

I/V特性圖之推導(三)

1. VGS≧VTH 時之通道電荷密度 2. 考慮汲極端電壓為 VD,則通 道中某一點 x 之電荷密度 3. 若 v=μE 為通道內電子速度, 其中μ為電荷載子遷移率,E為 電場,則電流值為 4. 考慮邊界條件 V(0)=0,V(L)=VDS,同乘 dx 並對其積分

ΦF=(kT/q)ln(Nsub/ni) ,其中 q 為電子電荷,Nsub 為基 板摻雜濃度,Qdep 為空乏區之電荷數量,Cox 為單位 面積之閘氧化層電容,εsi 代表矽的介電常數。 摻入 p+ 雜質改變氧化層界面附近的基板濃度進而改 變臨界電壓值。

PFET的開啟

在PFET中形成反轉層。

I/V特性圖之推導(一)

不同操作區中的元件電容

(1) 關閉:

CGD CGS CovW CGB (WLC ox )Cd /(WLC ox Cd )

Cd WL q si N sub / 4( F )

(2) 深三極區: CGD CGS WLC ox / 2 WC ov (3) 飽和區: CGS 2WLeff Cox / 3 WC ov

答: 我們寫出下列式子 且 1 / L,我們注意到如果長度加倍時,ID/VDS 斜率將會變為四分之 一。此乃是因為 I D VDS L 1 L2 (圖2.26),當給定一驅動閘極 -源極電壓時,較大之 L 可提供較理想的電流源,但會降低元件之電流 容量,因此 W 可能必須被等比例地增加。

轉導

(Transconductance)

定義一指標為汲極電流變化除以閘極-源極電壓變化,代表 元件將電壓轉換成電流的能力,稱為轉導。

MOS轉導與驅動電壓及汲極電流之關係圖

飽和區和三極管區之概念示意圖

例題 2.2

如圖2.19所示,繪出轉導和之關係圖。

解: 當 VDS 從無限大開始減少,了解 gm 是較為簡單的,只要 VDS ≧ Vb- VTH,M1 將操作於飽和區,ID 則為常數。從式(2.18)得知 gm 亦為常數。 當 VDS < Vb-VTH 時,M1 操作於三極管區,且:

從源極至汲極路徑可用一 線性電阻表示

例題 2.1

如圖2.14(a)所示,繪出 M1 之開啟電阻和之關係圖。假設 μnCox= 50 μA/V2,W/L= 10,VTH= 0.7V。注意其汲極端為開啟狀態。

解: 因為汲極端被開啟,ID= 0 且 VDS= 0,因此如果元件開啟時,將操作於 深三極管區。當 VG<1V+VTH 時,M1 關閉且 RD= ∞。當 VG>1V+VTH 時, 我們得到

圖2.26 通道長度加倍的影響

次臨界傳導

(Subthreshold)

當 VGS ≒ VTH 時,一個弱反轉層仍會存在,且電流亦會由 汲極流回源極,甚至當 VGS < VTH 時,ID 仍為有限,其和 VGS 之關係為指數相關。當 VDS > 200mV 時

其中ζ > 1 為一非理想因子,且 VT = kT/q。

NFET的開啟現象

(a)閘電壓驅動之MOSFET;(b)空乏區之形成; (c)初始的反轉層;(d)反轉層形成。

Threshold Adjustment

In practice, the threshold value is “ negative” and not suitable to circuit design. the threshold voltage is typically adjusted by implantation of dopants into the channel area. PMOS Device Formation of inversion layer in a PMOSFET when the gatesource voltage becomes sufficiently negative.

計算圖2.32中二種結構之源極和汲極接面電容。

解:

例題 2.6〈續〉

對圖2.32(a)之電晶體而言,我們可以得到

而對圖2.32(b)而言,

圖2.32(b)之幾何形狀被稱為摺疊(folded)結構。當我們提供同樣的 W/L 時, 圖2.32(b)之汲極接面電容比圖2.32(a)還小。 在上述計算中,我們已假定源極或汲極之總周長為 2(W+E) 乘上 Cjsw。面對通道之側邊電容可能會比其它三個側面電容小,因為通道截 止佈植效應(channel-stop implant)(見第十七章)。儘管如此,我們還是假 定所有的四個側邊都有相同的單位電容,因為電路中的每個節點都連結 至許多其它的元件電容,故由假設所造成的誤差 Device Physics