4011 CMOS 四2输入与非门

巧用一片CD4011组装七种逻辑门电路

巧用一片CD4011组装七种逻辑门电路陕西汉中宇星电力电子学校郭秦汉笔者用一块CD4011(四2与非门)和少量的外围元件,用三组电路分别制作了与非门、非门、与门、或非门、或门以及与或非门和异或门电路,经实验效果很好。

后来用此方法辅导学生制作,使学生对逻辑门电路应用有了初步的认识,对门电路的变通使用有了新的理解,增强了学生用学过的知识解决问题的能力,提高了学习兴趣。

现把制作方法介绍给大家,供参考。

一、五种基本门电路制作CD4011内部结构如图1所示。

此IC工作电压范围宽(3V~18V),且不易损坏。

笔者在做试验时,将一块IC反复拆装测试数次,依然完好。

1.组装与非门电路只要将电源接通,给输入端加上高电平或低电平,就可以直接测量其逻辑状态。

2.要组成与门电路,根据上述原理只需在输入端加一级非门。

在实际运用中,把与非门两个输入端并联,就把与非门改成了非门如图2所示。

3.或非门用两只二极管和一个电阻,组成或门电路,用两个与非门改装的非门,用来对小信号进行放大,组成或非门电路。

表达式为:逻辑图见图3所示。

具体电路如图4所示。

&1、&2组成与门电路,VD2、VD3和&3、&4组成或门电路,IC工作电压为DC9V,○14脚接电源正极,⑦脚接负极,VD1用于防止电源极性接反。

C为滤波电容,R3、R4为下拉电阻。

为了简化测试操作过程,将A、B端直接置0,即A=0、B=0,R1、R2为高电平输入信号源,如将其输出端接A或B,都可以使原来的状态发生改变,成为高电平。

与门、或门的输出端Y都接有发光二极管和限流电阻,用来显示输出状态。

输出高电平时,LED亮,输出低电平时,LED灭。

在测试中,可按照真值表要求,在A、B端输入电平,根据对应的LED亮为1,灭为0填入表格,完成对门电路的测试。

如需测试非门电路,可以将IC的④脚与LED的连接点断开而改接到或门电路⑩、⑥、⑩脚的连接处,在VD2、VD3输入高电平,便可以在检测或非门和或门的逻辑功能的同时,观察到&4的输入和输出电平,总是一高一低,两只LED一亮一灭,其逻辑功能符合逻辑函数表达式:如要测试与非门和或非门的逻辑功能,只需将与门端接④脚LED1正端拆下,改接到③脚上。

40系列管脚图

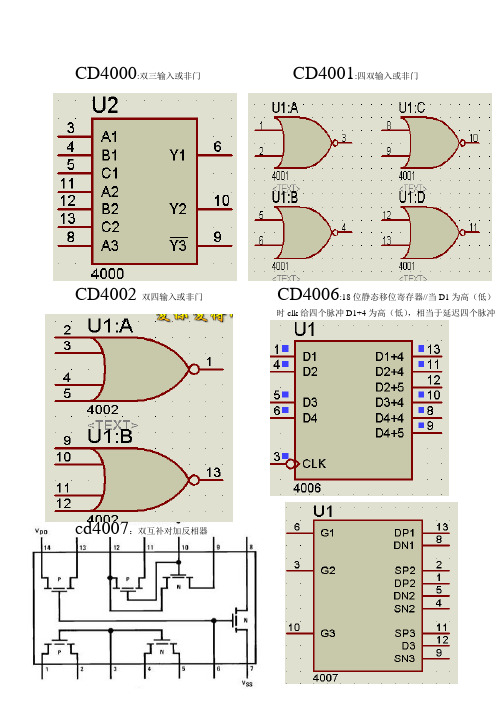

CD4000:双三输入或非门CD4001:四双输入或非门CD4002双四输入或非门CD4006:18位静态移位寄存器//当D1为高(低)时clk给四个脉冲D1+4为高(低),相当于延迟四个脉冲cd4007:双互补对加反相器CD4008:并行进位输出全加器CD4009:六缓相器/转换-倒相CD4010:六缓相器/转换-正相CD4011四2输入端与非门CD4012双4输入端与非门CD4013双主-从D型触发器CD4014 8位串入/并入-串出移位寄存器CD4015双4位串入/并出移位寄存器CD4016四传输门CD4017十进制计数/分配器CD4018可预制1/N计数器//当PE为高时并行输入数据,与clk无关,PE为低时D输入并移位CD4019四与或选择器CD4020 14级串行二进制计数/分频器clk给八个下降沿Q3开始计数CD4021 08位串入/并入-串出移位寄存器当9脚为同时D5-D7并行输入数据且与时钟无关,当其为低电平时从D4数据开始移位,SIN数据迟后六个脉冲CD402八进制计数/分配器CD4023三3输入端与非门CD4024 7级二进制串行计数/分频器CD4025三3输入端或非门CD4026十进制计数/7段译码器当2和15为低3为高时,数码管随脉冲0-1-2…9-02脚为高电平时计数锁存脚5.4.14一般为高显9时5脚为低显2时14脚为低4脚与3脚一至CD4027双J-K触发器CD4028 BCD码十进制译码器当jk同时为1时Qn+1=Qn’CD4029可预置可逆计数器CD4030四异或门当输入全部为低时,只给clk时钟,输出从9到0计数co平时为高输出为0时其为低,当只有10脚为高时给Clk电路从0到9计数,co只在显9时为低。

5脚为高电平则锁存。

1脚为高则并行置数·CD4033 十进制计数/7段译码器CD4034 8位通用总线寄存器CD4035 4位并入/串入-并出/串出移位寄存CD4038三串行加法器CD4040 12级二进制串行计数/分频器CD4041四同相/反相缓冲器脚1为脚3的同相输出,脚2为脚3的反相输出CD4042四锁存D型触发器CD4043 4三态R-S锁存触发器("1"触发) CD4044四三态R-S锁存触发器("0"触发) CD4046锁相环\\见资料CD4047无稳态/单稳态多谐振荡器\\见资料CD4048 4输入端可扩展多功能门\\见资料CD4049六反相缓冲/变换器CD4050六同相缓冲/变换器CD4051八选一模拟开关CD4052双4选1模拟开关6脚为低电平时有效;6脚为低电平时无效CD4053三组二路模拟开关只要A为1,NH CD4054 液晶显示驱动器为低x=x1;若A为0;INH为低不管BCX=x0CD4055 BCD-7段译码/液晶驱动器CD4056液晶显示驱动器当6脚为高电平时输出反码CD4059“N”分频计数器CD4060 14级二进制串行计数/分频器CD4063四位数字比较器CD4066四传输门CD4067 16选1模拟开关CD4068八输入端与非门/与门4069六反相器CD4070四异或门CD4071四2输入端或门CD4072双4输入端或门CD4073三3输入端与门CD4075三3输入端或门CD4076四D寄存器\\见资料CD4077四2输入端异或非门CD4078 8输入端或非门/或门CD4081四2输入端与门CD4082双4输入端与门CD4093四2输入端施密特触发器CD4085双2路2输入端与或非门CD4094 8位移位存储总线寄存器CD4095 3输入端J-K触发器STB为高时则将移位的数据显示出来,STB为低时输出保持不变,移位在工作只是没有显出来,要等到下次STB为高时才显出来,相当于74595的两个时钟CD4096 3输入端J-K触发器CD4098双单稳态触发器CD4099 8位可寻址锁存器CD40105先入先出FI-FD寄存器CD40106六施密特触发器CD40110十进制加/减,计数,锁存,译码驱动CD40160可预置BCD加计数器CD40161可预置4位二进制加计数器CD40162 BCD加法计数器CD40163 4位二进制同步计数器CD40174六锁存D型触发器CD40175四D型触发器CD40192可预置BCD CD40193可预置4位二进制CD40194 4位并入/串入-并加/减计数器(双时钟) 加/减计数器出/串出移位寄存CD4502可选通三态输出六反相/缓冲器CD4503六同相三态缓冲器CD4508双4位锁存D型触发器//12脚为低反相CD4510可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512八路数据选择器CD4513 BCD锁存,7段CD4514 4位锁存,4线-16CD4515 4位锁存,4线-16 译码,驱动器(消隐) 线译码器线译码器CD4516可预置4位二进制加/减计数器CD4518双BCD同步加计数器CD4520双4位二进制同步加计数器CD4522可预置BCD同步1/N计数器CD4526可预置4位二进制同步1/N计数器CD4528双单稳态触发器CD4529双四路/单八路模拟开关CD4530双5输入端优势逻辑门CD4532 8位优先编码器CD4538精密双单稳CD4539双四路数据选择器CD4541 可编程序振荡/计时器CD4543BCD七段锁存译码,驱动器CD4553三位BCD计数器CD4555双二进制四选一译码器/分离器CD4556双二进制四选CD4560 "N"BCD加法器CD4584六施密特触发器一译码器/分离器CD4585 4位数值比较器。

CC4011

tTHL 输出由高电平到低电平 转换时间

C1 输入电容 (任一输入端)

测试条件 VDD(V)

CL=50pF

5.0

RL=200k

10.0

tr=20ns

15.0

tf=20ns

5.0

10.0

15.0

5.0 10.0 15.0 5.0 10.0 15.0

-

规范值

最小

最大

15.0

11.0

IOH 输出高电 2.5

5/0 5.0 -2.0 -1.8

-1.6

-1.3 -1.15

mA

平电流

4.6

5/0 5.0 -0.64 -0.61 -0.51

-0.42 -0.36

(最小)

9.5

10/0 10.0 -1.6 -1.5

-1.3

-1.1 -0.9

13.5 15/0 15.0 -4.2 -4.0

15/0 15.0

-40℃

VIL 输入低电 4.5

平电压

9.0

(最大)

13.5

-

5.0

10.0

15.0

规范值 25℃ 85℃

0.05

4.95 9.95 14.95

1.5 3.0 4.0

125℃

单位 V V

V

VIH 输入高 4.5/0.5

-

5.0

3.5

V

电平电压 9.0/1.0

10.0

7.0

(最小) 13.5/1.5

CC4011------四2输入与非门

简要说明 CC4011 为 2 输入正向逻辑与非门。 CC4011 与非门为系统设计者提供了直接的与非功能,补充了已有 COS/MOS

40系列CMOS电路型号功能

40193 CMOS 可预制四位二进制计数器

40194 CMOS 4位双向并行存取通用移位寄存器

4020 CMOS 14级二进制串行计数/分频器

40208 CMOS 4×4多端寄存器

4021 CMOS 异步8位并入同步串入/串出寄存器

4022 CMOS 八进制计数器/分频器

4010 CMOS 六缓冲器/转换器(同相)

40100 CMOS 32位双向静态移位寄存器

40101 CMOS 9位奇偶发生器/校验器

40102 CMOS 8位BCD可预置同步减法计数器

40103 CMOS 8位二进制可预置同步减法计数器

40104 CMOS 4位三态输出双向通用移位寄存器

40105 CMOS 先进先出寄存器

40106 CMOS 六施密特触发器

40107 CMOS 2输入双与非缓冲/驱动器

40108 CMOS 4×4多端寄存

40109 CMOS 四三态输出低到高电平移位器

4011 CMOS 四2输入与非门

40110 CMOS 十进制加减计数/译码/锁存/驱动

4035 CMOS 4位并入/并出移位寄存器

4038 CMOS 3位串行负逻辑加法器

4040 CMOS 12级二进制计数/分频器

4041 CMOS 四原码/补码缓冲器

4042 CMOS 四时钟控制 D 锁存器

4043 CMOS 四三态或非 R/S 锁存器

4502 CMOS 可选通六反相缓冲器

4503 CMOS 六三态同相缓冲器

4504 CMOS 六TTL-CMOS电平移位器

4506 CMOS 双二组2输入可扩展与或非门

CD系列芯片大全

******************************************************************** ** CD 系列门电路CD4000 双 3输入端或非门CD4001 四 2输入端或非门CD4002 双 4输入端或非门CD4007 双互补对加反向器CD4009 六反向缓冲/变换器CD4011 四 2输入端与非门CD4012 双 4输入端与非门CD4023 三 2输入端与非门CD4025 三 2输入端与非门CD4030 四 2输入端异或门CD4041 四同相/反向缓冲器CD4048 8输入端可扩展多功能门CD4049 六反相缓冲 /变换器CD4050 六同相缓冲/变换器CD4068 8输入端与门/与非门CD4069 六反相器CD4070 四 2输入异或门CD4071 四 2输入端或门CD4072 双 4输入端或门CD4073 三 3输入端与门CD4075 三 3输入端或门CD4077 四异或非门CD4078 8输入端与非门/或门CD4081 四 2输入端与门CD4082 双 4输入端与非门CD4085 双 2路 2输入端与或非门CD4086 四 2输入端可扩展与或非门CD40104 TTL至高电平 CMOS 转换器CD40106 六施密特触发器CD40107 双 2输入端与非缓冲/驱动器CD40109 四低 -高电平位移器CD4501 三多输入门CD4052 六反向缓冲器(三态输出CD4503 六同相缓冲器(三态输出CD4504 6TTL或 CMOS 同级移相器CD4506 双可扩展 AIO 门CD4507 四异或门CD4519 4位与/或选择器CD4530 双 5输入多数逻辑门CD4572 四反向器加二输入或非门加二输入与非门CD4599 8位可寻址锁存器******************************************************************** ** 触发器CD4013 双 D 触发器CD4027 双 JK 触发器CD4042 四锁存 D 型触发器CD4043 四三态 R-S 锁存触发器(“ 1”触发CD4044 四三态 R-S 锁存触发器(“ 0”触发CD4047 单稳态触发/无稳多谐振荡器CD4093 四 2输入端施密特触发器CD4098 双单稳态触发器CD4099 8位可寻址锁存器CD4508 双 4位锁存触发器CD4528 双单稳态触发器 (与 CD4098管脚相同,只是 3、 13脚复位开关为高电平有效 CD4538 精密单稳多谐振荡器CD4583 双施密特触发器CD4584 六施密特触发器CD4599 8位可寻址锁存器******************************************************************** ** 计数器CD4017 十进制计数 /分配器CD4020 14位二进制串行计数器 /分频器CD4022 八进制计数 /分配器CD4024 7位二进制串行计数器 /分频器CD4029 可预置数可逆计数器(4位二进制或 BCD 码CD4040 12二进制串行计数器 /分频器CD4045 12位计数/缓冲器CD4059 四十进制 N 分频器CD4060 14二进制串行计数器 /分频器和振荡器CD4095 3输入端 J-K 触发器(相同 J-K 输入端CD4096 3输入端 J-K 触发器(相反和相同 J-K 输入端CD40110 十进制加/减计数/锁存/7端译码/驱动器CD40160 可预置数 BCD 加计数器(异步复位CD40161 可预置数 4位二进制加计数器 (R非=0时, CP 上脉冲复位 (异步复位CD40162 可预置数 BCD 加计数器(同步复位CD40163 可预置数 4位二进制加计数器 (R非=0时, CP 上脉冲复位 (同步复位CD40192 可预置数 BCD 加 /减计数器CD40193 可预置数 4位二进制加 /减计数器CD4510 可预置 BCD 加 /减计数器CD4516 可预置 4位二进制加 /减计数器CD4518 双 BCD 同步加计数器CD4520 双同步 4位二进制加计数器CD4521 24级频率分频器CD4522 可预置数 BCD 同步 1/N加计数器CD4526 可预置数 4位二进制同步 1/N加计数器CD4534 实时与译码计数器CD4536 可编程定时器CD4541 可编程定时器CD4553 3数字 BCD 计数器CD4568 相位比较器/可编程计数器CD4569 双可预置 BCD /二进制计数器CD4597 8位总线相容计数/锁存器CD4598 8位总线相容可建地址锁存器******************************************************************** **译码器CD4511 BCD锁存 /7段译码器 /驱动器CD4514 4位锁存 /4-16线译码器CD4515 4位锁存 /4-16线译码器(负逻辑输出CD4026 十进制计数 /7段译码器(适用于时钟计时电路,利用 C 端的功能可方便的实现 60或 12分频CD4028 BCD-十进制译码器CD4033 十进制计数 /7段译码器CD4054 4位液晶显示驱动CD4055 BCD-7段码/液晶驱动CD4056 BCD-7段码/驱动CD40102 8位可预置同步减法计时器(BCDCD40103 8位可预置同步减法计时器(二进制CD4513 BCD-锁存/7端译码/驱动器(无效“ 0”不显CD4514 4位锁存/4线— 16线译码器(输出“ 1”CD4515 4位锁存/4线— 16线译码器(输出“ 0”CD4543 BCD-锁存/7段译码/驱动器CD4544 BCD-锁存/7段译码/驱动器——波动闭锁CD4547 BCD-锁存/7段译码/大电流驱动器CD4555 双二进制 4选 1译码器/分离器(输出“ 1”CD4556 双二进制 4选 1译码器/分离器(输出“ 0”CD4558 BCD-7段译码CD4555 双二进制 4选 1译码器 /分离器CD4556 双二进制 4选 1译码器 /分离器(负逻辑输出******************************************************************** **移位寄存器CD4006 18位串入—串出移位寄存器CD4014 8位串入 /并入—串出移位寄存器CD4015 双 4位串入—并出移位寄存器CD4021 8位串入 /并入—串出移位寄存器CD4031 64位移位寄存器CD4034 8位通用总线寄存器CD4035 4位串入 /并入—串出 /并出移位寄存器CD4076 4线 D 型寄存器CD4094 8位移位/存储总线寄存器CD40100 32位左移/右移CD40105 先进先出寄存器CD40108 4×4多端口寄存器阵列CD40194 4位并入/串入—并出/串出移位寄存器(左移/右移CD40195 4位并入/串入—并出/串出移位寄存器CD4517 64位移位寄存器CD45490 连续的近似值寄存器CD4562 128位静态移位寄存器CD4580 4×4多端寄存器******************************************************************** **模拟开关和数据选择器CD4016 四联双向开关CD4019 四与或选择器【 Qn=(An*Ka+(Bn*Kb】CD4051 单八路模拟开关CD4052 双 4路模拟开关CD4053 三 2路模拟开关CD4066 四双向模拟开关CD4067 单十六路模拟开关CD4097 双八路模拟开关CD40257 四 2选 1数据选择器CD4512 八路数据选择器CD4529 双四路/单八路模拟开关CD4539 双四路数据选择器CD4551 四 2通道模拟多路传输******************************************************************** ** 运算电路CD4008 4位超前进位全加器CD4019 四与或选择器【 Qn=(An*Ka+(Bn*Kb】CD4527 BCD比例乘法器CD4032 三路串联加法器CD4038 三路串联加法器(负逻辑CD4063 四位量级比较器CD4070 四 2输入异或门CD4585 4位数值比较器CD4089 4位二进制比例乘法器CD40101 9位奇偶发生器/校验器CD4527 BCD比例乘法器CD4531 12位奇偶数CD4559 逐次近似值码器CD4560 “ N ” BCD 加法器CD4561 “ 9”求补器CD4581 4位算术逻辑单元CD4582 超前进位发生器CD4585 4位数值比较器******************************************************************** ** 存储器CD4049 4字×8位随机存取存储器CD4505 64×1位 RAMCD4537 256×1静态随机存取存储器CD4552 256位 RAM******************************************************************** ** 特殊电路CD4046 锁相环集成电路CD4532 8位优先编码器CD4500 工业控制单元CD4566 工业时基发生器CD4573 可预置运算放大器CD4574 比较器、线性、双对双运放CD4575 双/双预置运放/比较器CD4597 8位总线相容计数/锁存器CD4598 8位总线相容可建地址锁存器。

4与非门4011特性及应用_触摸开关_触发报警器

非门电路。由门 1、2 组成一个“电平自锁”电路;门 1 输出端直接与门 2 的输入端相连,门 2 的输出端通 过电阻 R2 与门 1 的输入端相连。这样,当门 1 的输 入端得到一个高电平的外来控制信号,则输出低电 平到门 2 的输入端;门 2 的输出端输出高电平。这 个高电平通过电阻 R2 输出到门 1 的输入端。如果 门 1 的输入端外来的控制信号消失,门 1 的输入端 仍然保持为高电平;门 1、门 2 的输出状态仍然保持 不变,门 2 的输出端仍然保持为高电平。反之,当门 1 的输入端得到一个低电平的控制信号,则该电路 门 2 的输出端就会变成低电平并保持不变。

二、“BB 机”讯响器

1. BB 机讯响器电路 电路图如图 2 所示,该电路可以产生类似 BB 机的“嘀嘀嘀、嘀嘀嘀……”的叫声。

图1

2. 4011 逻辑运算特性 4011 每个与非门有两个输入端,一个输出端。 只有当两个输入端同时输入高电位,输出端才能输 出低电位;只要有一个输入端输入低电位,则输出端 输出高电位。4011 逻辑运算的真值表如下。

电阻 R2 的阻值为 1M,远远大于 R1 的 51k,所 以无论是触发信号还是解除信号,电阻 R2 传递的 电压都不能对它们产生实质的影响。但是当触发信 号或解除信号消失后,电阻 R2 发挥作用,将自锁电 压传送到门 1 的输入端。

可以通过改变电阻 R1 和电容 C1 的取值来改 变触发延迟的时间长短,它们的取值小一些,触发的 灵敏度就高一些;它们的取值越大,对触发的反应就 越迟钝。但是要始终保持 R1 与 R2 的比例关系,使 得 R1 远远小于 R2。

由于脉冲延迟电路中上面的一路接有接触按 钮,并且在脉冲反相电路中多用了一个非门,导致该 线路分布电容增大;于是在下面的一路电路中,接入 了电阻 R5,使两路的分布电容大致相等。

CC4012

VO

VI

(V) (V)

-

5/0

10/0

15/0

VDD (V)

5.0 10.0 15.0

-55℃

-

5/0 5.0

10/0 10.0

15/0 15.0

-40℃

VIL 输入低电 4.5

平电压

9.0

(最大)

13.5

-

5.0

10.0

15.0

规范值 25℃ 85℃

0.05

4.95 9.95 14.95

1.5 3.0.5V~18V 输入电压……-0.5V~VDD+0.5V 输入电流…………….±10mA 储存稳定…………-65℃~150℃

逻辑符号

引出端排列(俯视)

逻辑图(1/2) 逻辑表达式

静态特性: 参数

VOL 输出低 电平电压 (最大) VOH 输出高 电平电压 (最小)

测试条件

tPLH 输出由低电平到高电平 传输延迟时间

tPHL 输出由高电平到低电平 传输延迟时间

tTLH 输出由低电平到高电平 转换时间

tTHL 输出由高电平到低电平 转换时间

CI 输入电容 (任一输入端)

测试条件

CL=50pF RL=200k tr=20ns tf=20ns

VDD(V)

5.0 10.0 15.0

125℃

单位 V V

V

VIH 输入高 4.5/0.5

-

5.0

3.5

V

电平电压 9.0/1.0

10.0

7.0

(最小) 13.5/1.5

15.0

11.0

IOH 输出高电 2.5

5/0 5.0 -2.0 -1.8

CD4011中文使用说明书

VO=4.6V,VI=0 或 5V 输出高电平电流 输出高电平电流 输入漏电流 -IOH -IOH ±IIN VO=9.5V,VI=0 或 10V VO=13.5V,VI=0 或 15V VO=2.5V,VI=0 或 5V VIN=0 或 15V

VDD=5V VDD=10V VDD=15V VDD=5V VDD=15V

V

输出低电平电流

VO=1.5V,VI=0 或 15V VO=4.6V,VI=0 或 5V 输出高电平电流 输出高电平电流 输入漏电流 -IOH -IOH VO=9.5V,VI=0 或 10V VO=2.5V,VI=0 或 5V VIN=0 或 15V

or

1.4 ±IIN VDD=15V 符号 测 试 条 件 最小 典型 IDD VI=VSS 或 VDD;IO=0 VI=VSS 或 VDD, ∣IO∣<1µA VOL VOH VI=VSS 或 VDD, ∣IO∣<1µA VDD=5V VDD=10V VDD=15V VDD=5V VDD=10V VDD=15V VDD=5V VDD=10V VDD=15V VDD=5V VDD=10V VDD=15V VDD=5V VDD=10V VDD=15V VDD=5V VDD=10V VDD=15V 3.5 7.0 11.0 0.52 1.3 3.6 4.95 9.95 14.95 VO=0.5V 或 4.5V,∣IO∣<1µA VO=1.0V 或 9.0V,∣IO∣<1µA VO=1.5V 或 13.5V,∣IO∣<1µA VO=0.5V 或 4.5V,∣IO∣<1µA VO=1.0V 或 9.0V,∣IO∣<1µA VO=1.5V 或 13.5V,∣IO∣<1µA VO=0.4V,VI=0 或 5V

CMOS40、45系列数字集成电路型号功能表

CMOS40、45系列数字集成电路型号功能表4000系列4000 双3输入或非门加1输入反相器4001 四2输入或非门4002 双4输入或非门4006 18位串入串出静态移位寄存器4007 双互补对加反相器4008 4位二进制超前进位全加器4009 六缓冲器/电平变换器(反相)4010 六缓冲器/电平变换器(同相)4011 四2输入与非门4012 双4输入与非门4013 双D型触发器(带预置和清除端)4014 8位串入/并入串出移位寄存器4015 双4位串入并出移位寄存器4016 四双向模拟开关4017 十进制计数/分配器4018 可预置1/N计数器4019 四2选1数据选择器4020 14位二进制串行计数器4021 8位静态移位寄存器4022 八进制计数/分配器4023 三3输入与非门4024 7位二进制串行计数器/分频器4025 三3输入或非门4026 十进制计数/七段译码器4055 BCD—7段液晶显示译码/驱动器4056 BCD—7段液晶显示译码/驱动器4058 双4位锁存器4059 1/N计数器4060 14位二进制串行计数器/分频器4063 4位数值比较器4066 四双向模拟开关4067 单16通道模拟开关4068 8输入与非/与门4069 六反相器4070 四异或门4071 四2输入或门4072 双4输入或门4073 三3输入与门4075 三3输入或门4076 四D型寄存器(三态)4077 四异或非门4078 8输入或非/或门4081 四2输入与门4082 双4输入与门4085 双2路2输入与或非门4086 四2输入与或非门4089 二进制系数乘法器4093 四2输入与非施密特触发器4094 8位移位存贮总线寄存器4095 3输入J—K触发器40194 4位双向通用移位寄存器40195 4位双向通用移位寄存器4500系列4501 双4输入端与非门4502 六反相器/缓冲器4503 六缓冲器(三态)4504 六电平变换器4505 64位静态随机存贮器4506 双2输入可扩展或非门4507 四异或门4508 双4位D锁存器4510 可预置BCD可逆计数器4511 BCD-七段译码器 /驱动器4512 8选1数据选择器4513 BCD-七段译码器 /驱动器4514 4-16线译码器4515 4-16线译码器4516 可预置二进制可逆计数器4517 双64位静态移位寄存器4518 双BCD同步加计数器4519 4位与或选择器4520 双4位二进制同步加计数器4521 24组分频器4522 可预置BCD 同步1/N计数器4526 可预置4位二进制1/N计数器4527 BCD系数乘法器4572 四反相器输入或/与非门4574 四可编程电压比较器4582 超前进位电路4583 双施密特触发器4584 六施密特触发器4585 4位数值比较器4590 单4位锁存器4597 8位总线兼容锁存器(三态)4599 8位可寻址锁存器 4027 双J—K主从触发器4028 BCD十进制译码器4029 4位可预置/可逆计数器4030 四异或门4031 64位静态移位寄存器4032 三串行加法器(同相)4033 十进制计数/七段译码器4034 8位通用总线寄存器4035 4位并入/并出移位寄存器4038 三串行加法器(反相)4040 12位二进制计数器4041 四同相/反相缓冲器4042 四D型锁存器4043 四或非R—S锁存器(三态)4044 四与非R—S锁存器(三态)4045 21位计数器4046 锁相环4047 无稳态/单稳态多谐振荡器4048 8输入多功能门(三态可扩展)4049 六缓冲器/电平变换器(反相)4050 六缓冲器/电平变换器(同相)4051 单8通道模拟开关4052 双4通道模拟开关4053 三2通道模拟开关4054 四段液晶显示驱动4096 3输入J—K触发器4097 双8通道模拟开关4098 双可再触发单稳态触发器4099.8位可寻址锁存器40000系列40100 32级静态左/右移位寄存器40101 9位奇偶发生器/校验器40102 可预置2位十进制减法计数器40103 可预置8位二进制减法计数器40104 4通用双向移位寄存器40105 16×4先入先出寄存器(三态)40106 六施密特触发器(反相)40107 双3输入与非缓冲器/驱动器40108 4×4多路寄存器(三态)40109 四电平变换器40110 十进制计数/锁存/译码/驱动40147 10~4线BCD优先编码器40160 可预置十进制计数器40161 可预置二进制计数器40162 可预置十进制计数器40163 可预置4位二进制计数器40174 六D型触发器40175 四D触发器40181 4位算术逻辑单元40182 超前进位发生器40192 可预置十进制可逆计数器40193 可预置二进制可逆计数器4528 双可重触发单稳态触发器4529 双四通道模拟开关4530 双5输入过半数逻辑门4531 12位奇偶校验器4532 8位优先编码器4534 实时五、十进制计数器4536 可编程定时器4538 双精密可重触发单稳态触发器4539 双4通道数选择器4541 可编程定时器4543 BCD-七段译码器 /驱动器4544 BCD-七段译码器 /驱动器4547 BCD-译码/大流动驱动器4549 近似函数寄存器4551 四2通道模拟开关4553 三数字BCD计数器4555 双4选1译码器4556 双4选1译码器4557 1-64位可变长度移位寄存器4558 BCD-七段译码器4559 近似函数寄存器4560 “N”BCD加法器4561 “9”求补器4562 128位静态移位寄存器4566 工业定时基准发生器4568 相位比较器和可编程计数器4569 双可预置BCD/二进计数器。

一种全电子多路音频切换器

一种全电子多路音频切换器全电子音频切换器方框图整个电原理图如图2所示。

时钟电路以IC;(CD4011一4个2输入端与非门)所构成,它是一个产生10kHz方波的振荡器。

当IC,一。

的脚2是逻辑高电平时,产生时钟,当脚2是逻辑低电平时,时钟停止。

当时钟作用时,由ICZ(CD4017一CMOS 计数器)和输入选择开关所构成的键盘编码器将顺序输出逻辑高电平。

清零端(ICZ的脚15)连接到最后一个输出端(ICZ的脚11),当最后这个输出端被选择时,ICZ的其余输出全部被清零,并重新从第一个输出端开始顺序输出高电平。

IC:的9个输出端通过Dl一D。

(二极管)连接到键盘开关上。

这些二极管用来防止某条输出线上的逻辑高电平反馈到逻辑低电平线上。

尽管每次只有一个开关被压下,但仍然要防止错误出现,例如有时会出现两个开关被压下的情况。

当某个输人选择开关被压下时,所选择的逻辑高电平会反馈到ICZ的输入端脚13,并通过反相器ICI一c传送到振荡器的门电路控制端(ICI一。

的脚2)。

只要一个开关保持压下状态,被选择的ICZ输出端就保持在高电平状态。

当开关复位时,振荡器开始工作,ICZ的输出端又开始顺序处于高电平状态。

有业余演唱。

有影视录象中的卡拉OK演唱,也有舞台演出中的卡拉OK演唱。

有歌厅即兴演唱,也有家庭娱乐演唱。

由于卡拉OK不仅可以视听欣赏,还可以主动参与演唱,使影视艺术和舞台艺术同时进人了家庭。

最初卡拉OK伴唱机只是播放伴奏音乐带并同时输入演唱歌声,后来发展为不仅能利用伴奏录音带,而且还能够利用唱片、录象带、视盘等播放伴唱音乐和图象。

目前卡拉OK伴唱机已是一种具有高保真音乐和高清晰图象的音频设备并采用数字混响器改善演唱音质,美化电声技术10/1996声音和模拟回声效果等,有些则设置了歌声对消器、变调器和自动伴唱功能形成专用声频系统,并且操作方便,例如多功能卡拉OK伴唱机。

朱维仲.电声设备原理及维修.北京兵器工业出版社,1995一种全电子多路音频切换器王惠民随着我国经济建设的不断发展,物质生活水平的不断提高,扩声系统越来越多地应用于车站、机场、码头、宾馆、大型商场和体育场馆等公共场所。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

October 1987

Revised January 1999

CD4001BC/CD4011BC Quad 2-Input NOR Buffered B Series Gate

• Quad 2-Input NAND Buffered B Series Gate © 1999 Fairchild Semiconductor Corporation DS005939.prf CD4001BC/CD4011BC

Quad 2-Input NOR Buffered B Series Gate •

Quad 2-Input NAND Buffered B Series Gate

General Description

The CD4001BC and CD4011BC quad gates are monolithic

complementary MOS (CMOS) integrated circuits con-

structed with N- and P-channel enhancement mode tran-

sistors. They have equal source and sink current

capabilities and conform to standard B series output drive.

The devices also have buffered outputs which improve

transfer characteristics by providing very high gain.

All inputs are protected against static discharge with diodes

to V DD and V SS.

Features

s Low power TTL:

Fan out of 2 driving 74L compatibility:or 1 driving 74LS

s5V–10V–15V parametric ratings

s Symmetrical output characteristics

s Maximum input leakage 1 µA at 15V over full

temperature range

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagrams

Pin Assignments for DIP, SOIC and SOP

CD4001BC

Top View

Pin Assignments for DIP and SOIC

CD4011BC

Top View

Order Number Package Number Package Description

CD4001BCM M14A14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow

CD4001BCSJ M14D14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

CD4001BCN N14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

CD4011BCM M14A14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow

CD4011BCN N14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide。