湖南工业大学实验报告

湖南工业大学学生实习报告

湖南工业大学学生实习报告大一第二学期的第十七周,我们商学院工管六七八九班一起参加了认识实习。

虽然实习仅有一个星期,时间不长,但留给我们的印象、以及经验认识却是极其丰富的。

我觉得,学习是相当注重实际经验的,更何况作为一名工商管理大类的学生,经验对我们来说就更加重要了。

一周以来,我始终怀着兴奋的心情,认真的观看视频资料、回味老师的讲座、参观金德管业、考察步步高国安店的大二实习生,这使我对本专业的认识进一步加强,也使我对今后工作的选择有了初步的认识。

相信不断积累的经验会让我走得更成功。

下面就是我本次实习的具体行程和体会。

首先,实习地点及日程安排。

6月4日观看《赢在中国》节目和听罗瑞雪教授的励志讲座。

6月5日观看前一天未完的《赢在中国》节目。

6月6日老师带领我们参观金德管业工业园区。

6月7日和同学去步步高国安店考察大二的学长学姐们的实习情况。

6月8日继续考察,并与同学交流心得与体会。

再者,实习的目的。

我记得《赢在中国》中,作为评委的“今日资本”总裁徐新说过,《赢在中国》这个比赛就是考察选手们的意志、毅力与坚强力。

观我们这次的认识实习,我觉得倒是没有那么深,认识实习的主要任务就是针对我们所学的专业(当然,这次是营销专业带队的),具体结合实习学生的情况,增加我们的经验。

经验是我们踏入社会必不可少的一项。

通过一周的认识实习,可使我们对所学专业更加了解,增强感性意识。

认识实习也是培养学生学习兴趣的过程,培养实践能力,达到学院培养应用型人才的培养目标的重要教学过程。

再来是这一周具体的实习过程及内容。

6月4日上午和6月5日上午观看的《赢在中国》视频,是中央电视台cctv2的一档全国性商战真人秀节目,大型的励志创业电视活动。

获胜者可以获得企业提供的一大笔风险投资。

我们观看的是第一赛季12强的竞争,前5名获得者依次为宋文明、周宇、周瑾、任春雷、吴志祥,联通世界风通行证获得者是浦滨——一个长得不错的帅小伙。

《赢在中国》是一个展示人才,选拔优秀创业人才的好栏目。

湖南工业大学认识实习报告

湖南工业大学学生实习总结报告实习性质:认识实习院(系):包装与材料工程学院专业:印刷工程班级:姓名:认识实习在6月24日于包印教学楼109正式拉开了帷幕。

为期两周的实习,我们都抱着万分期待的心情。

认识实习是将我们在印刷概论上所学习的理论知识实践化。

同时开阔视野,完善自己的知识结构,对凸版、平版、凹版、孔版等印刷方式的设备、材料、工艺有一个基本了解,对书本知识有一个从理论到实践的认知过程。

为以后专业课程的学习打下基础。

这也是让我们对印刷专业形成一个客观理性的认识。

所以我们都很重视这次实习。

在实习开始的第一天,我们召开了印刷系的动员大会。

钟云飞老师对实习安排,实习内容以及实习的注意事项进行了介绍。

在动员大会的最后,黄新国老师给大家带来的最新的印刷相关知识,黄老师给我们总结了在德国开展有着“印刷界奥运会”的德鲁巴会展核心内容。

如未来整个印刷行业的主要市场都集中在包装印刷。

印刷趋向数字化等等。

而我们的实习也大致分为了校内实习和校外实习两个部分。

接下来的4天我们在校内实习,我们在印刷系专业的老师的带领下,参观了各个实验室。

我们最先参观的是包印实验楼216,在这个实验室里主要包括了印前输入、色彩管理和印刷模拟系统。

这中间我最感兴趣的是印刷模拟系统的操作,希望将来有机会也很像学姐一样去参加比赛。

CTP输出,苹果机房、材料与试性这些在印刷概论上出现的知识在现实中更加具体的展现出来。

来到苹果机房时大家感叹:“这就是传说中的苹果机房啊!”看到苹果机的键盘和鼠标时,感受到它和普通电脑不同!苹果机在图像处理方面有很强大的功能,所以苹果机很适合印前处理;我们都在现场练习,摸索着苹果机的强大之处!同时我觉得实习过程中要多了解些知识,就对此进行了一定的了解,比如苹果机在3Dmax软件上渲染输出比较快,苹果机虽然贵,可是它的价格决定它的价值!CTP输出简化了工序,提高了效率,节约成本。

我们参观了那里的一台CTP机,也就是计算机直接制版机。

湖南工业大学单片机实验报告

单片机实验报告学生姓名刘宝雨班级测控1002班学号10401600244电气与信息工程学院2012年12 月20 日软件实验一存储器读写一、实验目的:1、掌握寄存器、存储器读写等汇编指令;2、掌握编程软件编辑、编译、调试等基本操作;3、学习简单程序的基本调试方法。

二、实验内容:将70H-7FH16个字节单元的数据复制到片外存储器2000H开始的地址单元中.程序清单如下:ORG 0000H;伪指令,程序入口SJMP START;段转移指令,转移到START执行ORG 0030H;伪指令,START的入口START: MOV R1,10H ;一共16个数据MOV R0,#70H ;原数据首地址MOV DPTR,#2000H; 片外存储单元首地址MOV 70H,#00H;送入原始数据,把70H-71H中分别送入00H-0FHMOV 71H,#01HMOV 72H,#02HMOV 73H,#03HMOV 74H,#04HMOV 75H,#05HMOV 76H,#06HMOV 77H,#07H;MOV 78H,#08HMOV 79H,#09HMOV 7AH,#0AHMOV 7BH,#0BHMOV 7CH,#0CHMOV 7DH,#0DHMOV 7EH,#0EHMOV 7FH,#0FHLOOP: MOV A,@R0;循环送入2000H-200FHMOVX @DPTR,A;执行片外将累加器A中的数据送到数据指针DPTRINC R0;R0中的数据自加一INC DPTR;DPTR中的数据自加一DJNZ R1,LOOP;R1=1,程序继续执行,R1不等于0,程序转移到LOOPEND;程序结束MOV R1,#10H;将立即数10H送到间接锁存器R1MOV R0,#70H;将立即数70H送到间接锁存器R0MOV DPTR,#2000H;将立即数2000H送到数据锁存器DPTR三、上机运行结果软件实验二数据排序实验一、实验目的熟悉单片机汇编指令系统,掌握汇编程序设计方法。

湖南工业大学电自专业89s51单片机实验报告(DOC)

实验一二进制转换成十进制实验一、实验设备1.THGQC-1型嵌入式单片机实验开发系统-套。

2.PC机一台。

二、实验目的掌握汇编语言设计和实验步骤,熟悉在KEIL环境下观察内部RAM 的方法。

三、实验内容单片机中的数值有各种表达方式,这是单片机的基础。

掌握各种数制之间的转换是一种基本功。

本实验内容是将一个给定的一字节二进制数,通过编程将其转换成十进制码。

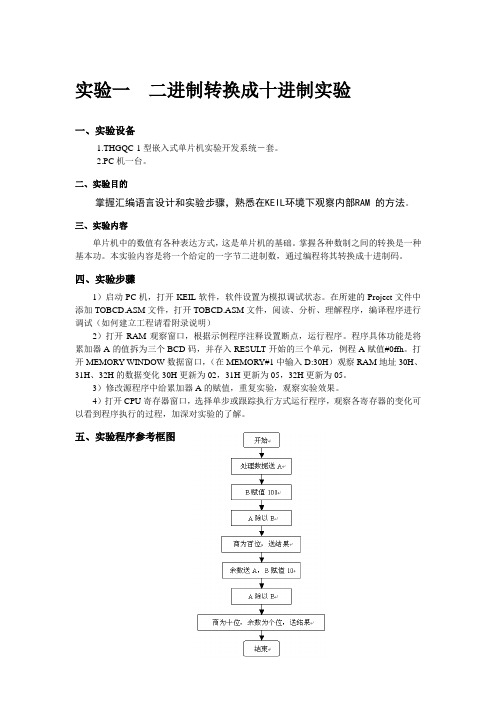

四、实验步骤1)启动PC机,打开KEIL软件,软件设置为模拟调试状态。

在所建的Project文件中添加TOBCD.ASM文件,打开TOBCD.ASM文件,阅读、分析、理解程序,编译程序进行调试(如何建立工程请看附录说明)2)打开RAM观察窗口,根据示例程序注释设置断点,运行程序。

程序具体功能是将累加器A的值拆为三个BCD码,并存入RESULT开始的三个单元,例程A赋值#0ffh。

打开MEMORY WINDOW数据窗口,(在MEMORY#1中输入D:30H)观察RAM地址30H、31H、32H的数据变化30H更新为02,31H更新为05,32H更新为05。

3)修改源程序中给累加器A的赋值,重复实验,观察实验效果。

4)打开CPU寄存器窗口,选择单步或跟踪执行方式运行程序,观察各寄存器的变化可以看到程序执行的过程,加深对实验的了解。

五、实验程序参考框图六、实验程序RESULT EQU 30HORG 0000HJMP STARTORG 0100HSTART:MOV SP,#40HMOV A,#0FFHCALL BINTOBCDNOP ;此处设置断点,察看RAM 30H,31H,32HLJMP $BINTOBCD:MOV B,#100DIV ABMOV RESULT,A ;除以100得百位数MOV A,BMOV B,#10DIV ABMOV RESULT+1,A ;余数除以10得十位数MOV RESULT+2,B ;余数为个位数RETEND七.实验程序编译和结果分析图1为keil2程序编辑器的编译窗口。

湖南工业大学计算机控制实验报告.

《计算机控制技术》实验报告学生姓名 刘宝雨 班级 测控1002班 学号10401600244电气与信息工程学院 2013年 4 月 20 日实验一 A/D、D/A转换实验实验1.1 A/D、D/A转换实验(1)1.实验线路原理图:见图1—1图1-1CPU的DPCLK信号与ADC0809单元电路的CLOCK相连作为ADC0809的时钟信号。

ADC0809芯片输入选通地址码A、B、C为“1”状态,选通输入通道IN7。

通过电位器W41给A/D变换器输入-5V~+5V的模拟电压。

8253的2#口用于5ms定时输出OUT2信号启动A/D变换器。

由8255口A为输入方式。

A/D转换的数据通过A口采入计算机,送到显示器上显示,并由数据总线送到D/A变换器0832的输入端。

选用CPU的地址输入信号IOY0为片选信号(CS),XIOW信号为写入信号(WR),D/A变换器的口地址为00H。

调节W41即可改变输入电压,可从显示器上看A/D变换器对应输出的数码,同时这个数码也是D/A变换器的输入数码。

2.A/D、D/A转换程序流程:(见图1—2)对应下面的流程,我们已编好了程序放在CPU的监控中,可用U(反汇编)命令查看。

而且已将所有控制程序放在光盘中,供教师参考,当然对于学生来说,应让其自己编写调试。

图1-23.实验内容及步骤(1)按图1—1接线。

用“短路块”分别将U1单元中的ST与+5V 短接,U4单元中的X与+5V,Z与-5V短接。

其它画“●”的线需自行连接。

示波器的CH1通道接U15单元的OUT端,连接好后,接通电源。

(2)对U15 D/A转换单元进行调零。

按下实验箱上的复位键,在调试窗口中出现“WELCOME TO YOU”后,输入如下(参照图1-3):A2000 按“Enter”键0000:2000 MOV AL,80 按“Enter”键0000:2002 OUT 00,AL 按“Enter”键0000:2004 INT 按“Enter”键0000:2005 按“Enter”键G=0000:2000 按“Enter”键待输入完成后,用U16单元电压表毫伏档监测U15 D/A转换单元OUT端电压,调节U15单元103电位器使电压表显示“00”。

湖南工业大学ARM实验报告

ARM嵌入式系统原理及应用开发实验报告学院:电气与信息工程学院班级:电子信息1204指导老师:谭会生姓名:学号:实验一:ARM汇编指令使用实验——基本数学/逻辑运算一、实验目的1.初步学会使用ARM ADS / Embest IDE for ARM 开发环境及ARM软件模拟器。

2.通过实验掌握数据传送和基本数学/逻辑运算的ARM汇编指令的使用方法。

二、实验设备1.硬件:PC机。

2.软件:ADS 1.2 / Embest IDE 200X集成开发环境。

三、实验内容熟悉ADS 1.2 / Embest IDE 200X开发环境的使用,使用LDR/STR和MOV等指令访问寄存器或存储单元,实现数据的加法运算。

具体实验参考程序如下:四.实验操作步骤1.新建工程。

先建立一个实验文件夹,如E\ARMSY\armasm1;然后运行Embest IDE 集成开发环境,选择File→New Workspace菜单项,弹出一个对话框,输入工程名armasm1a/armasmlb等相关内容;最后单击OK按钮,将创建一个新工程,并同时创建一个与工程名相同的工作区。

此时在工作区窗口将能打开该工作区和工程。

2.建立源文件。

选择File→New菜单项,弹出一个新的、没有标题的文本编辑窗口,输入光标位于窗口中第一行,按照实验参考程序编辑输入源文件代码。

编辑完后,保存文件armasmla. s。

1)armasmla. s源程序:/* armasm1a.s */.EQU X, 45 /*定义变量X,并赋值为45*/.EQU Y, 64 /*定义变量Y,并赋值为64*/.EQU STACK_TOP, 0X1000 /*定义栈顶0X1000*/.GLOBAL _START.TEXT_START: /*程序代码开始标志*/MOV SP, #STACK_TOPMOV R0, #X /*X的值放入R0*/STR R0, [SP] /*R0的值保存到堆栈*/MOV R0, #Y /*Y的值放入R0*/LDR R1, [SP] /*取堆栈中的数到R1*/ADD R0, R0, R1STR R0, [SP]STOP: B STOP /*程序结束,进入死循环*/.END2).使用ADD/SUB/LSL/LSR/AND/ORR等指令,完成基本数学/逻辑运算。

湖南工业大学EDA实验数字频率计实验报告

EDA技术与应用实验报告学院:电气与信息工程学院班级:电子信息1203指导老师:谭会生老师姓名:潘伟学号:124017200209实验四:数字频率计的设计一.实验目的(1)熟悉artus I/ISE Suite/ispLEVNRI软件的基本使用方法。

(2)熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。

(3)学习VHDL程序中数据对象、数据类型、顺序语句和并行语句的综合使用。

二.实验条件与要求(1)开发软件:Quartus II 9.0(2)实验设备:PC、GW48-CK EDA实验开发系统。

(3)画出系统的原理框图,说明系统中各个主要功能、编写各个VHDL源程序。

画出输入信号波形并调试和仿真。

三.实验内容设计并调试好八位十进制数字频率计,用GW48-CK实验开发系统进行硬件验证(实现应选择拟采用的实验芯片的型号)进行硬件验证。

四.实验设计电路原理图(1)VHDL源程序1、8位可自加载加法计数器的源程序CNT10.VHD如下--CNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CNT10 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;CQ:OUT INTEGER RANGE 0 TO 15;CO:OUT STD_LOGIC);END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI:INTEGER RANGE 0 TO 15;BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR='1'THEN CQI<=0;ELSIF CLK'EVENT AND CLK='1'THENIF ENA='1'THENIF CQI<9 THEN CQI<=CQI+1;ELSE CQI<=0;END IF;END IF;END IF;END PROCESS;PROCESS(CQI) ISBEGINIF CQI=9 THEN CO<='1';ELSE CO<='0';END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;2、32位锁存器的源程序REG32B.VHD如下:--REG32B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B ISPORT(LOAD:IN STD_LOGIC;DIN:IN STD_LOGIC_VECTOR(31DOWNTO 0);DOUT:OUT STD_LOGIC_VECTOR(31DOWNTO 0));END ENTITY REG32B;ARCHITECTURE ART OF REG32B ISBEGINPROCESS(LOAD,DIN) ISBEGINIF(LOAD'EVENT AND LOAD='1')THENDOUT<=DIN;END IF;END PROCESS;END ARCHITECTURE ART;3、测频信号控制发生器源程序TESTCLTL.VHD如下:--TESTCTL.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TESTCTL ISPORT(CLK:IN STD_LOGIC;TSTEN:OUT STD_LOGIC;CLR_CNT:OUT STD_LOGIC;LOAD:OUT STD_LOGIC);END ENTITY TESTCTL;ARCHITECTURE ART OF TESTCTL ISSIGNAL DIV2CLK:STD_LOGIC;BEGINPROCESS(CLK)ISBEGINIF CLK'EVENT AND CLK='1'THENDIV2CLK<=NOT DIV2CLK;END IF;END PROCESS;PROCESS(CLK,DIV2CLK) ISBEGINIF CLK='0' AND DIV2CLK='0'THENCLR_CNT<='1';ELSE CLR_CNT<='0';END IF;END PROCESS;LOAD<=NOT DIV2CLK;TSTEN<=DIV2CLK;END ARCHITECTURE ART;4、动态扫描程序如下:--CTRLS.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CTRLS ISPORT(CLK: IN STD_LOGIC;SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END ENTITY CTRLS;ARCHITECTURE ART OF CTRLS ISSIGNAL CNT:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINPROCESS(CLK) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CNT="111" THENCNT<="000";ELSECNT<=CNT+'1';END IF;END IF;END PROCESS;SEL<=CNT;END ARCHITECTURE ART;--DISPLAY.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DISPLAY ISPORT( SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);DATAIN: IN STD_LOGIC_VECTOR(31 DOWNTO 0);COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--LEDW: OUT STD_LOGIC_VECTOR(2 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END ENTITY DISPLAY;ARCHITECTURE ART OF DISPLAY ISSIGNAL DATA: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINP1:PROCESS(SEL) ISBEGINCASE SEL ISWHEN"000"=>COM<="11111110";WHEN"001"=>COM<="11111101";WHEN"010"=>COM<="11111011";WHEN"011"=>COM<="11110111";WHEN"100"=>COM<="11101111";WHEN"101"=>COM<="11011111";WHEN"110"=>COM<="10111111";WHEN"111"=>COM<="01111111";WHEN OTHERS=>COM<="11111111";END CASE;END PROCESS P1;--LEDW<=SEL;P2:PROCESS(SEL)BEGINCASE SEL ISWHEN"000"=>DATA<=DA TAIN(3 DOWNTO 0);WHEN"001"=>DATA<=DA TAIN(7 DOWNTO 4);WHEN"010"=>DATA<=DA TAIN(11 DOWNTO 8);WHEN"011"=>DATA<=DATAIN(15 DOWNTO 12);WHEN"100"=>DATA<=DA TAIN(19 DOWNTO 16);WHEN"101"=>DATA<=DA TAIN(23 DOWNTO 20);WHEN"110"=>DATA<=DATAIN(27 DOWNTO 24);WHEN"111"=>DATA<=DA TAIN(31 DOWNTO 28);WHEN OTHERS=>DATA<="0000";END CASE;CASE DATA ISWHEN"0000"=>SEG<="00111111";WHEN"0001"=>SEG<="00000110";WHEN"0010"=>SEG<="01011011";WHEN"0011"=>SEG<="01001111";WHEN"0100"=>SEG<="01100110";WHEN"0101"=>SEG<="01101101";WHEN"0110"=>SEG<="01111101";WHEN"0111"=>SEG<="00000111";WHEN"1000"=>SEG<="01111111";WHEN"1001"=>SEG<="01101111";WHEN OTHERS=>SEG<="00000000";END CASE;END PROCESS P2;END ARCHITECTURE ART;5、分频器程序如下:--CLKGEN.VHD--3MHZ TO 100HZLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CLKGEN ISPORT(CLK_IN: IN STD_LOGIC;RESET: IN STD_LOGIC;CLK_OUT: OUT STD_LOGIC );END ENTITY CLKGEN;ARCHITECTURE ART OF CLKGEN IS--SIGNAL CNT: INTEGER RANGE 0 TO 10#49999999#; CONSTANT DIVIDE_PERIOD:INTEGER:=50000000;-- SIGNAL CNT: INTEGER RANGE 0 TO 10#29#; BEGINPROCESS(CLK_IN,RESET) ISV ARIABLE CNT:INTEGER RANGE 0 TO 49999999;BEGINIF(RESET='1')THENCNT :=0;CLK_OUT<='0';ELSIF RISING_EDGE(CLK_IN) THENIF(CNT<(DIVIDE_PERIOD/2)) THENCLK_OUT<='1';CNT:=CNT+1;ELSIF(CNT<(DIVIDE_PERIOD-1)) THENCLK_OUT<='0';CNT:=CNT+1;ELSECNT:=0;END IF;END IF;END PROCESS DIVIDE_CLK;END ARCHITECTURE ART;6、数字频率计的源程序如下:--dtFREQ.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;--USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY dtFREQ ISPORT(FSIN: IN STD_LOGIC;--5ns\10ns\5nsCLK: IN STD_LOGIC;--500nsCLK2:IN STD_LOGIC;RESET: IN STD_LOGIC;-- CLK2:IN STD_LOGIC;--CLK2:BUFFER STD_LOGIC;--500ns-- DOUT: OUT STD_LOGIC_VECTOR(31 DOWNTO 0);--DOUT: OUT STD_LOGIC_VECTOR(31 DOWNTO 0);--SEG1: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--COM1: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));-- SD: OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); END ENTITY dtFREQ;ARCHITECTURE ART OF dtFREQ IS--CNT10COMPONENT CNT10 ISPORT(CLK, CLR, ENA: IN STD_LOGIC;CQ: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO: OUT STD_LOGIC);END COMPONENT CNT10;--REG32BCOMPONENT REG32B ISPORT(LOAD: IN STD_LOGIC;DIN: IN STD_LOGIC_VECTOR(31 DOWNTO 0);DOUT: OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); END COMPONENT REG32B;--TESTCTLCOMPONENT TESTCTL ISPORT(CLK: IN STD_LOGIC;TSTEN: OUT STD_LOGIC;CLR_CNT: OUT STD_LOGIC;LOAD: OUT STD_LOGIC);END COMPONENT TESTCTL;--CLKGENCOMPONENT CLKGEN ISPORT(CLK_IN: IN STD_LOGIC;RESET: IN STD_LOGIC;CLK_OUT: OUT STD_LOGIC );END COMPONENT CLKGEN;--CTRLSCOMPONENT CTRLS ISPORT(CLK: IN STD_LOGIC;SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END COMPONENT CTRLS;--DISPLAYCOMPONENT DISPLAY ISPORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);DATAIN: IN STD_LOGIC_VECTOR(31 DOWNTO 0);COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT DISPLAY;SIGNAL SE,SC,SL,CLK1:STD_LOGIC;SIGNAL S0,S1,S2,S3,S4,S5,S6,S7,S8:STD_LOGIC;SIGNAL SD,DOUT:STD_LOGIC_VECTOR(31 DOWNTO 0);-- SIGNAL SB:STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL SEL:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINU0:CLKGEN PORT MAP(CLK,RESET,CLK1);U1:TESTCTL PORT MAP(CLK=>CLK1,TSTEN=>SE, CLR_CNT=>SC, LOAD=>SL);U2:CNT10 PORT MAP(CLK=>FSIN, CLR=>SC, ENA=>SE, CQ=>SD(3 DOWNTO 0),CO=>S1);U3:CNT10 PORT MAP(CLK=>S1, CLR=>SC, ENA=>SE, CQ=>SD(7 DOWNTO 4),CO=>S2);U4:CNT10 PORT MAP(S2, SC, SE, SD(11 DOWNTO 8),S3);U5:CNT10 PORT MAP(S3, SC, SE, SD(15 DOWNTO 12),S4);U6:CNT10 PORT MAP(S4, SC, SE, SD(19 DOWNTO 16),S5);U7:CNT10 PORT MAP(S5, SC, SE, SD(23 DOWNTO 20),S6);U8:CNT10 PORT MAP(S6, SC, SE, SD(27 DOWNTO 24),S7);U9:CNT10 PORT MAP(S7, SC, SE, SD(31 DOWNTO 28),S8);U10:REG32B PORT MAP(LOAD=>SL, DIN=>SD, DOUT=>DOUT);--U10:CLKGEN PORT MAP(CLK1,S0);-- U11:CLKGEN PORT MAP(CLK2,CLK3);U11:CTRLS PORT MAP(CLK2,SEL);U12:DISPLAY PORT MAP(SEL,DOUT,COM(7 DOWNTO 0),SEG(7 DOWNTO 0));END ARCHITECTURE ART;五、仿真图如下:CNT10仿真图FREQ仿真图动态仿真图六、RTL视图如下:CNT10的RTL视图FREQ的RTL视图七、管脚锁定如图:八、实物数据如下图:6.实验总结本次实验实在是遇到了不少的麻烦。

实验二、液体饱和蒸汽压测定实验报告样例

湖南工业大学实验报告实验二液体饱和蒸气压的测定学生姓名预习实验报告内容一、实验目的1、学会用等压计测定在不同温度下乙醇的饱和蒸汽压;2、学会由图解法求乙醇的平均摩尔汽化热和正常沸点;3、掌握用等压法测定液体饱和蒸汽压的原理。

二、实验仪器仪器:恒温槽一套,DP—AF 饱和蒸汽压实验组合装置一套,真空泵,试剂:A.R.无水乙醇三、实验原理在一定温度下,纯液体与其气相达成平衡时的压力,称为该温度下液体的饱和蒸汽压。

饱和蒸汽压与温度的关系可用克劳修斯—克拉贝龙方程式来表示。

2*m*dln RT H dT p vap ∆=(2.1)*mH vap ∆为温度T 时液体的摩尔蒸发热,R 为气体常数,T 为绝对温度。

在一定温度变化范围内,*m H vap ∆可视为常数,可当作平均摩尔汽化热。

将上式积分得:'*ln C RTH p mvap +∆−=∗(2.2)或C TA p +=∗lg (2.3)式(2.3)中的C 为积分常数。

由(2.3)式可知lgp 与1/T 是直线关系,直线的斜率RH A mvap 303.2*∆−=,因此可求出*m H vap ∆。

若将lgp 对1/T 作图应得一直线,斜率为负值。

直线斜率RH A m mvap 303.2*∆−=−=。

由此得到:RmH m vap 303.2*−=∆(2.4)这就可以由图解法先求得斜率m ,然后再由(2.4)式计算出摩尔汽化热8m vap H ∆。

本实验用静态法测定乙醇在不同温度下的饱和蒸汽压,所用仪器是纯液体蒸汽压测定装置。

系统气液两相平衡的温度称为液体在此外压力下的沸点。

用当时的大气压减去数字压力计上的压力。

即为该温度下液体的饱和蒸汽压。

当外压是1大气压时,液体的蒸汽压与外压相等时的温度,叫做该液体的正常沸点。

四、实验步骤1、按图2-1用橡胶管将各仪器连接成饱和蒸气压的实验装置。

图2-1饱和蒸气压系统装置示意图2、取下等位计,向加料口注入乙醇。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告学年学期:-- 学年第学期课程名称:

指导老师:

学院(部):

班级:

学号:

姓名:

实验报告

第周实验名称

实验性质实验类型

实验课时实验日期、时间

实验消耗器材

实验仪器设备

实验目的

实验内容(实验原理、运用的理论知识和数据、算法、程序、步骤和方法)

实验内容(实验原理、运用的理论知识和数据、算法、程序、步骤和方法)

实验内容(实验原理、运用的理论知识和数据、算法、程序、步骤和方法)

实验内容(实验原理、运用的理论知识和数据、算法、程序、步骤和方法)

实验内容(实验原理、运用的理论知识和数据、算法、程序、步骤和方法)

实验报告

第周实验名称

实验性质实验类型

实验课时实验日期、时间

实验消耗器材

实验仪器设备

实验目的

实验内容(实验原理、运用的理论知识和数据、算法、程序、步骤和方法)

实验报告

第周实验名称

实验性质实验类型

实验课时实验日期、时间

实验消耗器材

实验仪器设备

实验目的

实验报告

第周实验名称

实验性质实验类型

实验课时实验日期、时间

实验消耗器材

实验仪器设备

实验目的。