VerilogHDL设计同步模10计数器

VerilogHDL十进制计数器实验Quartus非常详细的步骤

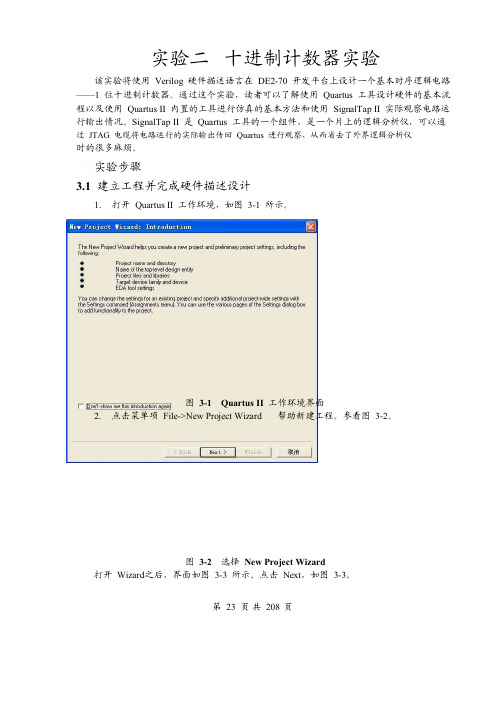

实验二十进制计数器实验该实验将使用Verilog 硬件描述语言在DE2-70 开发平台上设计一个基本时序逻辑电路——1 位十进制计数器。

通过这个实验,读者可以了解使用Quartus 工具设计硬件的基本流程以及使用Quartus II 内置的工具进行仿真的基本方法和使用SignalTap II 实际观察电路运行输出情况。

SignalTap II 是Quartus 工具的一个组件,是一个片上的逻辑分析仪,可以通过JTAG 电缆将电路运行的实际输出传回Quartus 进行观察,从而省去了外界逻辑分析仪时的很多麻烦。

实验步骤3.1建立工程并完成硬件描述设计1. 打开Quartus II 工作环境,如图3-1 所示。

图3-1 Quartus II工作环境界面2. 点击菜单项File->New Project Wizard 帮助新建工程。

参看图3-2。

图3-2 选择New Project Wizard打开Wizard 之后,界面如图3-3 所示。

点击Next,如图3-3。

第23 页共208 页图3-3 New Project Wizard界面3. 输入工程工作路径、工程文件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层实体名都是Counter10,输入结束后,如图3-4 所示。

点击Next。

图3-4输入设计工程信息4. 添加设计文件。

界面如图3-5 所示。

如果用户之前已经有设计文件(比如.v 文件)。

第24 页共208 页那么再次添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑设计文件。

图3-5添加设计文件5. 选择设计所用器件。

由于本次实验使用Altera 公司提供的DE2-70 开发板,用户必须选择与DE2-70 开发板相对应的FPGA 器件型号。

在Family 菜单中选择Cyclone II,Package 选FBGA,Pin Count 选896,Speed grade 选6,确认Available devices 中选中EP2C70F896C6,如图3-6。

Verilog— 同步计数器

西安邮电學院基于Verilog的HDL设计基础实验报告系部名称:通信与信息工程学院学生姓名:专业名称:通信工程班级:学号:时间:2010年12月11日实验题目同步计数器一、实验内容对使用JK主从触发器来设计的同步计数器的设计与验证;再对其进行综合生成网表文件;然后进行后仿真。

二、技术规范输入引脚:j,k,clock,clear;输出引脚:Q,Qbar。

技术规范: 前面是JK主从触发器,后边是基本触发器,JK主从触发器在clear和clock控制下变化,而输出Q跟随主触发器的变化而变化。

三、实验步骤1、在modulesim软件中进行JK主从触发器来设计的同步计数器的设计与验证,直到运行结果全部正确;2、在Quartus软件中对刚刚完成的计数器进行综合,生成网表文件;3、在modulesim软件中对计数器进行进行后仿真。

四、源代码1:设计模块:module counter(j,k,clock,clear,q,qbar);output [3:0] q,qbar;input clock,clear;input j,k;wire a,b,y,ybar,c,cbar,d;assign cbar = ~clock;assign a = ~(j & clear & clock & qbar),b = ~(k & clock & q),y = ~(a & ybar),ybar = ~(clear & b & y),c = ~(y & cbar),c = ~(ybar & cbar);assign q = ~(c & qbar),qbar = ~(d & clear & q);endmodule2:激励模块module simulate;reg clock,clear;reg j,k;wire[3:0] q,qbar;initial$monitor ($time,"Clear=%b,j=%b,k=%b,q=%b\n",clear,j,k,q); counter co(j,k,clock,clear,q,qbar);initialbeginclear=1'b1;j= 1'b1; k= 1'b1;#30 clear=1'b0;j= 1'b0; k= 1'b1;#40 clear=1'b1;j= 1'b1; k= 1'b0;#50 clear=1'b0;j= 1'b0; k= 1'b0;endinitialbeginclock=1'b0;forever #10 clock=~clock;endinitialbegin#500 $finish;endendmodule五、仿真结果及分析五、调试情况,设计技巧及体会1、程序调试:程序一开始设计完毕时出现错误,检查到小问题修改后,运行成功。

Verilog10进制计数器电路

练习设计一个10进制计数器电路,把10进制计数器的计数结果送到一位数码管显示,要求计数器的计数频率为1Hz。

系统时钟为25MHz,要求系统同步复位,高电平有效。

完成电路设计框图,各模块仿真以及系统功能仿真和下载编程。

分频器:module fenpin25(clk,rst,clk_1hz);input clk;input rst;output clk_1hz;reg clk_1hz;reg [23:0] cnt;always@(posedge clk or posedge rst)beginif(rst==1'b1)cnt<=24'd0;else if(cnt==13107119)begincnt<=24'd0;clk_1hz<=~clk_1hz;endelsecnt<=cnt+1;endendmodule十进制计数器:module cnt10(rst,clk,cnt);input rst,clk;output [3:0] c nt;reg [3:0] c nt;always@(posedge clk)beginif(rst==1'b0)cnt<=4'b000;else if(cnt==4'd9)cnt<=4'b000;elsecnt<=cnt+1;endendmodule十进制计数器仿真波形图:LED译码器:module qiduan(cnt,led,scan); input [3:0] c nt;output [6:0] l ed;output [3:0] s can;reg [6:0] l ed;wire [3:0] s can;assign scan=4'b0001;always@(cnt)begincase(cnt)4'b0001:led=7'b0000110;4'b0010:led=7'b1011011;4'b0011:led=7'b1001111;4'b0100:led=7'b1100110;4'b0101:led=7'b1101101;4'b0110:led=7'b1111100;4'b0111:led=7'b0000111;4'b1000:led=7'b1111111;4'b1001:led=7'b1101111;4'b1010:led=7'b1110111;default:led=7'b0111111;endcaseendendmoduleLED译码器仿真波形图:顶层电路Verilog HDL代码:module cnt10led(rst,clk,led,scan);input rst;input clk;output [6:0] l ed;output [3:0] s can;wire [3:0] c nt;wire [6:0] l ed;wire [3:0] s can;fenpin25 u0(.clk(clk),.rst(rst),.clk_1hz(clk_1hz)); cnt10 u1(.clk(clk_1hz),.rst(rst),.cnt(cnt)); qiduan u2(.cnt(cnt),.led(led),.scan(scan));endmodule框图:。

实验四-模10计数器与10分频电路

●实验名称:利用VerilogHDL设计一个模10加法计数器和一个时钟10分频电路●实验目的:1.熟悉用可编程器件实现基本时序逻辑电路的方法。

2.了解计数器的Verilog描述方法,以及偶数分频的思路与原理。

●预习要求:1.回顾数字电路中加法计数器的相关知识。

●实验说明:1.用MAX+plus II软件开发PLD器件有两种设计输入方式:原理图输入和HDL语言输入方式,或者将两者结合起来,一部分电路采用原理图,另一部分采用HDL语言。

2.加法计数器表示随着时钟脉冲的输入,计数器从0开始正向计数,直到计满规定的模值后归零,然后依次循环计数。

模10计数器表示,计数器从0000~1001循环计数。

3.时钟分频电路的功能是,对输入的时钟频率进行偶数倍的降频(倍增其周期),10分频意味着分频后产生的新时钟周期是输入时钟的20倍。

●实验内容与步骤:1.新建一个属于自己的工程目录。

2.用VerilogHDL语言方式编写一个模10加法计数器cnt_10。

3.对此计数器模块进行编译和仿真。

4.用VerilogHDL语言方式编写一个20分频模块fenpin_20,对输入时钟进行20分频处理。

5.对此分频电路进行仿真。

●实验报告要求:1.将自己绘制的电路图或者编写的VerilogHDL代码,截图或者复制到实验报告中。

2.将代码关键位置写上相应注释(可用中文)。

3.对仿真波形截图,贴到实验报告中。

●实验图表与数据:1. 模10加法计数器cnt_10的V erilog代码2. 模10加法计数器cnt_10的仿真波形:3. 20分频模块fenpin_10的Verilog代码:4. 20分频模块fenpin_10的仿真波形:。

同步可逆十进制计数器verilog代码

同步可逆十进制计数器verilog代码以下是一个同步可逆十进制计数器的Verilog代码:```module sync_reversible_counter(input clk, // 输入时钟信号input reset, // 输入复位信号output reg [3:0] count // 输出计数器值);// 定义状态变量reg [2:0] state;// 初始化状态变量和计数器值initial beginstate = 3'b000;count = 4'b0000;end// 状态转移逻辑always @(posedge clk) beginif (reset) begin // 复位信号为高电平时,将状态变量和计数器值重置为初始值state <= 3'b000;count <= 4'b0000;end else begin // 否则进行状态转移操作case (state)3'b000: begin // 当前状态为000时,下一状态为001,计数器加1state <= 3'b001;count <= count + 1;end3'b001: begin // 当前状态为001时,下一状态为010,计数器加1state <= 3'b010;count <= count + 1;end3'b010: begin // 当前状态为010时,下一状态为011,计数器加1state <= 3'b011;count <= count + 1;end3'b011: begin // 当前状态为011时,下一状态为100,计数器加1state <= 3'b100;count <= count + 1;end3'b100: begin // 当前状态为100时,下一状态为101,计数器加1state <= 3'b101;count <= count + 1;end3'b101: begin // 当前状态为101时,下一状态为110,计数器加1state <= 3'b110;count <= count + 1;end3'b110: begin // 当前状态为110时,下一状态为111,计数器加1state <= 3'b111;count <= count + 1;end3'b111: begin // 当前状态为111时,下一状态为000,计数器加1state <= 3'b000;count <= count + 1;endendcaseendendendmodule```这个Verilog代码实现了一个同步可逆十进制计数器。

10进制计数器的verilog设计

Lab6 10进制计数器吴晓鸣五班U2011138401.实验目的a. 使用Verilog语言实现10进制计数器设计。

b. 做出仿真波形。

c. 使用DE0开发板下载、验证。

2.实验内容●编写十进制计数器的代码,烧录到DE0中●用LED灯显示计数3.代码分析module abc(EN,CP,CR,Q);input EN,CP,CR;//三个输入端口output [3:0]Q;//四个输出端口reg[3:0]Q;always @(posedge CP or negedge CR)//当CP为上升沿或CR为下降沿if(~CR)Q=4'b0000;//清零开关else if(EN)//使能开关beginif(Q>=4'b1001) Q<=4'b0000;//当Q的值大于等于9,跳到0else Q<=Q+1'b1;endelse Q<=Q;endmodule4.实验步骤●新建一个工程,选择相应的实验板型号,创建一个Verilog HDL文件,输入程序。

●分析并编译程序,设置开发板引脚。

●连接实验板,烧入程序。

5. 实验结果的测试和分析a.编译代码:b.仿真波形c. 下载到DE0实验板上:设置引脚后,LED灯有规律的闪动,到9后,跳回0.6.实验总结通过这个实验,我了解了计数器与分频器的基本原理,熟悉了怎样用LED和verilog 来实现10进制的计数器,并用DE0显示实验结果。

7. 参考文献[1]康华光.电子技术基础(数字部分)北京:高等教育出版社,2006.[2]罗杰.Verilog HDL与数字ACIC设计基础武汉:华中科技大学出版社,2008.。

Verilog_HDL十进制计数器实验Quartus90非常详细的步骤

页 802 共 页 73 第 图击点、noitalipmoc trats>-gnissecorP 项单菜击点。件文译编全�后配分脚引成完 .22 。制控动手关开用使�波方频低出输接直法办有没板发开 07_2ED�关相 kcolc�意注 图脚引配分 63-3 图

绿个

。42V 是不 42Y 意注�63-3 图考参�一验实考 参�。]0[WS 关开接 klc�]0[YEK 接 n_tsr�]4[GDEL 接 wolfrevo �上�]0[GDEL-]3[GDEL� DEL 4 的板发开 07-2ED 到置配出输 q 的器数计将�册手导指户用 07-2ED 的供 提所据根。作操的脚引配分行进以可�后确正能功认确�后成完真仿。脚引置配 .12 果结真仿 53-3 图

为设制强 标图侧左击单�号信 n_tsr 中选。平电高续持后 sn02 低成改 n_tsr 将 .61

置设期周的钟时 72-3 图

。率比间时的占所内之期周个一在平电高指是即�比 空占是思意的 elcyc ytuD。72-3 图如�sn02 为整调期周把中框话对定设 kcolc 的出弹在 波方为改 klci 将 62-3 图

。件文计设辑编且并加添后之 txeN 击点�件文计设的成完有没果如�件文应相加添次再么那 验实器数计制进十 二验实

页 802 共 页 62 第 正户用现出会中栏签标 yhcrareiH 的 rotagivaN tcejorP 中面界 II sutrauQ�后建新成完在 结总程工建新 8-3 图

。建新成完 hsiniF 击点后认确�示所 8-3 图如�计设的前之对 核户用让结总个一成生动自会 II sutrauQ�后成完计设本基在。结总程工建新看查 .7 具工 ADE 置设 7-3 图

验实器数计制进十 二验实

verilog HDL十进制加减法计数器报告

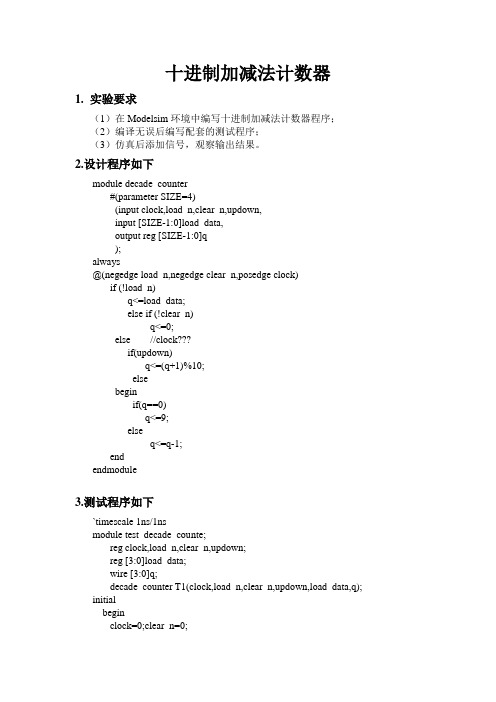

十进制加减法计数器1.实验要求(1)在Modelsim环境中编写十进制加减法计数器程序;(2)编译无误后编写配套的测试程序;(3)仿真后添加信号,观察输出结果。

2.设计程序如下module decade_counter#(parameter SIZE=4)(input clock,load_n,clear_n,updown,input [SIZE-1:0]load_data,output reg [SIZE-1:0]q);always@(negedge load_n,negedge clear_n,posedge clock)if (!load_n)q<=load_data;else if (!clear_n)q<=0;else //clockif(updown)q<=(q+1)%10;elsebeginif(q==0)q<=9;elseq<=q-1;endendmodule3.测试程序如下`timescale 1ns/1nsmodule test_decade_counte;reg clock,load_n,clear_n,updown;reg [3:0]load_data;wire [3:0]q;decade_counter T1(clock,load_n,clear_n,updown,load_data,q);initialbeginclock=0;clear_n=0;#30 clear_n=1;load_n=0;load_data=7;#30 load_n=1;updown=0;#300 updown=1;#300 updown=0;#300 updown=1;#300 $stop;endalways#10 clock=~clock;always@(q)$display("At time%t,q=%d",$time,q);endmodule4.波形如下5.测试结果如下# At time 0,q= 0# At time 30,q= 7# At time 70,q= 6# At time 90,q= 5# At time 110,q= 4# At time 130,q= 3# At time 150,q= 2# At time 170,q= 1# At time 190,q= 0# At time 210,q= 9# At time 230,q= 8# At time 250,q= 7# At time 270,q= 6# At time 290,q= 5# At time 310,q= 4# At time 330,q= 3# At time 370,q= 3 # At time 390,q= 4 # At time 410,q= 5 # At time 430,q= 6 # At time 450,q= 7 # At time 470,q= 8 # At time 490,q= 9 # At time 510,q= 0 # At time 530,q= 1 # At time 550,q= 2 # At time 570,q= 3 # At time 590,q= 4 # At time 610,q= 5 # At time 630,q= 6 # At time 650,q= 7 # At time 670,q= 6 # At time 690,q= 5 # At time 710,q= 4 # At time 730,q= 3 # At time 750,q= 2 # At time 770,q= 1 # At time 790,q= 0 # At time 810,q= 9 # At time 830,q= 8 # At time 850,q= 7 # At time 870,q= 6 # At time 890,q= 5 # At time 910,q= 4 # At time 930,q= 3 # At time 950,q= 2 # At time 970,q= 3 # At time 990,q= 4 # At time 1010,q= 5 # At time 1030,q= 6 # At time 1050,q= 7 # At time 1070,q= 8 # At time 1090,q= 9 # At time 1110,q= 0 # At time 1130,q= 1 # At time 1150,q= 2 # At time 1170,q= 3 # At time 1190,q= 4 # At time 1210,q= 5# At time 1250,q= 7。