verilog程序-60进制计数器

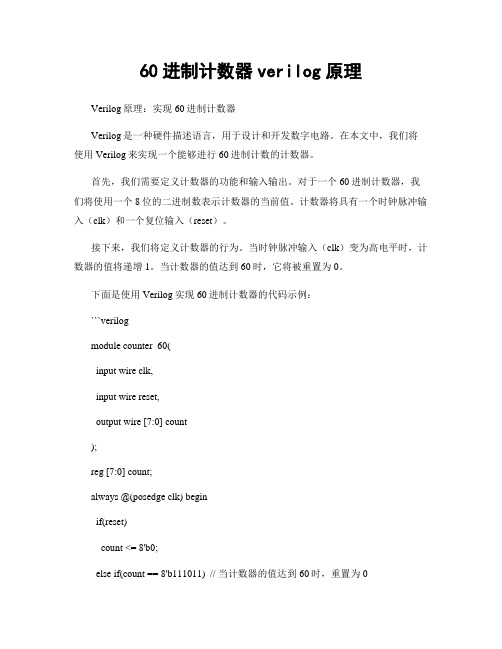

60进制计数器verilog原理

60进制计数器verilog原理Verilog原理:实现60进制计数器Verilog是一种硬件描述语言,用于设计和开发数字电路。

在本文中,我们将使用Verilog来实现一个能够进行60进制计数的计数器。

首先,我们需要定义计数器的功能和输入输出。

对于一个60进制计数器,我们将使用一个8位的二进制数表示计数器的当前值。

计数器将具有一个时钟脉冲输入(clk)和一个复位输入(reset)。

接下来,我们将定义计数器的行为。

当时钟脉冲输入(clk)变为高电平时,计数器的值将递增1。

当计数器的值达到60时,它将被重置为0。

下面是使用Verilog实现60进制计数器的代码示例:```verilogmodule counter_60(input wire clk,input wire reset,output wire [7:0] count);reg [7:0] count;always @(posedge clk) beginif(reset)count <= 8'b0;else if(count == 8'b111011) // 当计数器的值达到60时,重置为0count <= 8'b0;elsecount <= count + 1;endendmodule```以上代码中,我们使用`reg`关键字声明了一个8位的寄存器`count`,用于存储计数器的当前值。

`always @(posedge clk)`表示在时钟上升沿触发时执行以下代码块。

在代码块中,我们首先检查复位信号(reset)是否为高电平。

如果是,计数器的值将被重置为0。

接下来,我们使用一个条件语句判断计数器的值是否为59(8'b111011)。

如果是,计数器的值将重置为0。

否则,计数器的值递增1。

最后,我们将计数器的值作为输出wire `count`进行输出。

通过将以上代码编译为Verilog硬件描述语言的通用代码格式,我们可以在FPGA或ASIC芯片上实现一个用于60进制计数的计数器。

60进制计数器的设计

本科学生设计性实验报告项目组长_学号_成员专业_通信工程__班级_实验项目名称_ 60进制计数器的设计指导教师及职称_________开课学期 2011 至_2012 学年_第二_学期上课时间 2012 年 4 月 16 日一、实验设计方案实验名称:60进制计数器的设计实验时间:2012-4-16小组合作:是○否●小组成员:1、实验目的:熟悉QuartusⅡ的Verilog文本设计流程全过程,学习计数器的设计、仿真和硬件测试。

掌握原理图与文本混合设计方法。

实验要求:1.使用三种以上方法进行设计和仿真2.每种方法要有详细的设计程序和仿真结果3.对比每种方法的实现的RTL图4.选择一种在硬件上实现,并绘出详细实验步骤和实验步骤截图,最后描述实验结果2、实验场地及仪器、设备和材料:实验场地:电脑,quartus II软件,GW48EDA/SPOC主系统实验箱3、实验思路(实验内容、数据处理方法及实验步骤等):实验内容:用Verilog设计一个60进制计数器,要求用三种方式。

1. 打开QuartusII软件,建立一个新的工程:1) 单击菜单File\New Project Wizard…2) 输入工程的路径、工程名以及顶层实体名。

3) 单击Next>按钮,由于我们建立的是一个空的项目,所以没有包含已有文件,单击Next>继续。

4) 设置我们的器件信息:2.建立Verilog文件:1) 单击File\New菜单项,选择弹出窗口中的Verilog File项,单击OK按钮以建立打开空的Verilog文件。

2) 在编辑窗口中输入Verilog源文件并保存,注意实体名、文件名必须和建立工程时所设定的顶层实体名相同。

3) 编译工程单击Processing\Start Compilation开始编译,编译过程中可能会显示若干出错消息,参考提示原因对程序进行修改直到编译完全成功为止。

根据书上的例子做出了如下的三种方法:(1)方式一:(2)方式二:(3)方式三指导老师对实验设计方案的意见:指导老师签名:年月日二、实验结果与分析1、实验目的、场地及仪器、设备和材料、实验思路等见实验设计方案2、实验现象、数据及结果实验现象:(1)方式一:生成如下图电路模型:得到下图为波形图:(2)方式二:生成电路模型如图所示:得到的波形图如图所示:(3)方式三:得到电路模型如图所示:得到波形图如图所示:3、对实验现象、数据及观察结果的分析与讨论:通过实验过程,可以得到实验的相关图像,可能由于实验过程差不多所以得到的结果是差不多的。

六十进制计数器

单击Next单击Next单击Next单击Next单击Next单击Finish建好工程后,新建“Verilog HDL Files”,步骤如下图:单击此按钮选中Verilog HDL Files,单击OK 再出现的text编辑窗口中输入六进制的代码如下:注意所保存的文件名要和模块的名字一致然后就是编译:1.首先将文件置为顶层文件,两种方式:①快捷键“ctrl+shift+J”②菜单栏选中project——>Set as Top_level entity2.进行仿真:①快捷键“ctrl+L”②单击按钮③Processing——>Start Compilation编译成功后就是进行仿真了:新建仿真文件:选择Vector Waveform File,单击OK在左边空白处,右击后选择Insert,再选择Insert Node and Bus单击Node Finder…Filter:选择Pin:all,单击list,左边框中出现顶层文件中的端口,选中需要的端口,单击中间’>’按钮,即可导入,单击按快捷键“ctrl+S”,保存仿真文件,命名为“cnt6”,之后,菜单栏——>Processing——>simulator Tool: 先进行时序仿真,选中mode为Timing,选则input文件为cnt6.vwf,点击start:单击“Generate Functional Simulation Netlist”,单击start,进行功能仿真:2.VerilogHDL编写十进制计数器:具体步骤同上1,只把代码截图和仿真波形截图附上:时序仿真波形图如下:功能仿真波形如下图:3.VerilogHDL编写译码器:具体步骤同上1,只把代码截图和仿真波形截图附上:时序仿真波形图如下:功能仿真波形如下图:4.将以上三个模块级联获得60进制计数器,显示在数码管上:(1)先将三个模块生成符号文件,将模块文件置为顶层文件后,File——>Creat/update ——>Creat Symbol Files for Current file(2)新建Block diagram/Schematic Files.保存后,将此文件置为顶层文件,进行编译。

60进制计数器实验报告

60进制计数器实验报告60进制计数器实验报告引言:计数器是一种常见的电子设备,用于记录和显示数字。

在日常生活中,我们常见的计数器是十进制计数器,即由0到9的数字循环计数。

然而,在某些特殊的应用场景中,十进制计数器可能不够灵活。

本实验旨在设计和实现一种60进制计数器,以满足特定需求。

实验目的:1. 设计并实现60进制计数器电路;2. 验证60进制计数器的功能和准确性;3. 探讨60进制计数器的应用价值。

实验原理:十进制计数器是通过使用4位二进制计数器和逻辑门电路来实现的。

同样地,60进制计数器可以通过使用更多位的二进制计数器和逻辑门电路来实现。

在本实验中,我们使用6位二进制计数器和逻辑门电路来构建60进制计数器。

实验材料:1. 74LS74型D触发器芯片 x 62. 74LS00型与非门芯片 x 23. 74LS08型与门芯片 x 14. 连线材料5. 示波器6. 电源实验步骤:1. 根据电路原理图,连接各个芯片和逻辑门,确保连接正确无误。

2. 将电源接入电路,注意电压和接线的正确性。

3. 使用示波器观察计数器输出的波形,并检查是否按照预期进行计数。

实验结果:经过实验,我们成功地设计并实现了60进制计数器。

计数器在每个时钟脉冲的作用下,能够准确地按照60进制进行计数,并输出相应的波形。

通过示波器观察,我们可以清晰地看到计数器的计数过程,以及在达到最大计数值后的溢出现象。

实验讨论:60进制计数器的设计和实现为特定领域的计数需求提供了解决方案。

例如,在时间测量中,60进制更符合人们对时间的感知和使用习惯。

此外,60进制计数器还可以应用于音乐节拍器、航天导航等领域,提供更灵活和精确的计数方式。

然而,60进制计数器也存在一些限制和挑战。

首先,由于60不是2的幂次,所以构建60进制计数器的硬件复杂度较高。

其次,60进制计数器在数字显示和数据传输方面需要进行转换,增加了额外的工作量和成本。

结论:通过本实验,我们成功地设计并实现了60进制计数器。

60进制计数器进位信号和归零逻辑

60进制计数器进位信号和归零逻辑

在传统的计数系统中,我们经常使用十进制计数器,即使用0-9的数字进行计数。

然而,在某些特定的应用场景中,十进制计数器可能不够灵活。

这时,我们可以考虑使用其他进制计数器,如60进制计数器。

在60进制计数器中,我们使用的数字从0到59,而不再是0到9。

这意味着我们可以更精确地计数,并且可以在更长的时间段内进行计数,而不需要进行进位。

那么,进位信号和归零逻辑在60进制计数器中是如何工作的呢?

首先,我们需要确定计数器的位数。

在十进制计数器中,我们通常使用10位二进制数字进行计数,而在60进制计数器中,我们需要使用更多的位数,以便能够表示60个不同的数字。

当一个位达到60时,它就需要进位了。

进位信号会被发送给下一位,使其加1。

这个过程类似于十进制计数器中的进位操作,只不过进位的基数变成了60。

当最高位达到60时,我们可以选择两种方式来处理。

一种方式是忽略进位,继续递增最高位。

这意味着我们可以计数到最高位达到59,

然后归零重新计数。

另一种方式是将最高位的进位信号发送给其他系统,以触发一些特定的操作。

归零逻辑也是十分重要的。

当我们需要将计数器归零时,我们需要将所有位的值都设置为0。

这可以通过将每一位的进位信号发送给下一位来实现,直到最低位。

总之,60进制计数器的进位信号和归零逻辑与十进制计数器类似,只不过进位的基数变成了60。

这使得60进制计数器可以更灵活地进行计数,并且适用于一些特定的应用场景。

60计数器工作原理

60计数器工作原理

60计数器是一种数字电路元件,用于实现60进制的计数功能。

其工作原理如下:

1. 输入信号:60计数器通常有一个时钟输入信号。

当时钟信

号的一个脉冲到达时,计数器会按照特定的规则进行计数。

2. 初始化:计数器在初始状态下一般为0,即所有计数位上都

为0。

3. 计数规则:60计数器通常由多个计数位组成,每个计数位

都有两种状态:0和1。

当计数器接收到一个时钟脉冲时,它

会根据特定的规则将计数位递增,并将进位(carry out)信号

传递到高位。

4. 进位规则:在60计数器中,当最低位计数位达到其最大值(59时),它会产生一个进位信号。

这个进位信号会传递给

高位计数位,引起它们进行递增。

5. 循环:当最高位计数位达到其最大值时(59时),它也会

产生一个进位信号。

这个进位信号又会传递到最低位计数位,从而形成一个循环。

整个计数器会在0到59之间循环计数。

6. 外部控制:60计数器通常还有一些控制信号,如使能信号

和复位信号。

使能信号可以控制计数器的启用与禁用,而复位信号可以将计数器的状态重置为初始状态。

通过上述工作原理,60计数器可以实现60进制的计数功能,用于计时、频率分频、时钟同步等应用。

60进制计数器原理

60进制计数器原理60进制计数器是一种特殊的计数器,它可以用于表示60进制的数字。

在日常生活中,我们常常使用60进制计数器来表示时间,比如小时、分钟和秒。

在这篇文档中,我们将介绍60进制计数器的原理及其应用。

首先,让我们来了解一下60进制计数器的基本原理。

60进制计数器是一种基于60进制的数字系统,它由60个不同的数字组成,分别是0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F、G、H、I、J、K、L、M、N、O、P、Q、R、S、T、U、V、W、X、Y、Z、a、b、c、d、e、f、g、h、i、j、k、l、m、n、o、p、q、r、s、t、u、v、w、x、y、z、!、?、@、#、$、%。

这些数字可以组合成任意大小的数字,用来表示时间、角度、经纬度等。

接下来,让我们来看一下60进制计数器的应用。

在日常生活中,我们经常使用60进制计数器来表示时间。

例如,一天有24小时,每小时有60分钟,每分钟有60秒。

这种时间表示方法就是基于60进制计数器的原理。

另外,60进制计数器还可以用于表示角度。

在几何学和航海领域,我们经常使用60进制计数器来表示角度。

例如,一圈360度可以被表示为60进制的数值,这样可以更加方便地进行计算和测量。

除了时间和角度之外,60进制计数器还可以应用于其他领域。

在计算机科学中,我们经常使用60进制计数器来表示数据存储地址。

在地理信息系统中,我们也可以使用60进制计数器来表示经纬度。

总的来说,60进制计数器在各个领域都有着广泛的应用。

综上所述,60进制计数器是一种基于60进制数字系统的计数器,它可以用于表示时间、角度、数据存储地址等。

通过了解60进制计数器的原理及其应用,我们可以更好地理解其在日常生活和各个领域中的重要性和作用。

希望本文可以帮助您更好地理解60进制计数器,并在实际应用中发挥其作用。

Verilog机组实验计数器

计数器+ALU实验

实验内容

1、ALU实现及仿真

2、计数器实现及仿真

3、ALU+计数器综合实现及仿真

实验原理

1、A LU实现及仿真

使用Verilog HDL代码编程方式构建ALU181元件符号,生成ALU模块。

主要步骤:

(1)建立工程(注意工程名字和文件夹名字一致)

(2)编辑ALU181.v文件,并生成元件符号

(3)建立原理图文件,调用该元件符号

(4)编译

(5)波形仿真(不需引脚绑定)

2、计数器实现及仿真

(1)设计计数器Counter元件。

通过.v文件构建元件符号Counter,生成计数器。

(2)进行波形仿真

(3)进行引脚绑定,下载到实验箱进行验证。

3、ALU+计数器综合实现及仿真

(1)设计计数器Counter元件。

通过.v文件构建元件符号Counter,生成计数器(2)设计ALU元件。

通过.v文件构建元件符号ALU181

(3)计数器产生的信号S[3..0]作为ALU中S[3..0]的输入信号。

实验中程序运行结果及截图

实验心得

通过这次实验的学习。

我们了解到了ALU和计数器的基本原理,通过自己动手实验,进一步了解了其基本结构在实际实验中是怎样发挥作用的。

在实验的过程中,我和小组成员互相配合,共同摸索,虽然几经失败,但是最后在老师的帮助下发现了错误,并且加以改正,最后成功做出了实验,完成了一个简单的ALU+计数器。

在此过程中,增强了动手能力,加深了理解,增进了友谊,是一次不可多得的宝贵的实验经历。