基于FPGA与DDS的磁共振成像射频脉冲发生器

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

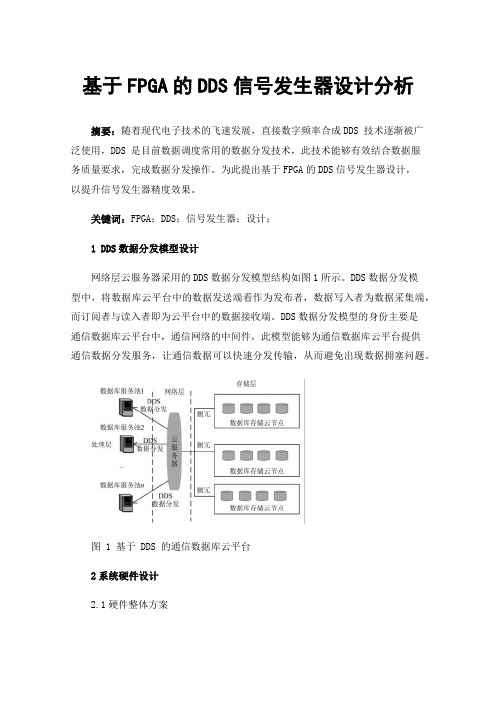

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

基于FPGA的DDS信号发生器的设计

基于 FPGA 的 DDS 信号发生器的设计发布时间:2022-11-15T12:38:52.851Z 来源:《中国科技信息》2022年第7月14期作者:陈慰安[导读] DDS是一种新的频率合成技术,陈慰安广东省博罗县质量技术监督检测所广东省惠州市 516100摘要:DDS是一种新的频率合成技术,也是一种新的信号生成技术。

该方法具有频率分辨率高、频率转换快、相位变化时能保持相位连续,易于实现频率、相位、振幅等数字调制。

因此,DDS在现代电子设备尤其是通信领域中得到了广泛的应用。

关键词:FPGA;DDS信号发生器;设计1FPGA和DDS相关概述FPGA(FieldProgrammableGateArray)是一种高集成度、高速度、高存储能力的器件。

该方法能够有效地实现DDS技术,极大地改善了功能信号发生器的工作效率,并大幅度降低了电子设备的制造成本。

传统的信号源电路采用模拟电路、单片机或DDS专用的芯片。

尽管其应用领域广泛,但是仍然有很多缺点,例如:设计方案成本高,输出波形类型少,输出信号频率控制不灵活,系统升级困难等。

传统的信号源存在两大问题。

一种是调节电压调节器来调节输出的频率,使其难以调节到一个固定的数值;另外,脉冲的工作周期是不能调节的。

DDS技术是目前世界上最主要的一种数字技术,它有很多优势。

DDS技术是一种低功耗、低成本、高转换频率和高分辨率的频率合成技术。

通常,DDS技术有如下几种产生信号的方法:①集成电路功能信号发生器通常能用于产生信号,但是它的功能不全、可用性低、精度低、不能满足高频信号的需要。

②利用MCU的功能产生器来完成:MAX038的优势在于生成高频信号并生成不同的波形,但是MAX038的输出频率是由模拟信号控制的。

该方法既要实现对信号的变换,又要对其进行控制。

由于步长的增大,导致了频率的精确度下降,使得电路变得更为复杂。

DDS技术是一种新的频率合成技术,它与前面所说的信号产生方式相比,可以直接进行DDS芯片的合成,具有操作简单、节约资源等优点。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着数字信号处理(DSP)技术的发展,直接数字频率合成器(DDS)逐渐取代了传统的频率合成器,成为一种高性能的信号发生器。

DDS信号发生器通过数字信号直接产生模拟信号,具有频率精度高、可编程性强和快速调频等优点。

本文将通过FPGA实现DDS信号发生器的设计。

首先,我们需要了解DDS信号发生器的基本原理。

DDS信号发生器的核心是相位累加器、查找表和数模转换器(DAC)。

通过累加器产生相位累积,将相位累积的结果通过查找表得到对应的振幅值,并经过数模转换器输出模拟信号。

1.确定需要生成的信号的参数,包括输出频率、相位步进精度、振幅等。

根据这些参数,计算累加器的增量值,即每个时钟周期累加器需要累加的值。

2.在FPGA中设计相位累加器。

相位累加器的宽度取决于相位步进精度,一般为32位或64位。

通过在每个时钟周期加上增量值,实现相位的累加。

3.设计查找表。

查找表的大小取决于数字信号的分辨率,一般为2^N 位。

通过输入相位值查找对应的振幅值。

4.设计数模转换器(DAC)。

通过DAC将数字信号转换为模拟信号输出。

5.在FPGA中实现控制逻辑,包括控制相位累加器和查找表的读写操作,使其按照设定的参数进行相位累加和振幅输出。

6.将设计好的FPGA模块进行综合、布局和时序约束,生成比特流文件。

通过以上步骤,基于FPGA的DDS信号发生器的设计就完成了。

设计好的FPGA模块可以实现高精度、高稳定性的信号发生器,广泛应用于通信、雷达、医疗设备等领域。

需要注意的是,在设计过程中需要考虑到FPGA的资源限制,包括LUT资源的利用、频率分辨率和输出频率的限制等。

此外,还可以通过增加相位累积周期、使用多路查找表和多路DAC等方法进一步优化设计。

综上所述,基于FPGA的DDS信号发生器设计是一个较为复杂的过程,需要对DDS原理有深入的理解,并结合FPGA的特点进行设计。

通过合理的设计和优化,可以实现高性能的DDS信号发生器。

(完整word版)基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计摘要:利用FPGA芯片及D/A转换器,采用直接数字频率合成技术,设计并实现了一个频率、幅值可调的信号发生器,同时阐述了该信号发生器的工作原理、电路结构及设计思路。

经过电路调试,输出波形达到技术要求,证明了该信号发生器的有效性和可靠性。

0 引言信号发生器作为一种基本电子设备广泛的应用于教学、科研中,因此从理论到工程对信号的发生进行深入研究,有着积极的意义.随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。

本文研究了基于FPGA 的DDS信号发生器设计,实现了满足预定指标的多波形输出。

可产生不同频率、幅度的正弦波、三角波、矩形波信号,仿真和实测结果均证实了其灵活性和可靠性。

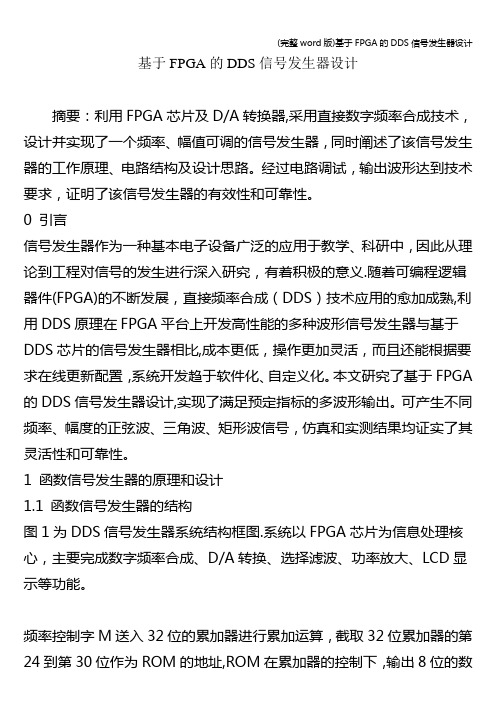

1 函数信号发生器的原理和设计1.1 函数信号发生器的结构图1为DDS信号发生器系统结构框图.系统以FPGA芯片为信息处理核心,主要完成数字频率合成、D/A转换、选择滤波、功率放大、LCD显示等功能。

频率控制字M送入32位的累加器进行累加运算,截取32位累加器的第24到第30位作为ROM的地址,ROM在累加器的控制下,输出8位的数字波形数据,经过DAC0832转换为模拟量,因为DAC0832输出的是电流的形式,所以通过电压转电流电路转换为电压形式的模拟波形,但其中还含有大量的高频成分,为了输出频率纯净的信号波形,再通过一个二阶的有源低通滤波器。

最后为了调节输出信号的峰峰值,再引入一个幅度调节电路。

根据直接数字频率合成理论将系统的频率分辨率及输出频率写为:其中fclk和N为系统时钟和位宽,M为频率控制字,利用信号相位与时间成线性关系的特性,直接对所需信号进行抽样、量化和映射,输出频率可调的信号波形。

基于FPGA的DDS信号发生器设计【开题报告】

毕业设计开题报告电子信息科学与技术基于FPGA的DDS信号发生器设计一、选题的背景与意义1971年,美国学者J.Tierney等人撰写的"A Digital Frequency Synthesizer"一文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新合成原理。

限于当时的技术和器件生产,它的性能指标无法与已有的技术相比,故未受到重视。

之后的一年间,微电子技术有了飞速的发展,直接数字频率合成器(即DDS)也得到了迅速的发展。

一些传统的信号波形产生方法,如RC和LC振荡器或单片模拟集成函数发生器,尽管它们的电路实现比较简单,但产生的信号波形频率精度和稳定度并不是很理想,而使用锁相环技术,频率精度有了很大的提高,但工艺相对比较复杂,分辨率也不高,频率变换和实现计算机程序控制也不方便。

而这种DDS技术将先进的数字信号处理理论与方法引入信号合成领域,实现了合成信号的频率转换和频率准确度之间的统一。

它具有相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、输出波形灵活、可编程、全数字化、控制灵活、体积小、易于集成、功耗低等优越的性能特点,击败其他频率合成技术脱颖而出,成为了现代频率合成技术的佼佼者。

现如今性能优良的DDS产品不断推出,它们集可编程DDS系统、高性能DAC及高速比较器等于一身,能实现多种功能,被广泛应用于跳频通信、雷达、导航、电子侦察、干扰和反干扰等电子技术领域,具有极高的研究价值。

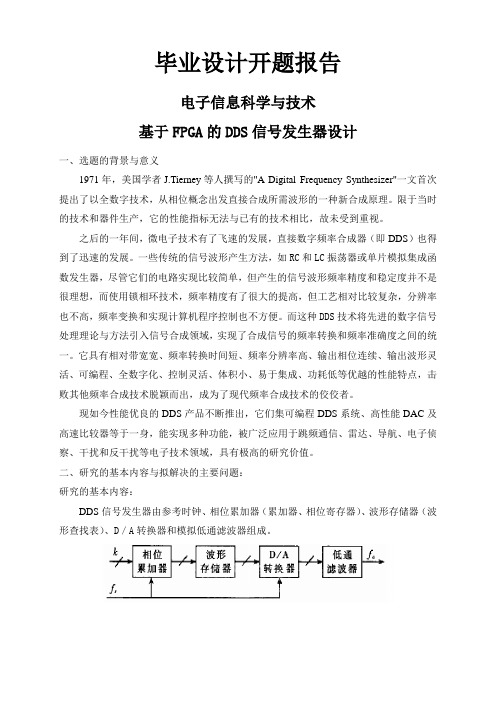

二、研究的基本内容与拟解决的主要问题:研究的基本内容:DDS信号发生器由参考时钟、相位累加器(累加器、相位寄存器)、波形存储器(波形查找表)、D/A转换器和模拟低通滤波器组成。

(1)参考时钟参考时钟是电路的工作时钟由开发板上的晶振(约50MHz)提供。

(2)相位累加器DDS系统的核心部分为相位累加器,其主要负责DDS实现原理中的相位累加功能的完成。

如果累加器的位数大,这样才能使DDS的优越性充分发挥出来,通常DDS的输出频率可由频率控制字K控制,其设定可根据需要进行。

基于FPGA的DDS信号发生器的研究--毕业论文

第1章绪论1.1 课题背景频率检测是电子测量领域的最基本也是最重要的测量之一,频率信号抗干扰强,易于传输,可以获得较高的测量精度,所以频率方法的研究越来越受到重视[1]。

在频率合成领域中,直接数字合成(Direct Digital Synthesizer,简称:DDS)是近年来新的技术, 它从相位的角度出发直接合成所需波形。

它是由美国人J.Tierncy首先提出来的,是一种以数字信号处理理论为基础,从相位概念出发直接合成所需波形的一种新的全数字技术的频率合成方法[2]。

其主要优点有:频率改变速度快、频率分辨率高、输出相位连续、可编程、全数字化便于集成等,目前使用最广泛的一种DDS频率合成方式是利用高速存储器将正弦波的M个样品存在其中,然后以查找的方式按均匀的速率把这些样品输入到高速数模转换器,变成所设定频率的正弦波信号[3]。

近30年来,随着超大规模集成、现场可编程门阵列(Field Programmable Gate Array,简称:FPGA)、复杂可编程器件(Complex programmable Logic Device,简称:CPLD)等技术的出现以及对DDS理论上的进一步探讨,使得DDS技术得到了飞速的发展。

它已广泛应用于通讯、雷达、遥控测试、电子对抗、以及现代化的仪器仪表工业等许多领域。

DDS的数字部分,即相位累加器和查表,被称为数控振荡器(NCO)[4]。

波形发生器即通常所说的信号发生器是一种常用的信号源,和示波器、电压表、频率计等仪器一样是最普遍、最基本也是应用最广泛的的电子仪器之一,几乎所有电参量的测量都要用到波形发生器。

不论是在生产还是在科研与教学上,波形发生器都是电子工程师信号仿真试验的最佳工具。

随着现代电子技术的飞速发展,现代电子测量工作对波形发生器的性能提出了更高的要求,不仅要求能产生正弦波、方波等标准波形,还能根据需要产生任意波形,且操作方便,输出波形质量好,输出频率范围宽,输出频率稳定度、准确度及分辨率高,频率转换速度快且频率转换时输出波形相位连续等。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着现代科技的不断发展,数字信号发生器(DDS)已成为各种电子设备中常用的一种功能模块。

使用DDS技术可以生成高质量、高稳定性的各种频率和波形的信号。

而FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,具有高集成度、高速度和灵活性等优势,逐渐成为了实现DDS信号发生器的主要选择之一一、DDS技术概述DDS(Direct Digital Synthesis)技术是一种基于数字直接合成的方法,通过计算机算法精确地合成期望的波形。

它的工作原理是将时钟信号分频得到一系列的离散相位值,再通过查表和插值的方法得到对应的幅值,最后通过一个DAC(Digital to Analog Converter)将数字信号转换为模拟信号输出。

二、基于FPGA的DDS信号发生器设计步骤1.系统架构设计根据DDS信号发生器的要求,确定所需的系统架构。

一般包括时钟模块、相位累加器、查找表、插值器、DAC和控制逻辑等模块。

2.时钟模块使用FPGA内部的资源或外部时钟源生成所需的系统时钟信号。

可以通过时钟分频和PLL(Phase-Locked Loop)锁相环技术来实现对系统时钟的精确控制。

3.相位累加器利用FPGA的寄存器或分频模块实现相位累加功能。

通过周期性地累加相位增量,可以得到DDS信号的相位。

4.查找表利用FPGA内部的RAM(Random Access Memory)存储相位对应的幅值。

根据相位的大小来查找对应的幅值,存储在RAM中。

5.插值器可以通过线性插值或差值的方法对相位查找表的输出进行插值,以提高输出信号的精度和稳定性。

6.DAC将插值器输出的数字信号转换为模拟信号,通过FPGA的IO端口或专用的DAC芯片输出到外部电路。

7.控制逻辑设计合适的控制逻辑,可以通过外部接口或FPGA内部的控制模块来控制DDS信号发生器的频率、幅值、相位偏移等参数。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计一、引言随着科技的不断发展,数字信号处理(Digital Signal Processing,简称DSP)在各个领域得到广泛应用。

其中,一种常见的应用是通过数字直接合成(Digital Direct Synthesis,简称DDS)来生成各种信号。

DDS信号发生器能够快速准确地产生高质量的信号,被广泛应用于通信、电子测量、医疗器械等领域。

本文将阐述基于现场可编程门阵列(Field-Programmable Gate Array,简称FPGA)的DDS信号发生器设计。

二、FPGA的简介FPGA是一种可编程的逻辑器件,其内部包含了大量可编程的逻辑单元和存储单元。

FPGA具有灵活性高、可重构性强等特点,可以根据设计者的需求,灵活地实现各种数字电路。

因此,FPGA成为DDS信号发生器设计的理想平台。

三、DDS技术原理DDS技术通过数字控制相位累加器和振荡器来实现信号的直接合成。

其中,相位累加器用于控制振荡器输出频率的连续调节,振荡器则根据相位累加器的输出产生正弦波。

DDS信号发生器的主要步骤如下:1. 初始化相位累加器:将初始相位值存入相位累加器。

2. 累加相位值:相位累加器根据设定的增量值不断累加,得到一个新的相位值。

3. 查表获得振荡器的输出值:通过查表法,根据相位值获得振荡器的输出幅度。

4. 输出信号:根据振荡器的输出幅度,形成DDS信号。

四、1. 系统架构设计:本设计采用基于FPGA的硬件逻辑实现DDS信号发生器。

系统由相位累加器、振荡器、幅度调节模块和输出模块组成。

其中,相位累加器使用FPGA中的计数器实现,振荡器采用三角函数计算逼近的方式实现,幅度调节模块用于调节振荡器的输出幅度,输出模块将DDS信号输出到外部。

2. 相位累加器设计:相位累加器是DDS信号发生器的核心模块。

本设计采用基于FPGA的计数器实现相位累加器,通过控制计数器的计数速度来调节信号的频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA与DDS的磁共振成像射频脉冲发生器李聿为;肖亮【摘要】设计了一种基于现场可编程门阵列(FPGA)与直接数字频率合成(DDS)的磁共振成像(MRI)射频脉冲发生器,采用FPGA实现DDS,并内置软脉冲波形双端口随机存取存储器(RAM)、乘法器以及相关的控制逻辑.实现了较高的技术指标,其中频率、相位与幅度分辨率分别为32 bits、16 bits与16 bits,软脉冲波形的时间精度可达0.1ms. FPGA提供了一个可编程的接口,便于序列控制器对其进行控制,以输出射频脉冲. MRI实验结果证明了该设计的可行性.%A radio frequency (RF) pulse generator for magnetic resonance imaging (MRI) was designed based on field programmable gate array (FPGA) and directdigital synthesis (DDS). The generator utilizes FPGA to achieve DDS and embed soft pulse waveform (RAM), multiplier and related control logic.The RF generator showed high technical specifications, with frequency, phase and amplitude resolution up to 32 bits, 16 bits and 16 bits, respectively. Time precision of the soft pulse waveform reached0.1ms.FPGA provided a programmable interface, facilitating the control from sequence controller and generation of RF pulses. The feasibility of the design was demonstrated with imaging experiments.【期刊名称】《波谱学杂志》【年(卷),期】2016(033)004【总页数】7页(P590-596)【关键词】磁共振成像(MRI);射频脉冲发生器;现场可编程门阵列(FPGA);直接数字频率合成(DDS)【作者】李聿为;肖亮【作者单位】北京化工大学信息科学与技术学院信息工程系,北京 100029;北京化工大学信息科学与技术学院信息工程系,北京 100029【正文语种】中文【中图分类】O482.53谱仪是磁共振成像(MRI)系统的核心设备,主要功能包括控制整个系统的时序、发射射频脉冲信号、发射用于空间定位的梯度信号、接收回波信号与传输数据等. 射频脉冲发生器是谱仪的重要组成部分[1-3],当序列运行时,其在序列控制器的控制下,产生指定参数的硬脉冲或者软脉冲用于驱动射频线圈,产生B1场[4]. 射频脉冲发生器发射信号的性能指标(包括频率精度、相位精度、幅度精度等)对磁共振图像质量有显著影响,因此世界上很多实验室都致力于研究高性能的、灵活可控的射频脉冲发生器[5-8].目前MRI系统的射频脉冲发生器多采用直接数字频率合成(DDS)技术[9,10],其中大部分采用DDS专用芯片来实现脉冲信号的发生[11-15]. 它的缺点在于信号的相位和幅度精度受到器件的限制,并且序列控制器对DDS专用芯片的控制不够灵活快速.本文设计了一种基于现场可编程门阵列(FPGA)的射频脉冲发生器,并将其配备于实验室自行研发的MRI谱仪之中. 在FPGA内部构建DDS、软脉冲波形(包括幅度和相位)双端口随机存取存储器(RAM)、乘法器以及相关的控制逻辑,其中DDS的频率、相位与幅度分辨率分别为32 bits、16 bits与16 bits,软脉冲波形的时间精度可达0.1 μs. 外部输入时钟为60 MHz,FPGA可通过锁相环将60 MHz时钟倍频到300 MHz,并将300 MHz时钟作为DDS的系统时钟,因而信号的输出频率范围可从直流到135 MHz,适用于0~3 T的MRI系统. 相比专用的DDS器件,以带有正交调制数据接口的数字上变频器AD9957为例(其工作频率最高可达1 GHz,信号输出频率范围为0~400 MHz),本文设计的射频脉冲发生器(其工作频率最高可达223 MHz,信号输出频率范围约为0~100 MHz),在工作频率和信号输出频率范围等性能上与AD9957有一定的差距,但是谱仪的序列控制器可通过本地总线配置FPGA的参数与数据来控制DDS的运行,使得设计更加灵活.本文设计的射频脉冲发生器主要由FPGA、数模转换器(DAC)、低通滤波器(LPF)、增益控制、乘法器、放大器和射频开关等器件组成,其结构框图如图1所示.FPGA提供了一个并行总线接口,序列控制器通过该接口与FPGA进行通信,通过简单的写指令操作就可以将射频发生的相关参数和数据配置到FPGA之中. 这些参数包括频率、相位、软脉冲波形数据(包括相位和幅度)、软脉冲参数(包括波形长度和时间精度)、射频发生控制参数(包括软、硬脉冲的选择和触发)和增益等. 随着序列的运行,打开射频开关,设置FPGA内部的控制寄存器,FPGA随即根据预设的参数自动地发生频率、相位、幅度等均可控的数字射频波形.FPGA芯片采用ALTERA公司Cyclone Ⅲ系列的EP3C25Q240,实现的功能包括数据锁存、数据存储、变频、计数、频率合成、相位累加、波形调制等,其设计可根据需要灵活进行调整.MAXIM公司的数模转换器MAX5885用于完成数字射频波形的数模转换.MAX5885的最高转换速率为200 MHz,字长为16 bits,输出具有较小的无杂散动态范围(SFDR):当系统时钟为100 MHz、输出为10 MHz时,SFDR为77dB. MAX5885的输出经过低通滤波后送到ADI公司的四象限乘法器AD834进行增益控制. 增益信号由LINEAR TECHNOLOGY公司的数模转换器LTC1657产生,它的字长为16 bits.经过增益调节的射频信号再由低噪宽带固定增益放大器——SIRENZA公司的SGA-4586放大,其增益大致为28 dB左右,噪声系数为1.7 dB. SGA-4586的输出经过射频开关——MACOM公司的SW-239(在序列控制器的控制下打开或关闭,切换时间为4 ns,隔离度为56 dB),最后馈送到射频功率放大器.图2是射频脉冲发生器电路板的实物照片.FPGA设计采用硬件描述语言(VHDL),在ALTERA公司的Quartus Ⅱ软件平台上进行编译. FPGA的结构设计如图3所示.FPGA内部的功能模块主要包括频率寄存器、相位寄存器、幅度寄存器、软脉冲相位存储器、软脉冲幅度存储器、相位累加器、加法器(叠加相位)、正弦查找表、乘法器(波形调制)以及控制单元. 频率寄存器字长为32 bits,当系统时钟为60 MHz时,频率精度约为0.014 Hz. 相位寄存器的字长为16 bits,相位精度约为0.005 5°. 软脉冲幅度存储器、软脉冲相位存储器大小均为4 k×16 bits. 正弦查找表的大小为16 k×16 bits,为提高查找表的利用效率,查找表只读存储器(ROM)中只存储1/4周期的正弦波幅度量化数据,利用正弦函数的对称性并进行实时计算得到整个周期的正弦波数据.DDS工作时,每一个时钟周期内频率字与相位累加器累加一次,得到位宽为32位的累加值,取高16位作为相位值叠加相位字后,再与相位寄存器的相位相加后以二进制码的形式去寻址正弦查找表,完成相位到幅度的转换. 该数字化波形序列经过数/模转换和低通滤波后,输出正弦波信号(信号频率就是相位累加器的溢出频率).射频信号()st表达式如下,其中()At为软脉冲波形幅度.产生中心频率为f0的射频信号,FPGA的频率字(FTW)可通过(2)式计算得到,其中SYSCLK为系统时钟[16].软脉冲幅度存储器为无符号整数,但是射频信号为有符号整数,因此相位寄存器的相位值(POW)可通过(3)式计算得到:其中Int函数为取整函数. 当()0At<时,如果POW大于最大值65 535,则对65 536取模后输出. 例如()0At<、相位为200°时,则POW为69 176,取模后得到POW为3 640.若需要产生硬脉冲,FPGA的DDS直接生成预定频率、相位的正弦信号,FPGA受触发后,打开射频开关,射频信号输出,持续一段时间后关闭射频开关,从而得到硬脉冲.若需要产生软脉冲,则需按以下基本流程操作:(1)序列控制器通过并行总线接口将射频发生的相关参数和数据配置到FPGA上,包括频率、相位、软脉冲波形数据、软脉冲参数、射频发生控制参数和增益等. (2)FPGA向用于增益控制的DAC赋值,实时调节输出射频波形的幅度.(3)FPGA受触发后,打开射频开关,启动软脉冲发生.(4)FPGA内部构建的计数器开始计数,该计数器以软脉冲波形的时间精度为周期,每当计数器计完一个周期时自动从存储器中依次读出调制波形数据,并以系统时钟为周期与查找表的正弦输出数据相乘,当指定调制波形长度的数据全部从存储器读出后,停止读数与相乘操作.(5)关闭射频开关.射频脉冲发生的实验结果(采用泰克公司的示波器DPO3034B进行测量)如图4所示,信号频率为14.79 MHz,幅度峰峰值为760 mV,输出阻抗为50 Ω.采用AGILENT公司的E4402B频谱分析仪对输出频率为14.79 MHz的射频信号进行频谱分析. 频谱分析结果如图5所示,偏离中心频率1 kHz范围内的相位噪声约为-73.9 dB/Hz;偏离中心频率1 MHz范围内的杂散约为-75.1 dB.将该射频脉冲发生器配备于实验室的自研谱仪,采集水模与人脑的磁共振图像,结果如图6所示. 系统磁场强度为0.3 T,射频功放采用ANALOGIC公司的AN8111,设置参数如下:软脉冲为3Sinc(256个点),视野大小(FOV)= 240 mm×240 mm,激发层厚(Slice Thickness)= 8 mm,扫描次数(NS)= 2,接收扫描带宽= 25 kHz,中心频率(SF)= 12.78 MHz. 该结果证明了此次设计的基于FPGA和DDS的射频脉冲发射器在实际应用中是可行的.提出了一种基于FPGA和DDS的MRI射频脉冲发生器的设计,此设计方法基于FPGA丰富的硬件资源、高速的运行时钟以及编程的灵活性,在FPGA内部构建DDS以及各功能单元,输出波形具有较高的频率、相位、幅度分辨率以及软脉冲时间精度,可应用于低场与高场(0~3 T)MRI谱仪. MRI实验结果证明了该设计的可行性.【相关文献】[1] Shen J, Xu Q, Liu Y, et al. Home-built magnetic resonance imaging system (0.3 T) witha complete digital spectrometer[J]. Rev Sci Instrum, 2005, 76(10): 105101.[2] Liu Min(刘敏), Qiu Wen-qi(邱雯绮), Sun Hui-jun(孙惠军), et al. Progress in the portable NMR spectrometer(便携式核磁共振谱仪的研究进展)[J]. Chinese J Magn Reson(波谱学杂志), 2014, 31(4): 504-514.[3] Chen Nan(陈楠), Chen Jie-hua(陈杰华), Hu Peng(胡鹏), et al. A digital transmitter for NMR based on FPGA(基于FPGA的核磁共振数字化发射机)[J]. Chinese J Magn Reson(波谱学杂志), 2008, 25(2): 243-249.[4] Xiao L, Sun B H, Ma Y P, et al. A digital magnetic resonance imaging spectrometer using digital signal processor and field programmable gate array[J]. Rev Sci Instrum, 2013, 84(5): 054702.[5] Ning Rui-peng(宁瑞鹏), Liu Yang(刘燕), Ren Jie-jing(任洁静), et al. Phase coherence between RF transmitter and receiver in digital MRI spectrometer(磁共振成像数字谱仪的射频发射/接收通道相位相干性的研究)[J]. Chinese J Magn Reson(波谱学杂志), 2007, 24(4): 439-445.[6] Mao Wen-ping(毛文平), Li Yun-yan(李云燕), Liu Zao(刘造), et al. A transmitter capable of fast modulation for NMR spectrometer-design and implementation(具有快速调制功能NMR发射机的设计与实现)[J]. Chinese J Magn Reson(波谱学杂志), 2013, 30(1): 13-20. [7] Ning R P, Yang G, Li G Y. A versatile pulse programmer for magnetic resonance imaging[J]. Rev Sci Instrum, 2011, 82(5): 054301.[8] Mao W P, Bao Q J, Yang L, et al. A modularized pulse programmer for NMR spectroscopy[J]. Meas Sci Technol, 2011, 22(2): 620-626.[9] Core S. Pulse Blaster DDS™ Model DDS-II-300 USB Owner’s Manual[M]. Florida: Spin Core Technologies InC, 2009.[10] Liu Hai-dan(刘海丹), Wang Hui-wang(王恢旺), Zhu Tian-xiong(朱天雄), et al. A frequency synthesizer for high-field NMR spectrometers(高场核磁共振波谱仪频率合成器设计)[J]. Chinese J Magn Reson(波谱学杂志), 2014, 31(1): 91-99.[11] Jiang Yu(蒋瑜), Shen Jian-hua(沈建华), Jiang Yun(蒋赟), et al. Application of the four DDS devices running in parallel to NMR(四路并行DDS合成技术在核磁共振中的应用)[J]. Chinese J Magn Reson(波谱学杂志), 2000, 17(6): 483-487.[12] Jiang Yun(蒋赟), Jiang Yu(蒋瑜), Tao Hong-yan(陶红艳),et al. DDS frequency source in NMR(用于核磁共振的直接数字合成频率源)[J]. Chinese J Magn Reson( 波谱学杂志), 2001,18(4): 291-295.[13] Ning Rui-peng(宁瑞鹏), Xu Qin(徐勤), Shen Jie(沈杰), et al. A PCI based complete digital frequency source for nuclear magnetic resonance spectrometer(基于PCI总线的全功能数字化频率源)[J]. Chinese J Magn Reson(波谱学杂志), 2006, 23(2): 209-215.[14] Xu Q, Christopher G, Zhou L, et al. An inexpensive and programmable RF transmitter setup for two-coil CASL[J]. Concept Magn Reson B, 2008, 33B(4): 228-235.[15] Xiao L, Wang W M. A radio-frequency source using direct digital synthesis and field programmable gate array for nuclear magnetic resonance[J]. Rev Sci Instrum, 2009, 80(12): 124703.[16] Bai Ju-xian(白居宪). Direct Digital Frequency Synthesis(直接数字频率合成)[M]. Xi’an(西安): Xi An Jiao Tong University Press(西安交通大学出版社), 2007.。