11100101序列检测器

时序电路设计-101序列检测器

数字逻辑设计及应用课程设计报告姓名:雷蕾学号:2010012030036选课号:设计题号: 5一.设计题目:设计101序列检测器二.设计要求要求使用状态机设计一个序列检测器,检测输入数据,当输入中出现101时,输出1,否则输出为0。

不进行重复判断,即当出现10101…时,输出为00100…判断的具体流程如下:1.电路复位,进入状态S0,等待输入2.S0状态下:如果输入为0,则停留在S0,如果输入为1,则跳转到S13.S1状态下:如果输入为0,则跳转到S2,如果输入为1,则停留在S14.S2状态下:如果输入为1,则输出1,并跳转到S0,如果输入为0,则输出0,并跳转到S0检测器电路实现:时钟信号,1 bit输入待判断信号,1bit输出判断结果。

三.设计过程1.设计方案:通过使用ISE编写verilog语言,实现以下过程:1s3只有当s3接收到的输入信号为1的时候,输出才会为1,其余时候输出都为0.2.设计程序:模块文件:`timescale 10ns/1ns//////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 21:02:40 06/06/2012// Design Name:// Module Name: abcd// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////////// module abcd(input reset,input clk,input ipt,output reg result);parameter [1:0] s0 = 2'b00, s1 = 2'b01, s2 = 2'b10;reg[1:0] state;always @ (posedge clk)beginif(reset)beginstate<=s0;result<=0;endelsebegincase(state)s0:beginif(ipt==0)beginstate<=s0;result<=0;endelse.beginstate<=s1;result<=0;endends1:beginif(ipt==0)beginstate<=s2;result<=0;endelsebeginstate<=s1;result<=0;endends2:beginif(ipt==0)beginstate<=s0;result<=0;endelsebeginstate<=s0;result<=1;endenddefault:beginstate<=s0;result<=0;endendcaseendendendmodule测试文件:`timescale 10ns / 1ps////////////////////////////////////////////////////////////////////////////// //// Company:// Engineer://// Create Date: 23:05:50 06/06/2012// Design Name: test_detector// Module Name: D:/TDDOWNLOAD/fortwo2/haha.v// Project Name: fortwo2// Target Device:// Tool versions:// Description://// Verilog Test Fixture created by ISE for module: test_detector//// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////// //module haha;module test_detector();reg clk;reg reset;reg ipt;wire result;reg[20:0] indata=20'b101001110011011110110;integer i;initial clk=1;always #1 clk=~clk;initialbeginreset=1;ipt=0;#4reset=0;for(i=0;i<21;i=i+1)beginipt=indata[i];#2;end#10$stop;endabcd detector_instance(.clk(clk),.reset(reset),.ipt(ipt),.result(result));endmodule3.仿真结果四.设计结论(包括:设计结果分析、设计中遇到的问题、设计心得和体会等) 1.设计结果分析:以时钟信号的一个周期为基准,有仿真结果可看出,当输入(ipt)为连续的一个周期高一个周期的低一个周期的高(即101)时,输出(result)为高。

序列检测器原理

序列检测器原理

序列检测器是一种用来检测和识别输入序列中特定模式的设备或算法。

它能够根据事先给定的规则或模型对输入序列进行分析和判断,并输出相应的结果或响应。

序列检测器通常由以下几个组成部分构成:

1. 输入接口:用于接收输入序列的信号或数据。

2. 存储器:存储检测器的状态信息和输入序列的历史数据。

3. 状态机:用于根据输入序列的不同模式进行状态转换和控制。

4. 判决逻辑:根据当前状态和输入序列的特征,判断当前模式是否匹配。

5. 输出接口:根据判决的结果,输出相应的响应或结果。

序列检测器的工作原理如下:

1. 初始化:将序列检测器的状态设为初始状态,准备接收输入序列。

2. 接收输入:逐个接收输入序列的信号或数据。

3. 状态转换:根据当前状态和输入序列的特征,根据事先设定好的规则或模型进行状态转换。

4. 判决匹配:根据当前状态和输入序列的特征,判断当前模式是否匹配。

5. 输出结果:根据判决的结果,输出相应的响应或结果。

6. 循环操作:重复执行2-5步骤,直至所有的输入序列被处理完毕。

通过以上的工作原理,序列检测器可以有效地检测和识别输入序列中的特定模式。

它在许多应用中都有广泛的应用,如通信领域中的错误检测、模式识别等。

序列检测器实验报告

序列检测器设计实验内容:设计一个1110010序列检测器,即检测器检测到序列1110010时,输出为1,否则输出为0。

输入信号:一个时钟输入信号clk;一个输入端x以输入序列来检测;一个输入y用来选择是检测序列1110010或是检测自己输入的序列;一个输入k(7..0)用来输入想要检测器检测的序列;输出信号:一个7位输出信号q,用来输出正在检测的7位序列;一个1位输出信号unlk,当被检测序列符合时,输出unlk为1否则为0;中间信号:再定义两个7位的中间信号a和combination;执行操作:在上升的时钟沿时候,将从x输入的序列赋给7位a,在y等于1的情况下,令中间信号combination为1110010,否则,在y等于0的情况下,令中间信号combination为从k输入的七位长序列。

最后把a的值赋给q,如果a与combination输出unlk等于1否则等于0。

(1)序列检测器语言设计:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;USE IEEE.STD_LOGIC_ARITH.ALL;entity xulie2 isport (clk,x:in std_logic;y:in std_logic;k:in std_logic_vector(7 downto 1);unlk:out std_logic;q:out std_logic_vector(7 downto 1)); end xulie2;architecture art of xulie2 issignal a:std_logic_vector(7 downto 1);signal combination: std_logic_vector(7 downto 1);beginprocess(clk)beginif clk'event and clk='1' thena<=a(6 downto 1)&x;if y='1' thencombination<="1110010";else combination<=k;end if;end if;q<=a;end process;unlk<='1' when(a=combination) else '0';end art;序列检测器波形图:其中ENDTIME=10.0us GRIDSIZE=100.0ns波形图分析:如图,选择输入端y输入为1时,q对应着输出从x输入的7位序列,如果从x输入的待检测的7位序列为1110010时,unlk为1,否则为0,当选择输入端y输入为0时,q依旧对应着输出从x输入的待检测的当前7为序列,但是只有当从x输入的7为序列与从k输入的7位序列一致时,输出端unlk才为1,否则为0。

实验三_用状态机实现序列检测器的设计Verilog

实验三用状态机实现序列检测器的设计一、实验目的:用状态机实现序列检测器的设计,并对其进行仿真和硬件测试。

二、原理说明:序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出a,否则输出b。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测过程中,任何一位不相等都将回到初始状态重新开始检测。

例3-1描述的电路完成对序列数"11100101"的。

当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“a”,否则仍然输出“b”。

【例3-1】//顶层文件:module XULIEQI(clk,reset,din18,LED7S);input clk;input reset;input [17:0] din18;output [6:0] LED7S;wire [3:0] AB;wire [17:0] din18;xulie u1 (clk, din18, reset, din);schk u2 (din,clk,reset,AB);decl7s u3 (AB,LED7S);endmodule//串行检测:module schk(DIN,CLK,CLR,AB);input DIN,CLK,CLR;output[3:0] AB;reg [3:0] AB;reg [7:0] Q;parameteridle = 8'b00000000,a = 8'b00000001,b = 8'b00000010,c = 8'b00000100,d = 8'b00001000,e = 8'b00010000,f = 8'b00100000,g = 8'b01000000,h = 8'b10000000;parameter data=8'b11100101;always @(posedge CLK or negedge CLR) if(!CLR)beginQ <= idle;endelsebegincase(Q)idle:beginif(DIN==data[7]) Q<=a;else Q<=idle;enda:beginif(DIN== data[6]) Q<=b;else Q<=idle;endb:beginif(DIN== data[5]) Q<=c;else Q<=idle;endc:beginif(DIN== data[4]) Q<=d;else Q<=c;endd:beginif(DIN== data[3]) Q<=e;else Q<=a;ende:beginif(DIN== data[2]) Q<=f;else Q<=idle;endf:beginif(DIN== data[1]) Q<=g;else Q<=b;endg:beginif(DIN== data[0]) Q<=h;else Q<=idle;endh:beginif(DIN== data[7]) Q<=a;else Q<=idle;enddefault :Q<=idle;endcaseendalways @(Q)beginif(Q==h) AB <= 4'b1010 ;else AB <= 4'b1011 ;endendmodule//前端预置8位数据输入:module xulie(clk, din18, reset, din);input clk;input[17:0] din18;input reset;output din;reg din;parameters0 = 5'b00000,s1 = 5'b00001,s2 = 5'b00010,s3 = 5'b00011,s4 = 5'b00100,s5 = 5'b00101,s6 = 5'b00110,s7 = 5'b00111,s8 = 5'b01000,s9 = 5'b01001,s10 = 5'b01010,s11 = 5'b01011,s12 = 5'b01100,s13 = 5'b01101,s14 = 5'b01110,s15 = 5'b01111,s16 = 5'b10000,s17 = 5'b10001;reg[4:0] cur_state,next_state;always @ (posedge clk or negedge reset) if(!reset)cur_state <= s17;elsecur_state <= next_state;always @ (cur_state or din18 or din ) begincase (cur_state)s17 : begindin <= din18[17];next_state <= s16;ends16 : begindin <= din18[16];next_state <= s15;ends15 : begindin <= din18[15];next_state <= s14;s14 : begindin <= din18[14];next_state <= s13;ends13 : begindin <= din18[13];next_state <= s12;ends12 : begindin <= din18[12];next_state <= s11;ends11 : begindin <= din18[11];next_state <= s10;ends10 : begindin <= din18[10];next_state <= s9;ends9 : begindin <= din18[9];next_state <= s8;ends8 : begindin <= din18[8];next_state <= s7;ends7 : begindin <= din18[7];next_state <= s6;ends6 : begindin <= din18[6];next_state <= s5;ends5 : begindin <= din18[5];next_state <= s4;ends4 : begindin <= din18[4];next_state <= s3;s3 : begindin <= din18[3];next_state <= s2;ends2 : begindin <= din18[2];next_state <= s1;ends1 : begindin <= din18[1];next_state <= s0;ends0: begindin <= din18[0];next_state <= s17;enddefault : begindin <= 1'b0;next_state <= s0;endendcaseendendmodule提示:1.若对于D <= "11100101 ",电路需记忆:初始状态、1、11、111 、1110 、11100、111001、1110010、11100101 共9种状态。

111序列检测器

“111”序列检测器1设计内容题目:“1 1 1”序列检测器。

原始条件:使用D触发器( 74 LS 74 )、“与”门 ( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计“1 1 1”序列检测器。

集成电路引脚图:图12设计要求1.能够运用数字逻辑的理论和方法,把时序逻辑电路设计和组合逻辑电路设计相结合,设计一个有实际应用的数字逻辑电路。

2.使用同步时序逻辑电路的设计方法,设计“1 1 1”序列检测器。

写出设计中的5个过程。

画出课程设计图。

3.根据74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路引脚号,在设计好的“1 1 1”序列检测器电路图中标上引脚号。

4.在试验设备上,使用74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路连接、调试和测试“1 1 1”序列检测器电路。

3设计原理及过程3.1建立原始状态图和状态表设计的序列检测器的功能是检测外部输入二进制代码中的“111”序列。

该同步时序逻辑电路有一个外部输入x和一个外部输出Z。

在作原始状态图时,一旦外部输入序列输入一个“1”,就要把它记载下来,因为这个“1”可能是“111”序列的第一个“1”。

紧接着下一个输入是否为“1”,因为“11”是外部输入“111”序列的前二位。

其后如果再输入一个“1”,外部输出就为“1”。

所以电路必须记住外部输入二进制代码中的“1”、“11”、“111”这3种输入情况。

每一种输入情况应该用一个状态记录下来。

根据要求,假设外部输入x的序列和相应的外部输出Z如下:外部输入x:0 1 1 0 1 1 1 0 0 0 1 1 1 1 0 1外部输出Z:0 0 0 0 0 0 1 0 0 0 0 0 1 1 0 0在建立原始状态图和状态表之前,并不知道实现上述逻辑功能的同步时序逻辑电路有多少个状态,可以指定某个状态为初始状态,在这里用A、B表示电路的不同状态。

实验三用状态机实现序列检测器的设计

仿真,分析结果

4、锁引脚

1)根据DE2_pin_assignments文件内容、格式制作 本设计引脚对应文件的引脚锁定文件: XUELIEQI.csv

• 由Processing->generate functional simulation netlist,提取功能仿真的网表

• 由processing -> start simulation 进行功能仿 真,并对结果进行分析。

• 时序仿真

• 由assignments->settings,更改仿真器的设置为 时序仿真:timing

• 双击波形文件下的空白区,得到如下对话框,点 击Noder Finder

弹出下面的对话框,单击List,选中AB、CLK、CLR 、DIN、Q几个端口,单击>_后,点击OK

• 由edit->end time ,设定仿真终止时间为 1us, 选中CLK点击 设置周期是10ns,

并对CLR,DIN作相应设置

• 由assigments->settings,对仿真工具设定为功 能仿真,并将激励文件调入

• 由Processing->generate functional simulation netlist,提取功能仿真的网表

• 由processing -> start simulation 进行功能仿

实验三 用状态机实现序列检测器的设计

任务分析

• 本次实验的核心是:应用有限状态机设计思路, 检测输入的串行数据是否是”11100101”。

使用D触发器设计一个11001序列检测器

使用D触发器设计一个11001序列检测器讨论使用D触发器设计一个11001序列检测器,讨论序列可交迭(Overlap)检测和不可交迭检测在设计上的区别,讨论分别采用Mealy机设计和采用Moore机设计的区别,讨论未用状态的处理问题。

【要求】给出电路原理图或HDL代码,要求进行仿真,并给出仿真结果。

1.原件介绍D触发器(74LS74)、“与”门(74LS08)、“或”门(74LS32)、“非”门(74LS04),集成电路引脚2.设计思路根据要求,设计的序列检测器有一个外部输入x 和一个外部输出Z 。

输入和输出的逻辑关系为:当外部输入x 第一个为"1",外部输出Z 为"0";当外部输入x 第二个为"1",外部输出Z 为"0";当外部输入第三个x 为"0",外部输出Z 为"0",当外部输入第四个x 为“0”,外部输出Z 为0,当外部输入第五个x 为“1”,输入X 0 1 1 1 0 0 1 0 1 输出Y 0 0 0 0 0 0 1 0 0要判别序列检测器是否连续接收了"11001",电路必须用不同的状态记载外部输入x 的值。

假设电路的初始状态为A ,x 输入第一个"1",检测器状态由A 装换到B ,用状态B 记载检测器接受了"11001"序列的第一个"1",这时外部输出Z=0;x 输入第二个"1",检测器状态由B 装换到C ,用状态C 记载检测器接了“11001”序列的第二个"1",外部输出Z=0;x 输入第三个"0",检测器状态由C 装换到D ,外部输出Z=0;x 输入第四个为“0”,检测器状态由D 装换到E ,外部输出Z=0;x 输入第五个为“1”,检测器状态由E 装换到F ,外部输出Z=1。

1010序列检测器

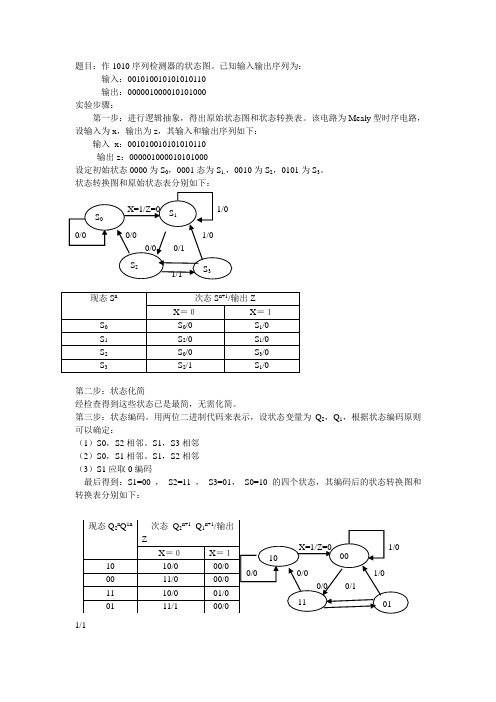

题目:作1010序列检测器的状态图。

已知输入输出序列为:

输入:001010010101010110

输出:000001000010101000

实验步骤:

第一步:进行逻辑抽象,得出原始状态图和状态转换表。

该电路为Mealy型时序电路,设输入为x,输出为z,其输入和输出序列如下:

输入x:001010010101010110

输出z:000001000010101000

设定初始状态0000为S0,0001态为S1.,0010为S2,0101为S3。

状态转换图和原始状态表分别如下:

第二步:状态化简

经检查得到这些状态已是最简,无需化简。

第三步:状态编码。

用两位二进制代码来表示,设状态变量为Q2,Q1,根据状态编码原则可以确定:

(1)S0,S2相邻。

S1,S3相邻

(2)S0,S1相邻。

S1,S2相邻

(3)S1应取0编码

最后得到:S1=00 ,S2=11 ,S3=01,S0=10的四个状态,其编码后的状态转换图和转换表分别如下:

1/1

第四步:选定触发器。

选用D触发器,由上图可以画出Z函数的卡诺图和各触发器状态Q2n+1和Q1n+1函数的卡诺图如下:

由D触发器的特性方程得到:

Q2Q1n

Z=X n

Q2n+1=D2=X

Q2+XQ2n Q1n

Q1n+1=D1=X n

第五步:画出其相应逻辑图如下:

第六步:判断是否自启动

因为本题没有无效状态,所以可以自启动。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

状态图:

状态表:

VHDL:

Library IEEE.;

Use.ieee.std_logic_1164.all;

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SCHK IS

PORT( DIN,CLK,CLR : IN STD_LOGIC ; --串行输入数据位/工作时钟/复位信号

AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); --检测结果输出

END SCHK;

ARCHITECTURE behav OF SCHK IS

SIGNAL Q : INTEGER RANGE 0 TO 8 ;

SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0); --8位待检测预置数

BEGIN

D <= "11100101 " ; --8位待检测预置数

PROCESS( CLK, CLR )

BEGIN

IF CLR = '1' THEN Q <= 0 ;

ELSIF CLK'EVENT AND CLK='1' THEN --时钟到来时,判断并处理当前输入的位CASE Q IS

WHEN 0=> IF DIN = D(7) THEN Q <= 1 ; ELSE Q <= 0 ; END IF ;

WHEN 1=> IF DIN = D(6) THEN Q <= 2 ; ELSE Q <= 0 ; END IF ;

WHEN 2=> IF DIN = D(5) THEN Q <= 3 ; ELSE Q <= 0 ; END IF ;

WHEN 3=> IF DIN = D(4) THEN Q <= 4 ; ELSE Q <= 0 ; END IF ;

WHEN 4=> IF DIN = D(3) THEN Q <= 5 ; ELSE Q <= 0 ; END IF ;

WHEN 5=> IF DIN = D(2) THEN Q <= 6 ; ELSE Q <= 0 ; END IF ;

WHEN 6=> IF DIN = D(1) THEN Q <= 7 ; ELSE Q <= 0 ; END IF ;

WHEN 7=> IF DIN = D(0) THEN Q <= 8 ; ELSE Q <= 0 ; END IF ;

WHEN OTHERS => Q <= 0 ;

END CASE ;

END IF ;

END PROCESS ;

PROCESS( Q ) --检测结果判断输出

BEGIN

IF Q = 8 THEN AB <= "1010" ; --序列数检测正确,输出“A”

ELSE AB <= "1011" ; --序列数检测错误,输出“B”

END IF ;

END PROCESS ;

END behav ;

提示:若对于D <= "11100101 ",电路需记忆:初始状态、1、11、111 、 1110 、11100、111001、1110010、11100101 共9种状态。