三位二进制减法计数器精选文档

三位二进制减法计数器设计审批稿

三位二进制减法计数器设计YKK standardization office【 YKK5AB- YKK08- YKK2C- YKK18】目录1课程设计的目的与作用1.了解同步计数器,序列信号发生器和N进制计数器工作原理;2.掌握计数器电路的分析,设计方法及应用;3.掌握序列信号发生器的分析,设计方法及应用;4.掌握N进制计数器的分析,设计方法及应用;5.学会正确使用JK触发器。

2 设计任务、及所用multisim软件环境介绍设计任务减法计数器1. 设计一个循环型3位2进制减法计数器,其中无效状态为(001,110)。

2. 根据同步计数器原理设计减法器的电路图。

3. 根据电路原理图使用Multisim进行仿真。

4. 将电路图进行实际接线操作。

5. 检查无误后,测试其功能。

1.2.2串行序列信号发生器1.设计一个序列信号发生器,其中信号序列为(101100)。

2.根据序列发生器原理设计发生器的原理图。

3.根据电路原理图使用Multisim进行仿真。

24进制计数器1. 用集成芯片设计一个24进制计数器2. 根据设计原理设计计数器原理图3. 根据电路原理图使用Mltisim仿真multisim软件环境介绍第一节 Multisim概貌软件以图形界面为主,采用菜单、工具栏和热键相结合的方式,具有一般Windows应用软件的界面风格,用户可以根据自己的习惯和熟悉程度自如使用。

一、Multisim的主窗口界面。

启动Multisim 12后,将出现如图所示的界面。

图 multism 12启动后所示界面界面由多个区域构成:菜单栏,各种工具栏,电路输入窗口,状态条,列表框等。

通过对各部分的操作可以实现电路图的输入、编辑,并根据需要对电路进行相应的观测和分析。

用户可以通过菜单或工具栏改变主窗口的视图内容。

二、菜单栏菜单栏位于界面的上方,通过菜单可以对Multisim的所有功能进行操作。

不难看出菜单中有一些与大多数Windows平台上的应用软件一致的功能选项,如File,Edit,View,Options,Help。

3位2进制同步计数器(约束项:000,010)

图a

图2.2.3电位器左端时刻仿真图1

图b:

图2.2.4电位器左端时刻仿真图2

(3)估算当电位器滑动端调至最右端时,由图(a)可得

Uom=4.877V Ucm=2.809V T=7.836ms

由图(b)可得:

T2=1.586ms ,所以T1= T—T2=7.836ms—1.586ms=6.25ms

1.3ms

5.2ms

0.2

仿真结果

1.68ms

6.063ms

0.217

(3)当电位器的滑动端调至最右端时

T1

T2

D

估算结果

5.2ms

1.3ms

0.8

仿真结果

6.25ms

1.586ms

0.798

对比表中的估算结果和仿真结果,数值有较大的误差,其误差原因是在仿真中二极管影响输入波的周期,以及读数的误差。总的来看,估算的结果和仿真的结果是一致的。

(4)状态方程:

电路次态卡诺图:

图1.3.2电路次态卡诺图

Q1N+1的次态卡诺图为:

图1.3.3Q1N+1的次态卡诺图

Q0N+1的次态卡诺图为:

图1.3.4Q0N+1的次态卡诺图

状态方程:

Y= Q1nQ0n

= +

= +X =

(5) 驱动方程为 :

= =

= =1

(6) 检查能否自启动(无无效状态)

(7) 最后结果

1数字电子设计部分

1.1

(1)了解同步加法计数器工作原理和逻辑功能。

(2)掌握计数器电路的分析,设计方法及应用。

(3) 学会正确使用JK触发器。

三位二进制减法计数器与芯片仿真进制减法计数器

目录1 课程设计的目的与作用 01.1课程设计目的 02 所用multisim软件环境介绍 02.1 Multisim软件环境介绍 02.2 Multisim软件界面介绍 (1)3设计任务 (2)3.1设计的总体框图 (2)3.1.1三位二进制减法计数器的总体框图 (2)3.1.2 串行序列信号检测器的总体框图 (2)3.1.3 74193芯片仿真63进制减法计数器原理 (2)3.2设计过程 (2)3.2.1 三位二进制同步减法计数器 (2)3.2.2串行序列信号检测器 (4)3.2.3 74193芯片仿真63进制减法计数器 (5)4实验仪器 (6)4.1三位二进制减法器 (6)4.2串行序列检测器 (6)4.3 74193芯片仿真63进制减法器计数 (6)5仿真结果分析 (6)5.1三位二进制同步减法计数器的电路原理图及结果 (6)5.2串行序列信号检测器电路原理图及结果 (7)5.3 74193芯片仿真63进制减法计数器的电路原理图及结果 (7)6设计总结和体会 (8)7参考文献 (8)1 课程设计的目的与作用1.1课程设计目的1.通过Multisim的仿真设计,掌握Multisim软件的基本使用方法;2.学会在multisim环境下建立电路模型,能进行正确的仿真;3.通过Multisim的仿真,熟练掌握三位二进制同步加法计数器和串行序列检测器电路,10000串行序列检测器电路设计;4.学会分析仿真结果的正确性,与理论计算值进行比较;5.通过课程设计,加强动手,动脑的能力。

2 所用multisim软件环境介绍2.1 Multisim软件环境介绍Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。

它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。

Multisim 10 启动画面图工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。

32进制同步减法计数器设计解析

目录一、设计目的 (1)二、设计原理 (1)三、设计 (1)3.1设计思路 (1)3.2设计步骤 (1)四、QuartusⅡ9.0操作步骤 (3)五、程序 (4)5.1完整程序 (4)5.2仿真程序 (8)六、仿真 (12)6.1仿真结果 (12)6.2仿真结果分析 (12)七、引脚分配 (13)八、课程设计总结 (14)参考文献 (15)一、设计目的1)巩固和加深对“EDA技术””的基本知识的理解,提高综合运用本课程所学知识的能力。

2)培养学生根据课题需要选学参考书籍、查阅手册、图表和文献资料的自学能力。

通过独立思考,深入钻研相关问题,学会自己分析解决问题的方法。

3)培养硬件设计、软件设计及系统软、硬件调试的基本思路、方法和技巧,并能熟练使用当前较流行的一些有关电路设计与分析的软件和硬件。

二、设计原理计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种。

本次设计是32进制同步减法计数器。

32进制的二进制范围为“00000”到“11111”,即十进制0~31。

当显示的数小于31时,数字将自减,减至0时又跳会预先输入的数,如此循环。

系统提供50MHZ频率的时钟源,输入的数字信号由实验装置上的开关给定,输出由LED完成,同时数码管显示输入和输出的数字信号。

设置2个按钮,一个作“开始”,即使能端en,一个作系统“复位”res。

三、设计3.1设计思路本次程序设计的思路主要是分模块进行。

32进制同步减法计数器的基本工作原理是循环自减,因此得需要一个自减VHDL的程序。

系统提供50MHZ频率的时钟源,频率太大,肉眼无法观察,得需要一个分频的程序。

数字电子设计3位2进制同步计数器(约束项:000,010)串行序列信号检测器矩形波发生电路求和电路

数字电⼦设计3位2进制同步计数器(约束项:000,010)串⾏序列信号检测器矩形波发⽣电路求和电路课程设计任务书⽬录1数字电⼦设计部分 (1)1.1课程设计的内容和要求 (1)1.2计数器设计原理 (1)1.2.1三位⼆进制同步计数器状态图(000,010) (1)1.2.2选择触发器、求时钟⽅程、输出⽅程、状态⽅程和结果 (1) 1.2.3逻辑接线图 (4)1.2.4仿真结果 (5)1.3串⾏序列检测器设计原理 (8)1.3.2选择触发器、求时钟⽅程、输出⽅程、状态⽅程和结果 (8) 1.3.3、逻辑接线图 (11)1.3.4.仿真结果 (11)1.4 设计总结和体会 (13)2.模拟电⼦设计部分 (14)2.1课程设计的⽬的 (14)2.2矩形波发⽣器 (14)2.2.1简单原理及性能指标 (14)2.2.2结论 (15)2.2.3矩形波发⽣电路的仿真 (16)(1)仿真电路图 (16)(2)仿真波形及数据 (17)2.2.4结果分析 (22)2.3反相输⼊求和运算电路 (22)2.3.1简单原理及性能指标 (22)2.3.2结论 (23)2.3.3反相输⼊求和电路仿真 (23)图2.3.1反向输⼊求和电路仿真图 (24)(2)仿真结果 (24)图2.3.2仿真结果 (24)2.4误差分析 (24)2.4.1误差因素 (24)2.4.2改进⽅法 (25)2.5.设计总结和体会 (25)3.参考⽂献 (25)1数字电⼦设计部分1.1课程设计的内容和要求(1)了解同步加法计数器⼯作原理和逻辑功能。

(2)掌握计数器电路的分析,设计⽅法及应⽤。

(3)学会正确使⽤JK触发器。

1.2计数器设计原理1.2.1三位⼆进制同步计数器状态图(000,010)0011.2.2选择触发器、求时钟⽅程、输出⽅程、状态⽅程和结果(1)选择触发器由于JK触发器功能齐全、使⽤灵活,故选⽤3个下降沿JK触发器。

(2)求时钟⽅程CP0=CP1=CP2=CP(3)求输出⽅程输出⽅程的卡诺图为:图1.2.1输出⽅程的卡诺图(4)状态⽅程:次态卡诺图:N+1的次态卡诺图为:Q2N+1的次态卡诺图图1.2.2Q2Q1N+1的次态卡诺图为:N+1的次态卡诺图图1.2.3Q1N+1的次态卡诺图为QN+1的次态卡诺图图1.2.4 Q状态⽅程:Q2n+1=+=+=+(5) 驱动⽅程为:===1===(6) 检查能否⾃启动(⽆效状态000、010)000 001010 011所以能⾃启动。

二进制计数器

19

5.2.2 同步二进制计数器

同步计数器中,各触发器的翻转与时钟脉冲同步。 同步计数器的工作速度较快,工作频率也较高。

1.同步二进制加法计数器

(1)设计思想:

① 所有触发器的时钟控制端均由计数脉冲CP输

入,CP的每一个触发沿都会使所有的触发器状态更

新。

② 应控制触发器的输入端,可将触发器接成T

触发器。

2019/5/2

(a) 电路图 (b)时序图

12

2.异步二进制减法计数器

必须满足二进制数的减法运算规则:0-1不够减, 应向相邻高位借位,即10-1=1。

组成二进制减法计数器时,各触发器应当满足: ① 每输入一个计数脉冲,触发器应当翻转一次 (即用T′触发器); ② 当低位触发器由0变为1时,应输出一个借位信 号加到相邻高位触发器的计数输入端。

等效十进制数 0 1 2 3 4 5 6 7 0

2019/5/2

8

④ 时序图

图5-13 3位二进制加法计数器的时序图

2019/5/2

9

⑤ 状态转换图

圆圈内表 示Q2Q1Q0

的状态

用箭头表 示状态转 换的方向

图5-14 3位二进制加法计数器的状态转换图

2019/5/2

10

⑥ 结论

如果计数器从000状态开始计数,在第八个计 数脉冲输入后,计数器又重新回到000状态,完成 了一次计数循环。所以该计数器是八进制加法计 数器或称为模8加法计数器。

24

2.同步二进制减法计数器

(1)设计思想: ① 所有触发器的时钟控制端均由计数脉冲CP输入,

CP的每一个触发沿都会使所有的触发器状态更新。 ② 应控制触发器的输入端,可将触发器接成T触发

三位二进制减法计数器真值表

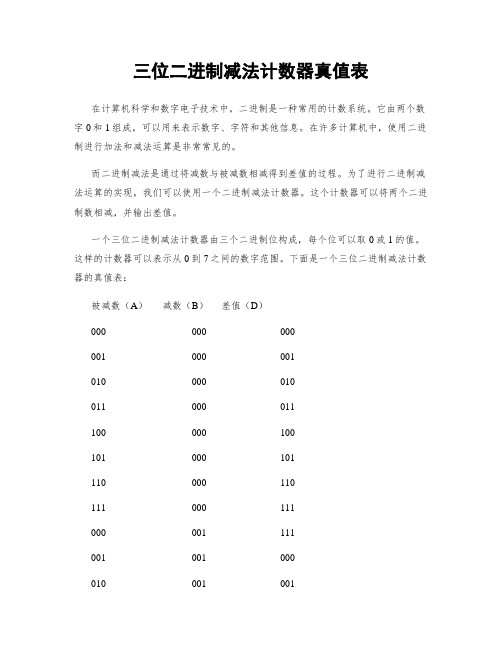

三位二进制减法计数器真值表在计算机科学和数字电子技术中,二进制是一种常用的计数系统。

它由两个数字0和1组成,可以用来表示数字、字符和其他信息。

在许多计算机中,使用二进制进行加法和减法运算是非常常见的。

而二进制减法是通过将减数与被减数相减得到差值的过程。

为了进行二进制减法运算的实现,我们可以使用一个二进制减法计数器。

这个计数器可以将两个二进制数相减,并输出差值。

一个三位二进制减法计数器由三个二进制位构成,每个位可以取0或1的值。

这样的计数器可以表示从0到7之间的数字范围。

下面是一个三位二进制减法计数器的真值表:被减数(A)减数(B)差值(D)000 000 000001 000 001010 000 010011 000 011100 000 100101 000 101110 000 110111 000 111000 001 111001 001 000010 001 001011 001 010 100 001 011 101 001 100 110 001 101 111 001 110 000 010 110 001 010 111 010 010 000 011 010 001 100 010 010 101 010 011 110 010 100 111 010 101 000 011 101 001 011 110 010 011 111 011 011 000 100 011 001 101 011 010 110 011 011 111 011 100000 100 011 001 100 100 010 100 101 011 100 110 100 100 111 101 100 000 110 100 001 111 100 010 000 101 010 001 101 011 010 101 100 011 101 101 100 101 110 101 101 111 110 101 000 111 101 001 000 110 001 001 110 010 010 110 011 011 110 100 100 110 101101 110 110110 110 111111 110 000000 111 000001 111 001010 111 010011 111 011100 111 100101 111 101110 111 110111 111 111在这个真值表中,被减数(A)和减数(B)分别取0和1的所有情况下,都列出了对应的差值(D)。

数电课设三位同步二进制减法器串行序列检测电路设计

目录1 .数字电子课程设计的目的与作用 (1)2 .课程设计的任务 (1)3. 三位同步二进制减法器 (1)3.1. 三位同步二进制减法器设计电路的理论分析 (1)3.1.1原始状态图的建立: (1)3.1.2卡诺图 (2)3.1.3时钟方程、输出方程和状态方程: (3)3.1.4无效状态的判断 (4)3.2. 三位同步二进制减法器设计电路 (4)3.3.三位同步二进制减法器的仿真结果 (5)4.串行序列检测电路设计 (8)4.1.串行序列检测电路设计电路的理论分析 (8)4.1.1原始状态图的建立: (8)4.1.2卡诺图 (9)4.1.3时钟方程、输出方程和状态方程: (10)4.2.串行序列检测设计电路 (10)4.3串行序列检测器的仿真结果 (11)5.用数据选择器实现函数F=AB+BC+CA (13)5.1用数据选择器实现函数F=AB+BC+CA的电路设计 (13)5.1.1选择数据译码器 (13)5.1.2写标准与非—与非表达式 (13)5.1.3确定数据选择器输入变量的表达式 (13)5.2用数据选择器实现函数F=AB+BC+CA的设计电路 (14)5.3实验结论 (14)6.设计总结和体会 (14)7.参考文献 (15)1 .数字电子课程设计的目的与作用随着科技的进步和社会的发展,数字电路在各种电器中的应用越来越广泛。

0、1代码的简易变换能够实现复杂的逻辑功能使得数字电路的实现效率很高。

课程设计的目的是通过实际设计并搭建一些简易但典型的数字电路来加深对各逻辑器件逻辑功能的理解。

课程设计能够使我们更进一步理解课堂上所学的理论知识,同时又能锻炼我们的动手能力和分析问题解决问题的能力。

2 .课程设计的任务利用所学的数字电路的理论知识,用JK触发器、74LS00、74LS08等逻辑门在数字电路系统上设计并搭建000、010为无效状态的三位同步二进制减法器以及串行序列1001的检测电路,注意检查其中的无效状态能否自行启动,若不能自启进行相应的逻辑修改,直至符合设计要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

三位二进制减法计数器

精选文档

TTMS system office room 【TTMS16H-TTMS2A-TTMS8Q8-

成绩评定表

课程设计任务书

目录

1 课程设计的目的与作用

1.了解同步计数器及序列信号发生器工作原理;

2.掌握计数器电路的分析,设计方法及应用;

3.掌握序列信号发生器的分析,设计方法及应用

2 设计任务

三位二进制同步减法计数器

1.设计一个循环型三位二进制减法计数器,其中无效状态为(000,110),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

串行序列发生器的设计

1.设计一个能循环产生给定序列的串行序列信号发生器,其中发生序列(1101),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

基于74191芯片仿真设计54进制减法计数器并显示计数过程

1.设计一个基于74191芯片仿真设计54进制减法计数器并显示计数过程,组合电路部分选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

3设计原理

三位二进制减法计数器

1.计数器是用来统计输入脉冲个数电路,是组成数字电路和计算机电路的基本时序逻辑部件。

计数器按长度可分为:二进制,十进制和任意进制计数器。

计数器不仅有加法计数器,也有减法计数器。

如果一个计数器既能完成累加技术功能,也能完成递减功能,则称其为可逆计数器。

在同步计数器中,个触发器共用同一个时钟信号。

2.时序电路的分析过程:根据给定的时序电路,写出各触发器的驱动方程,输出方程,根据驱动方程带入触发器特征方程,得到每个触发器的次态方程;再根据给定初态,一次迭代得到特征转换表,分析特征转换表画出状态图。

是输入计数脉冲,所谓计数,就是记CP脉冲个数,每来一个CP脉冲,计数器就加一个1,随着输入计数脉冲个数的增加,计数器中的数值也增大,当计数器记满时再来CP脉冲,计数器归零的同时给高位进位,即要给高位进位信号。

串行序列发生器的设计

1.序列是把一组0,1数码按一定规则顺序排列的串行信号,可以做同步信号地址码,数据等,也可以做控制信号。

2.计数型序列信号发生器是在计数器的基础上加上反馈网络构成。

要实现序列长度为M 序列信号发生器。

其设计步骤为:

a.先设计一个计数模值为M的计数器;

b.再令计数器每一个状态输出符合序列信号要求;

c.根据计数器状态转换关系和序列信号要求设计输出组合网络

3.3 74191芯片仿真设计54进制减法计数器并显示计数过程

1.写出的二进制代码

2.求归零逻辑

3.异步置数的值

4实验步骤

三位二进制减法计数器(无效状态000,110)

所给无效状态为000、110,对其余有效状态进行逻辑抽象可以得到减法器设计电路的原始状态图如图所示: 加法真值表:

图状态转移表

三位二进制加法计数器的总体框图

输入脉冲

图三位二进制加法计数器的总体框图

(1)状态图

图减法器的状态图 (2)选择的触发器名称:选用三个CP 下降沿触发的边沿JK 触发器 (3)输出方程:Y= Q —

2n

Q —

n 1 Q 0n (4)状态方程

n

n

Q

图电路次态的卡诺图

n n

Q

n n

Q

图 1

1

+n Q 的卡诺图

n n

Q

图 1

+n Q 的卡诺图

由卡诺图得出状态方程为:

Q 2n+1=n

Q 20Q +n Q 2n

Q 1

Q 1n+1 =n

Q 10Q +012Q Q Q +21Q Q Q 0n+1=n

Q 0+(12Q Q +12Q Q )0Q

(5)驱动方程

0J =1 1J =02Q Q 2J =1Q 0K = Q 1̅̅̅Q 2̅̅̅̅̅ Q 1Q 2̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 1K =20Q Q 2K =0Q

(6)时钟方程 0CP =1CP =2CP =3CP

图设计电路的逻辑电路图 (7)仿真结果

状态1

状态2 状态3 状态4

状态5

状态6 (进位端为高电平)串行序列发生器的设计

串行序列信号发生器的总体框图:

图串行序列信号发生器的总体框图

(1)状态图

(2) 进行状态分配

S 0=00 S 1=01 S 2=10 S 3=11

(3)选择的触发器名称:选用两个CP 下降沿触发的边沿JK 触发器 (4)输出方程:Y= X Q —

1n Q —

0n (5)状态方程

n n

图输出状态Y的卡诺图

n n

图0Q 1Q 次态图

n n

图1

1

+n Q 次态状态图

n n

图1

+n Q 次态状态图

由卡诺图得出状态方程为: 1+n Q =J n Q +n Q K

1

1

+n Q =10Q Q +X 10Q Q

1

+n Q =X Q 1N

0Q +(X Q —

1n

+X —

Q 1n ) Q 0n

(6)驱动方程

1J =X 0Q 0J =X ○+n Q 1 1K =n Q 0 0K =n XQ 1 Y=X n

Q 1n Q 0

(7)逻辑电路图

图串行序列1101检测电路

(8)仿真结果

输入X=1,触发器变为01,Y=0

输入X=1,触发器变为10,Y=0

输入X=0,触发器变为11,Y=0

输入X=1, Y=1

74191芯片仿真设计54进制减法计数器并显示计数过程

1)写出的二进制代码

1111 1111 (255 FFH)

1111 1110 (254 FEH)

54个数

…

1100 1010 (202 CAH)

2)求归零逻辑

因为L—D—是异步置数端,所以返回值应为1100 1001

L—D—=Q5n Q4n Q2n Q1n

3)画连线图

(4)仿真结果

第一个数 FFH

第二个数 FEH

第三个数 FDH

?

?

第54个数 CAH

5 仿真结果分析

实验结果可通过数字显示器的数字变化观察计数器的工作情况,容易验证电路是否正确。

1.三位二进制减法计数器,小灯会按照111,101,100,011,010,001的顺序循环变化,证

明 000,110不存在的约束项,电路连接正确。

2.序列信号发生器,当依次输入1101时,输出Y为1,证明设计合理且电路连接正确。

3.仿真运行时,显示器从FFH ~CAH依次进行减法计数.

6 设计总结

通过本次课程设计使我对同步计数器及序列信号发生器工作原理有了更深的了解,同时掌握计数器电路的分析,设计方法及应用和序列信号发生器的分析,设计方法及应用,基本能够独立设计出一般简单的电路

7 参考文献

1.《数字电子技术基础简明教程》余孟尝主编;清华大学电子学教研组编.——3版.——北京:高等教育出版社,(2007重印)

2.张利萍.王向磊编.《数字电子技术实验》. 沈阳:沈阳理工大学出版

3.童诗白,徐振英. 现代电子学及应用. 北京:高等教育出版社,

4.黄培根奚慧平主编浙江大学出版社 2005年2月第一版Multisim 7&电子技术实验。