计算机接口与微机原理-第14周-DMA控制器8237A-b

可编程DMA控制8237A

0禁止存储器到存储器传输 1允许存储器到存储器传输

0禁止通道0地址保持不变 1允许存储器到存储器传输 XD0=0时不起作用

0允许8237A操作 1禁止8237A操作

0正常时序 1压缩序 XD0=1不起作用

图12-4 命令寄存器

7.请求寄存器(RR)

8237A的4个通道都有一个于其相对应的请求触发器, 它是用来设置DMA请求标志的。在8237A控制器内,是4 个请求触发器对应1个DMA请求寄存器。我们知道,DMA 请求可以由硬件发出,也可由软件发出,对于硬件是通 过DREQ引脚引入DMA请求的,对于软件,则是通过对DMA 请求标志的设置来发出请求的,在存储器与存储器进行 数据传输时,因没有外部DREQ请求信号,因此,由软件 产生一个DMA请求信号来启动,DMA传输请求寄存器的格 式如图12-5所示。

2.当前字数寄存器(CWCR)

它用于存放当前的字节数,最大可达64KB。每一个通道都有一个16位 的当前字计数寄存器。在DMA传送操作时,每传送一个字节,该寄存器的内 容减1,当计数值变为零时,便自动产生终止计数信号。在编程状态下, CPU以字节为单位进行操作。在自动预置方式下,当计数减为0或出现有效 低电平时,基字计数寄存器(BWC)可自动地将初始值重新装入CWCR。

7 65 4 3 2 1 0

00选择请求方式 01选择单字节方式 10选择块方式 11选择级联方式

0选择地址增量 1选择地址减量

0禁止自动预置 1允许自动预置

00选择通道0 01选择通道1 10选择通道2 11选择通道3

00效验传输 01写传输 10读传输 11非法 XX若D7D6=11,则无效

图12-2 工作方式寄存器

(2)综合屏蔽命令格式(或称为主屏蔽寄存器)。其格 式如图12-6(b)所示。8237A允许使用综合屏蔽命令一 次完成对4个通道的屏蔽设置。

微机原理与接口技术实验十二 8237 DMA传送实验

实验十二8237 DMA传送实验一、实验目的(1)掌握DMA方式的工作原理和8237DMA控制器的编程使用方法。

(2)掌握如何在实验系统环境下,使用DMA的CH0进行数据传送。

二、实验内容利用本实验系统提供的8237A-5 DMA控制的CH0,实现DMA的内存到内存的读、写传送,采用DMA软件请求,把内存中3000H~4FFFH单元内容传送到5000H~6FFFH单元中。

三、编程指南1、8237A引脚图图6-62、8237A的内部寄存器格式⑴8237A控制寄存器格式(2) 8237A模式寄存器格式(3)8237A状态寄存器格式(4)请求寄存器和屏蔽寄存器格式(5)多通道屏蔽寄存器格式(6)8237A端口地址3、8237A的初始化编程⑴命令字写入控制寄存器⑵方式字写入模式寄存器⑶屏蔽字写入屏蔽寄存器⑷写先/后触发器⑸写入基地址和当前地址寄存器以及基字节和当前字节计数器。

⑹写入请求寄存器如果采用软件DMA请求,在适当的时候令通道的请求触发器置1。

四、实验接线图图6-7五、实验步骤连CS10到8000H,在系统内存3000H~4FFFH单元中填充10,11,12,13……,运行程序8237·ASM或在实验系统处于P态下,按SCAL键,然后在系统内存3000H~4FFFH 单元中填充10,11,12,13……,输入2860,按EXEC键即可,当系统显示“8237——good”表示DMA传送结束,按RST钮,返回P态,用内存读写命令检查5000H~6FFFH单元内容是否和3000H~4FFFH单元内容相一致,验证其正确性。

六、实验程序清单;8237.ASM,MOV:RAM FROM 3000H TO 5000H;BYTE-MOVCODE SEGMENTASSUME CS:CODEPCTL EQU 0FF20H ;控制口PA EQU 0FF21H ;字位口PB EQU 0FF22H ;字形口PC EQU 0FF23H ;键入口CLEARF EQU 800CHCH0A EQU 8000hCH1A EQU 8002HCH1C EQU 8003HMODE EQU 800BHCMMD EQU 8008HMASKS EQU 800FHREQ EQU 8009HSTATUS EQU 8008Hrst equ 800dhLATCH EQU 9000HORG 2860H ;FORM EPROM FILE (.COM),SET ORG= 0100HSTART: JMP START0BUF DB ?,?,?,?,?,?data1: db 0c0h,0f9h,0a4h,0b0h,99h,92h,82h,0f8h,80h,90h,88h,83h,0c6h,0a1hdb 86h,8eh,0ffh,0ch,89h,0deh,0c7h,8ch,0f3h,0bfh,8FHSTART0: MOV SI,3000HMOV DI,5000HMOV CX,1FFFHMOV AL,00MOV DX,LATCHOUT DX,ALNOPNOPmov dx,rstout dx,alMOV DX,CLEARFOUT DX,ALMOV AL,0FH ;MASK_CH_0-3MOV DX,MASKSOUT DX,ALNOPNOPMOV DX,CH0A ;L-SADMOV AX,SIOUT DX,ALMOV AL,AHOUT DX,ALNOPNOPMOV DX,CH1A ;L-DADMOV AX,DIOUT DX,ALMOV AL,AHOUT DX,ALNOPNOPMOV AX,CX ;COUNTMOV DX,CH1COUT DX,ALMOV AL,AHOUT DX,ALMOV AL,48H ;P_MODEMOV DX,MODEOUT DX,ALMOV AL,45HOUT DX,ALMOV AL,01H ;ON-8237MOV DX,CMMDOUT DX,ALL1: MOV AL,0EH ;UNMASK_CH_0MOV DX,MASKSOUT DX,ALMOV AL,04H ;START_DMA_TRANSFERMOV DX,REQOUT DX,ALMOV DX,STATUSNOPNOPWAIT1: IN AL,DXTEST AL,03HJZ WAIT1; CALL CMP1; JNZ ERRMOV DX,CH1CIN AL,DXMOV AH,ALCMP AX,0FFFFHJNZ L1CALL BUF1MOV CX,0080HL2: PUSH CXCALL DISPPOP CXLOOP L2CALL BUF2L3: CALL DISPJMP L3;---------------------------------------------CMP1: MOV DX,CH0ACALL CMP10MOV SI,AXMOV DX,CH1ACALL CMP10MOV DI,AXMOV AX,[SI]CMP [DI],AXRETCMP10: IN AL,DXMOV BL,ALIN AL,DXMOV AH,ALMOV AL,BLDEC AXRETERR: CALL BUF3ERR0: CALL DISPJMP ERR0;---------------------------DISP: MOV AL,0FFH ;00HMOV DX,PAOUT DX,ALMOV CL,0DFH ;20H ;显示子程序,5msMOV BX,OFFSET BUFDIS1: MOV AL,[BX]MOV AH,00HPUSH BXMOV BX,OFFSET DATA1ADD BX,AXMOV AL,[BX]MOV DX,PBOUT DX,ALMOV AL,CLMOV DX,PAOUT DX,ALPUSH CXDIS2: MOV CX,00A0HDELAY: LOOP DELAYPOP CXCMP CL,0FEH ;01HJZ LX1INC BXROR CL,1 ;SHR CL,1JMP DIS1LX1: MOV AL,0FFHMOV DX,PBOUT DX,ALRETBUF1: MOV BUF,08HMOV BUF+1,02HMOV BUF+2,03HMOV BUF+3,07HMOV BUF+4,17HMOV BUF+5,17HRET;------------------------------------------------------------- BUF2: MOV BUF,09HMOV BUF+1,00HMOV BUF+2,00HMOV BUF+3,0DHMOV BUF+4,10HMOV BUF+5,10HRETBUF3: MOV BUF,08HMOV BUF+1,02HMOV BUF+2,03HMOV BUF+3,07HMOV BUF+4,18HMOV BUF+5,18HRETCODE ENDSEND START。

可编程DMA控制器8237A

图7.5.5 DMA的读/写总线周期 ·非总 线信 号 (a) DMA读操作; (b) DMA写操作

(3) 8237几个特殊操作的说明。

S1 CLK AEN A8~A15 A 0~A7 RD WR 扩展 码 CLK A 0~A7 RD WR (b ) S2 S1 S2 (a) S1 S2 有效 有 效 S2 S3 S4 S2 S3 S4

定时 和 控制

A4~A7 输出缓冲

A8~ A15

命令 控制

写缓冲 DREQ0~ 4 DREQ3 HRQ HLDA DACK0~ 4 DACK3

读缓冲 据总线 I/O 缓冲 DB0~DB7

内部数 优先级 编号和 旋转优先 级逻辑 命令(8)

屏蔽(4)

读写 模式 (4×6) 状态(8) 临时(8)

请求(4)

设置命令寄存器

初始化必须设置命令寄存器,以确定其工作时序、 优先级方式、DREQ和DACK的有效电平及是否允许工 作等。

清除先/后触发器

先/后触发器是一个指针,当它为0时,对低字节进 行操作,当它为1时,对高字节进行操作。

设置地址和字节计数器

8237A每个通道有四个16位的寄存器。这四个寄存器 是基地址寄存器和当前地址寄存器以及基本字节计数 寄存器和当前字节计数寄存器。

7.5.2 DMA的工作方式、 操作类型及时序

1. 8237 DMA的工作方式及传输操作类型

(1) 8237的 4 种工作方式。 ① 单字节传送方式。在这种方式下, 每次仅传送一个字节数据。 传送

后,字节数寄存器减1,地址寄存器加1或减1(由初始化编程决定)。 HRQ变

为无效,8237释放系统总线,控制权返回给CPU。 当前字节数寄存器从初始 值减到0,还要再传输一个字节,又从0减到0FFFFH时,才发出有效EOP信号, 结束DMA传输过程。 通常,在DACK成为有效之前,DREQ必须保持有效。每次传送后, DMA控制器把总线让给CPU至少一个总线周期,且立即开始检测DREQ输入, 一旦DREQ为有效, 再进行下一个字节的传送。

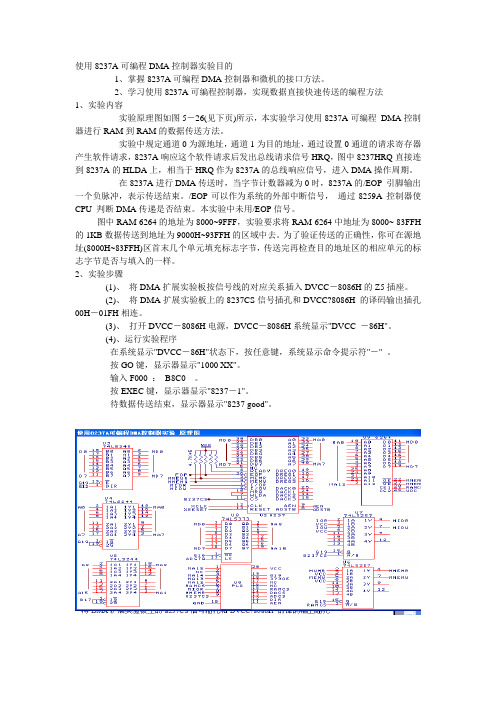

使用8237A可编程DMA控制器实验目的

使用8237A可编程DMA控制器实验目的1、掌握8237A可编程DMA控制器和微机的接口方法。

2、学习使用8237A可编程控制器,实现数据直接快速传送的编程方法1、实验内容实验原理图如图5-26(见下页)所示,本实验学习使用8237A可编程DMA控制器进行RAM到RAM的数据传送方法。

实验中规定通道0为源地址,通道1为目的地址,通过设置0通道的请求寄存器产生软件请求,8237A响应这个软件请求后发出总线请求信号HRQ,图中8237HRQ直接连到8237A的HLDA上,相当于HRQ作为8237A的总线响应信号,进入DMA操作周期。

在8237A进行DMA传送时,当字节计数器减为0时,8237A的/EOP 引脚输出一个负脉冲,表示传送结束。

/EOP可以作为系统的外部中断信号,通过8259A控制器使CPU 判断DMA传递是否结束。

本实验中未用/EOP信号。

图中RAM 6264的地址为8000~9FFF,实验要求将RAM 6264中地址为8000~ 83FFH 的1KB数据传送到地址为9000H~93FFH的区域中去。

为了验证传送的正确性,你可在源地址(8000H~83FFH)区首末几个单元填充标志字节,传送完再检查目的地址区的相应单元的标志字节是否与填入的一样。

2、实验步骤(1)、将DMA扩展实验板按信号线的对应关系插入DVCC-8086H的Z5插座。

(2)、将DMA扩展实验板上的8237CS信号插孔和DVCC?8086H 的译码输出插孔00H-01FH相连。

(3)、打开DVCC-8086H电源,DVCC-8086H系统显示"DVCC -86H"。

(4)、运行实验程序在系统显示"DVCC-86H"状态下,按任意键,系统显示命令提示符"-" 。

按GO键,显示器显示"1000 XX"。

输入F000 :B8C0 。

按EXEC键,显示器显示"8237-1"。

微机原理与接口技术期末试题ABC三卷及答案

《微机接口技术》课程试题A卷一、填空题(每空格1 分共 28 分)1.接口的基本功能是()和()。

2.数据输入/输出的三种方式是()、()和()。

3.在查询输入/输出方式下,外设必须至少有两个端口,一个是()端口,另一个是()端口。

4.总线传输方式通常有三种()、()和()。

5.在总线上完成一次数据传输一般要经历如下阶段()阶段、()阶段、()阶段、()阶段。

6.按总线在微机结构中所处的位置,总线可分为()总线、()总线、()总线、()总线。

7.8255A具有()工作方式:()选通、()选通和()。

8.串行通信方式分为()和()。

9.RS-232-C是()与()间的标准。

10.调制解调器是()和()的组合器件。

二、判断题(每小题3分共24)11.8086CPU 在读/写总线周期的 T3 状态结束对 READY 线采样,如果 READY 为低电平,则在 T3 与 T4 状态之间插入等待状态 TW。

()12.在 8253 的方式控制字中,有一项计数锁存操作,其作用是暂停计数器的计数。

()13.8250 的溢出错误指示 CPU 还未取走前一个数据,接收移位寄存器又将接收到的一个新数据送至输入缓冲器。

()14.在 8088 系统(最小组态)中,执行指令”MOV [2000H],AX”需 1 个总线周期。

()15.DMA 控制器 8237A 现行字节数寄存器的值减到 0 时,终止计数。

()16.8086/8088CPU 的复位后开始执行的第一条指令的地址为FFFFH。

()17.若各中断源的优先级是一样的,则可用自动循环优先级来实现。

()18.最小模式下 8086/8088 读总线操作时序和写总线操作时序中的 DT / R 信号波形基本相同。

()三、单项选择题:(每小题 3分,共 30 分)19.8086CPU工作在总线请求方式时,会让出()。

A.地址总线 B.数据总线C.地址和数据总线 D.地址、数据和控制总线20.8086CPU的I/O地址空间为()字节。

吉大14秋学期《微机原理及应用》在线作业一答案

吉大14秋学期《微机原理及应用》在线作业一

判断题多选题单选题

一、判断题(共5 道试题,共20 分。

)

1. 采用直接寻址输入/输出指令的最大端口地址为0FFH。

()

A. 错误

B. 正确

-----------------选择:B

2. 在8253的方式控制字中,有一项计数锁存操作,其作用是暂停计数器的计数。

()

A. 错误

B. 正确

-----------------选择:A

3. CPU响应可屏蔽中断时,无须从数据总线上读取中断类型码。

()

A. 错误

B. 正确

-----------------选择:A

4. DMA控制器8237A现行字节数寄存器的值减到0时,终止计数。

()

A. 错误

B. 正确

-----------------选择:A

5. 若各中断源的优先级是一样的,则可用自动循环优先级来实现。

()

A. 错误

B. 正确

-----------------选择:B

吉大14秋学期《微机原理及应用》在线作业一

判断题多选题单选题

二、多选题(共3 道试题,共12 分。

)

1. 在CPU与外设之间设计接口电路的目的主要有()。

A. 解决驱动能力问题

B. 控制数据传送速度

C. 完成数据形式转换

D. 负责CPU与外设的联络

-----------------选择:ABCD

2. 可以实现在数据段中保留10H个字节单元的指令有( )。

A. DW 08H DUP(?)。

【微机原理】11.3-8237A应用

MOV AL,43H

;通道3方式字

OUT DMA+0BH,AL ;写入通道3

;设置屏蔽字,清04个通道屏蔽位,Biblioteka 去除屏蔽MOV AL,00H

;屏蔽字

OUT DMA+0FH,AL ;输出到8237A

;对通道0~3的地址值和计数值进行测试,看读出的

; 值是否与写入的值(在BX中)相等

MOV DX,DMA

MOV DX,DMA ;通道0的地址寄存器端口

MOV AL,0FFH ;AL=FFH

C8:

MOV CX,0008H ;循环次数为8

WRITE:

MOV BH,AL

;放进BX以便比较

MOV BL,AL

;第1遍AL=FFH,第2遍00H

OUT DX,AL

;写入低8位

OUT DX,AL

;写入高8位

INC

DX

2. 编程举例 ➢ 某系统中用8237A设计了DMA传输电路,其基地址为00H。要

求用通道0从外设(如磁盘)输入1个1K字节数据块,传送到 内存中6000H开始区域中,每传送1字节,地址+1,采用数据 块连续传送方式,禁止自动预置,外设的DMA请求信号DREQ 和响应信号DACK均为高电平有效。则初始化8237A的程序如下:

DMA EQU 00H

;DMA基地址

;先送命令字,禁止8237A工作

MOV AL,04

;命令字:禁止8237A工作

OUT DMA+08H,AL ;输出命令字到8237A

OUT DMA+0DH,AL ;发总清命令

;第一遍,将通道0~3的基地址和当前地址寄存器

;均置为FFFFH,第二遍均置为0000H

电子科技大学14秋《微机原理及应用》在线作业1答案

14秋《微机原理及应用》在线作业1多选题判断题单选题一、多选题(共10 道试题,共50 分。

)1. 存储器寻址中所用的间址寄存器有()。

A. BXB. BPC. SID. DI-----------------选择:ABCD2. 在常用的I/O接口电路中,以下I/O接口芯片具有的特点是:()。

A. 计时器8253 有4个口地址,内部有三个独立的16位计数器,每个计数器具有6种工作方式,计数触发方式即可以内触发也可实现外触发。

B. 并行接口8255A有4个口地址,内部有3 个8位I/O口,每个口既可工作于简单输入/输出方式,又可工作于选通输入/输出方式,且A口还可工作于双向输入/输出方式。

C. DMA控制器8237 是4通道双地址DMAC,有16 个口地址,每一通道有三种传输方式,4个通道具有固定优先或循环优先方式。

D. 串行接口8250 是单通道异步通信控制器,有8 个口地址,内部具有发/收双-----------------选择:AD3. 下面各项中,不是同步总线协议的特点有()。

A. 不需要应答信号B. 各部件间的存取时间基本接近C. 总线周期长度可变D. 需要请求与应答握手信号-----------------选择:CD4. 下列存储器中,断电后内容仍然可以保存而不丢失的存储器包括()。

A. DRAMB. FLASHC. EPROMD. EEPROM-----------------选择:BCD5. 下面关于微处理器的叙述中,正确的是()。

A. 微处理器通常由单片集成电路制成。

B. 微处理器具有运算和控制功能,但无存储功能。

C. 8086是现在PC机中应用最广泛的微处理器。

D. Intel公司是研制和生产微处理器的知名公司。

-----------------选择:AD6. 关于断点与现场,描述正确的是()。

A. 断点通常指被中断的主程序的下一条待运行的指令的存放地址。

B. 断点是中断返回时的程序地址。

微机原理与接口技术课件:07 dma控制器8237a

三、8237A的外部引脚:

12. CLK:(clock )时钟信号。输入, 8237A:最高3MHZ. 8237A-5:最高5MHZ.

13. CS:(Chip Slected)片选信号。输 入,低电平有效。

14. RESET:复位信号。输入,高电平有 效。8237内部寄存器清0,屏蔽寄 存器置1,8237A处于状态,允许 CPU访问。

二、DMA控制器工作过程:

DMA控制器的工作过程分为四个阶段,分别是: 申请阶段 响应阶段 数据传送阶段 传送结束阶段。

微机原理与接口技术西北第二民族学院 电信系自动化教研室

1 DMA控制器概述

勤读力耕 立己达人

二、DMA控制器工作过程---申请阶段

1.外设向DMAC发出DMA请求信号DREQ(DMA Request); 2. DMAC向CPU发总线请求信号HRQ(Hold

2.块传输模式:指DMA控制器每次请求总线连续传送一个数 据块,待整个数据块全部传送完成后再释放总线控制权。 • 由DREQ启动连续地传送数据,直到字节数寄存器从0 减 到FFFFH终止计数,或由外部输入有效信号终结DMA传 送 • DREQ只需维持有效到DACK有效

微机原理与接口技术西北第二民族学院 电信系自动化教研室

1.6 M I/O MM

2 M I/O MM I/O I/O

2 M I/O

微机原理与接口技术西北第二民族学院 电信系自动化教研室

勤读力耕 立己达人

2 8237A的编程结构和外部引脚

一、8237A的主要特点:

(1)一个芯片中有4个独立的DMA通道。 (2)可以实现内存与外设,内存与内存的数据传输。 (3)每一个通道的DMA请求都可以被允许或禁止。 (4)每个通道的DMA请求有不同的优先级,即可以是

DMA控制器8237

DMA传送的基本原理图

DMA传送的三个阶段之准备阶段

(1)准备阶段。 • 这是一个程序工作阶段,包括对DMA控制器的初 始化、工作方式、基本参数的设置;对I/O设备及 其接口的初始化,如寄存器的清除,设备工作的 启动等。这时DMA控制器和I/O设备接口都被看作 是有多个I/O端口的设备,CPU对其相继执行若干 条OUT指令。所以图中DMA控制器、I/O设备接 口与系统总线之间都画有地址总线、数据总线和 控制总线。

• ③DMA控制器向地址总线发出将要传送数据的存储器的地 址信息,以备访问对应的存储单元。

DMA传送操作过程(续)

• ④DMA控制器向控制总线发出控制存储器和I/O设 备操作需要的读写信号,实现I/O设备和存储器之 间一个字节的传送。应该特别指出,传送数据字 节的途径是I/O设备→I/O设备接口→系统总线→存 储器,不经过DMA控制器。DMA控制器只起控制 作用。 • ⑤修改DMA控制器中提供存储器地址的地址寄存 器,指向存储器下一单元;记录传送的字节数, 为下一字节传送做好准备。

第 11 章

DMA控制器8237

教学重点

•A的工作原理 • DMA控制器8237A的初始化

教学要求

• 掌握DMA控制器传送数据的工作机理

• 了解DMA控制器的内部结构 • 了解8237的使用方法

第11章 DMA控制器8237

• 11.1 DMA传送的基本原理

DMA传送的三个阶段之结束阶段

(3)传送结束处理阶段。 • 在这一阶段通常是引入一段程序(可由中 断方法或基本I/O测试状态引入),对传送 的结果进行处理,或者同时完成下一次传 送的第一阶段的任务,为下次DMA传送作 准备。

11.2 DMA控制器8237A的工作原理

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DMA控制器8237Av外设与内存间的DMA工作时序v存储器间的DMA工作时序v PC/XT的DMA控制电路v DMA应答电路v8237A的应用举例v PC/XT机上的初始化和测试v磁盘DMA传输的初始化编程中山大学信息科学与技术学院陈任8237A 的工作原理(1)初始化工作模式起始地址传送字节数启动I/O 接口I/O 接口准备好数据并向8237A 发出DMA 请求DREQ 8237A 向CPU 发出总线持有请求信号HRQ CPU 在当前总线周期结束之后发出总线持有响应信号HLDA并让出总线8237A 接管总线并向接口发出DMA 响应DACK DACK 可作为端口选择信号8237A 读取I/O 端口并将读出的字节写入存储器(信号:IOR,存储器地址,MEMW )DMA 写操作传送一个字节地址加1,计数值减1如果计数值减至0发出EOP整个传送过程结束,否则,进入(10)123456789CPU 8237AI/O 接口DREQ HRQ HLDADACK 在块传送模式下转到(8)10在字节传送模式下,让出总线转到(3)在请求传送模式下,如果DREQ 无效则让出总线回到(3),否则,转到(8)8237A 的工作原理(2)8237A (一个通道)I/O 接口(1)DREQ 8088(2)HRQ(3)HLDA(4)DACK 初始化一个通道CPU 在DMA 之前需要进行初始化:设置DMA 的命令和模式寄存器,为DMA 通道设置地址和计数寄存器的值。

I/O 接口不需要地址译码电路,DACK 直接作为其中I/O 数据端口的片选信号(5)存储器地址IORMEMW存储器(5)数据(5)IOR (5)MEMW数据总线地址总线控制总线(7)EOP (当计数减为0时发出)地址计数(6)地址增/减1计数减1外设和内存间DMA传送时序(1)v8237A主要用于外设和内存之间进行高速的数据传输。

v8237A有两个主要的工作周期,即空闲周期(Idle Cycle)和有效周期(Active Cycle),每个周期由若干个状态构成。

v8237A设有7个独立的操作状态:SI、SO、S1、S2、S3、S4和SW,每个状态包含一个时钟周期。

›SI是非操作状态,8237A未接到DMA请求时便进入SI状态,此时8237A 可由CPU编程并预置操作方式。

›状态SO是DMA服务的第一个状态,此时8237A已向CPU的HOLD引脚发出一个DMA请求信号,但还没收到回答信号。

›S1、S2、S3、S4是DMA服务的工作状态。

›必要时,由慢速设备使用8237A的READY线,在S2和S4或S3和S4之间插入等待状态SW。

外设和内存间DMA传送时序(2) v空闲周期:系统复位后或无DMA请求时8237A处于空闲周期,工作于从态方式。

›在空闲周期的每一个时钟周期,8237A都对DREQ线进行采样,以确定是否有DMA请求,若无请求则一直处于SI状态。

›同时对CS#端进行采样,若CS#为低电平,而DREQ也为低(无效)则进入程序状态。

此时,CPU可以对8237A进行编程,把数据写入内部寄存器,或从内部寄存器中读出内容进行检查。

›IOR#和IOW#信号控制读/写操作,地址信号A3~A0用于选择内部寄存器的端口地址。

外设和内存间DMA传送时序(3) v有效周期:›当8237A在SI状态采样到外部存在有效的DMA请求信号DREQ(1)后,就向CPU发出DMA请求信号HRQ(2),并进入有效周期SO状态,等待CPU发出允许DMA操作的回答信号HLDA。

›此时,8237A仍可接受CPU的访问,SO是由主态转至从态的过渡阶段。

若在SO周期的上升沿采样到HLDA信号(高电平)(3),则表示CPU已经交出系统总线的控制权,下一个周期便进入DMA传送状态周期S1,DMA处于主态工作方式。

›一个完整的DMA传送周期由S1、S2、S3和S4共4个状态组成。

外设和内存间DMA传送时序(4) v有效周期:›在S1状态周期,地址允许信号AEN有效(4),把要访问的存储单元的高8位地址A15~A8送到数据总线DB7~DB0上(5),并发地址选通信号ADSTB,其下降沿(S2周期内)把高8位地址锁存到外部的地址锁存器中(6)。

低8位地址A7~A0由8237A直接送到地址总线上(7),在整个DMA 传送中都要保持住。

›S2状态周期用来修改存储单元的低16位地址。

此时,8237A从DB7~DB0线上输出这16位地址的高8位A15~A8,从A7~A0线上输出低8位。

另外8237A向外设输出DMA响应信号DACK (8),并使读或写信号有效,这样外设和内存间可在读写信号控制下交换数据。

›通常DREQ信号必须保持到DACK有效之后才能失效,失效允许有一个时间范围,图中用多条斜线表示(9)。

外设和内存间DMA传送时序(5) v有效周期:›若对命令寄存器的D3位编程,设定为正常时序后,工作时序中将会出现S3状态(10),用来延长读脉冲,即延长取数时间。

如用压缩时序工作,则没有S3状态,直接由S2状态进入S4状态。

›在S4状态,8237A对传输模式进行测试,如非块传输方式,也不是请求传输方式,则在测试后可立即回到S1或S2状态。

›在块传送方式下,S4后应接着传送下一个字节,在大部分情况下,地址高8位不变,每传送256个数据字节才变一次,仅低8位地址增1或减1。

›所以,在大部分情况下锁存高8位地址的S1状态就用不着,可直接由S4周期进入S2周期,从输出低8位地址起执行新的读写命令(11),一直到数据传送完毕,8237A又进入SI周期等待新的DMA请求。

外设和内存间DMA传送时序(6) v扩展写周期:›可以看出,8237A用正常时序工作时,一般要用到3个时钟周期S2、S3和S4。

在系统特性许可的范围内,为加快传送速度,可采用压缩时序,将传送时间压缩到两个时钟周期S2和S4内,压缩时序只能出现在连续传送数据的DMA操作中。

›无论是正常时序还是压缩时序,当高8位地址需要修正时,S1状态仍必须出现。

›如果外设的速度较慢,必须用正常时序工作。

若正常时序仍不能满足要求,以至于还是不能在指定时间内完成存取操作,那么就要在硬件上通过READY信号,使8237A插入等待状态SW。

›有些设备是利用8237A送出的IOW#或MEMW#信号的下降沿产生READY响应的,而这两个信号都是在传送过程的最后才送出,为使READY信号提前到来,将写脉冲拉宽,并使它们提前到来,就要用到扩展写信号方法(12)。

扩展写功能是通过对命令寄存器的D5位的设置来实现,当D5位置1时,写信号被扩展到2个时钟周期。

›在S4状态开始前,8237A要检测READY输入信号,若其为低则插入等待状态SW,直到READY变为高电平,才进入S4。

对于慢速的存储器和I/O设备,进行DMA传送时,可插入等待周期。

存储器到存储器传送时序(1)v当命令寄存器的D0位置1时,允许存储器与存储器之间的DMA传送。

传送操作必须用通道0和通道1进行,先用通道0从源内存单元读入数据字节,放入暂存器,再经通道1写入目的内存单元。

v传送过程由8个时钟周期组成。

前4个状态用S11、S12、S13、S14表示,这4个时钟周期用于从源内存单元读出数据。

后4个状态用S21、S22、S23和S24表示,把数据写入目的内存单元。

存储器到存储器传送时序(2)v在读出状态,通道0的高8位地址A15~A8通过DB7~DB0输出(1),由ADSTB信号锁存到外部锁存器中(2),低8位地址由A7~A0直接输出(3)。

v从S13状态起MEMR#有效(4),到S14时钟周期的上升沿把源内存单元读出的数据通过DB7~DB0送到8237A的暂存器(5) 。

v4个读周期完成后,进入4个写周期,先通过DB7~DB0引线输出通道1的高8位地址A15~A8(6),并由ADSTB锁存到外部锁存器中(7),低8位地址由A7~A0输出(8)。

v在以后的周期,使MEMW#有效(9),把暂存器中的数据经DB0~DB7输出到目的内存单元(10)。

v数据传送完成后发EOP#信号,结束DMA操作(11)。

IBM PC/XT 的DMA 控制电路8237A驱动器页面寄存器锁存器A 0~A 7A 16~A 19A 8~A 15A 0~A 7AEN ADSTB DCLK DMA CS RDY TO DMARESET HOLDA XIOR XIOW XMEMR XMEMW DRQ 0~3D 0~7WRT DMAPG DMA AENWA WBRARBWRITE READD 3-01G 2GOE GTCHRQ DMA DACK 0BRD DACK 1DACK 2DACK 3EOP HRQ DACK 0DACK 1DACK 2DACK 3CLK CS READY RESET HLDA IOR IOW MEMR MEMW DREQ 0~3DB 0~7A 4~A 7A 0~A 3IBM PC/XT的DMA控制电路v PC/XT机中的DMA控制电路由8237A-5 DMA控制器、地址驱动器74LS244,地址锁存器74LS373和页面寄存器74LS670等器件组成。

v构成四个DMA通道,提供数据宽度为8位的DMA传输:›通道0 –动态存储器刷新通道0设置:实地址为0,计数值为64K, 工作方式为读操作,自动预置,地址加1,单字节传送。

›通道1 –保留›通道2 –软盘›通道3 –硬盘v固定优先级,通道0优先级最高,通道3最低。

v当进入DMA服务时,直接从8237A-5的A7~A4和A3~A0端输出低8位地址,在整个DMA传输周期中,这些地址信号是稳定的,被送到地址驱动器74LS244的输入端。

v仅仅在S1、S2状态,高8位地址A15~A8才通过DB0~DB7输出,因此要用ADSTB选通信号将高8位地址锁存在地址锁存器74LS373中。

v8237A-5只能提供16位地址,因此设置了一个页面寄存器74LS670来产生存储器的高4位地址A19~A16,通过对页面寄存器的编程,可以实现在1M内存范围内寻址,但是在DMA传输过程中,页面寄存器的值是固定的,即总是指向内IBM PC/XT的DMA控制电路v页面寄存器共有四组4位地址,可以用于四个通道。

通道1, 通道2和通道3分别采用端口83H, 81H和82H,通道0未用。

页面寄存器的片选信号WRT DMAPG#采用地址80~9FH译码。

v页面寄存器内部有4个可以由程序读写的寄存器,每个寄存器对应一个DMA 通道,长度均为4位。

v对于每一个DMA通道来说,页面寄存器的4位输入接到系统数据总线的D3~D0,4位输出接系统地址总线的A19~A16。

v当控制信号WRITE#为低电平时,可从数据总线的低4位D3~D0将最高4位地址信息写入该通道的页面寄存器。