基于FPGA的交通灯(verilog)

《FPGA设计与应用》交通灯实验一

《FPGA设计与应用》交通灯实验

一、实验目的和要求

实验目的:

1. 综合运用 Verilog HDL 语言进行时序设计。

实验要求:

1. 两个方向各种灯亮的时间能够进行设置和修改

二、实验内容和原理

1. 编写时间控制程序,利用交通灯实验子板,实现东西,南北向的交通灯计数并亮灯的程序;

2.子板实现所有显示方面的功能,包括十进制倒数计数和红绿黄三色灯的轮流点亮。

三、主要仪器设备

电脑、VIVADO软件

四、操作方法与实验步骤

1.为了在八段数码管上正确显示十进制数据,设计一个函数,程序即上述实验五中的数码管封装模块。

2、将实验板上电,下载程序到 FPGA 芯片中。

3、观察实验结果。

五、实验数据记录和处理

综合:

程序:

六、实验结果与分析

实验仿真结果:

实物操作:

七、讨论和心得

通过这次实验,我加深了用Verilog语言来进行时序设计方法的理解,能够编写简单的时间控制程序,让我verilog语法的运用更加熟练,在实验中还用到了之前学到的模块调用,加深了我对之前知识的理解。

通过本次实验,我不仅学到了关于Verilog的知识,同时也让我感觉到了思考的重要性。

基于FPGA实现的交通灯控制器详解

基于FPGA实现的交通灯控制器详解交通灯控制器是城市交通管理中的重要设备,用来控制红绿灯的改变。

传统的交通灯控制器多采用微控制器或单片机实现,但是这些方式在处理大规模的交通路口时会受到性能和并发处理能力的限制。

为了克服这些问题,近年来,基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)的交通灯控制器逐渐得到应用。

FPGA是一种可编程逻辑器件,能够根据用户需求进行现场编程,具有高度灵活性和可重构性。

基于FPGA的交通灯控制器可以通过并行处理和精确时间管理来提高性能。

FPGA可以为每个交通灯信号灯分配独立的处理器核,同时可以对不同的交通灯进行并发处理。

这种并行处理的方式大大提高了系统的响应速度和处理能力,可以更好地适应高负载的交通场景。

此外,FPGA还可以提供更精确的时间管理。

交通灯的信号改变需要精确地控制时间,以确保交通流畅和交通安全。

传统的微控制器或单片机无法提供足够的精确性和实时性,而FPGA可以通过硬件电路和时钟管理单元来实现高精度的时间控制。

这种精确的时间管理能够对交通流量进行准确的判断和调度,提高交通效率。

此外,基于FPGA的交通灯控制器还具有可扩展性和灵活性。

FPGA的可编程特性使得交通灯控制器可以轻松地进行功能扩展和升级,满足不同场景和需求的要求。

而且,FPGA还可以进行实时调度和优化,可以根据实际交通情况进行动态调整,使交通灯控制系统更加智能和高效。

总之,基于FPGA的交通灯控制器具有高性能、精确的时间管理、可扩展性和灵活性等优点。

它可以提供更好的交通管理和安全保障,适用于大规模的交通路口和复杂的交通场景。

随着FPGA技术的不断发展和成熟,基于FPGA的交通灯控制器将会得到更广泛的应用。

基于FPGA的交通灯设计

基于FPGA的交通灯设计交通灯是城市交通系统中非常重要的组成部分,它们的设计和控制对交通流的安全和效率有重大影响。

随着科技的进步,基于FPGA(现场可编程门阵列)的交通灯设计越来越受到关注和应用。

本文将介绍基于FPGA的交通灯设计的原理和优势,并探讨其在现实生活中的应用。

首先,我们来了解FPGA技术。

FPGA是一种硬件设备,可以通过编程对其内部逻辑电路进行配置和重组。

与传统的固定功能芯片相比,FPGA具有灵活性和可重配置性。

它可以根据不同的需求和应用进行程序和逻辑的重新编程,从而实现不同的功能。

这使FPGA成为交通灯设计的理想选择。

基于FPGA的交通灯设计的核心是通过编程逻辑实现灯色的切换和时序控制。

传统的交通灯通常由三个灯色(红、黄、绿)组成,可以根据交通流的需求进行切换。

基于FPGA的交通灯设计可以通过编程逻辑控制灯色和时序,从而实现更加精确和高效的交通流控制。

基于FPGA的交通灯设计具有以下优势。

首先,由于FPGA的可重配置性,交通灯的设计可以根据实际需求进行调整和优化。

无论是交通流量大还是小,交通灯的时序和灯色可以进行灵活调整,以提高交通流的效率和安全性。

其次,FPGA的高性能特性使得交通灯能够实时响应交通流变化。

无论是高峰时段还是低峰时段,交通灯都能够根据实际情况进行灯色切换,确保交通流的顺畅和安全。

最后,FPGA的可靠性和稳定性可以保证交通灯的长期运行。

传统的交通灯可能会因为灯泡烧坏或电路故障而出现故障,而基于FPGA的交通灯设计可以提高系统的可靠性和稳定性,减少故障的发生。

基于FPGA的交通灯设计在现实生活中有广泛的应用。

首先,它可以用于城市道路的交通信号控制。

根据交通流量和道路拥堵情况,交通灯的时序和灯色可以进行调整,以最大程度地减少交通堵塞和事故发生的可能性。

其次,基于FPGA的交通灯设计可以应用于隧道和地下通道的交通信号控制。

由于隧道和地下通道的特殊环境,传统的交通灯在这些场景中难以进行有效的控制。

基于FPGA的智能交通灯控制器

数字逻辑课程设计报告题目:基于FPGA的智能交通灯控制器课程名称:数字逻辑课程设计专业班级:学号:姓名:报告日期:2013-9-12计算机科学与技术学院1. 实验目的通过V erilog的编程,深入了解并掌握可编程芯片的使用技术,完成规定的设计任务,加强对《数字逻辑》课程所学知识的理解,培养学生创造性思维能力和独立解决实际问题的能力。

2. 实验内容用V erilog代码实现智能交通灯信号控制器设计,具体内容及要求如下:(1)在主干道与次干道公路十字交叉路口,为确保人员、车辆安全、迅速地通过,在交叉路口的每个入口处设置了红、绿、黄三色信号灯。

红灯禁止通行;绿灯允许通行;黄灯亮则给行驶中的车辆有时间行驶到禁行线之外。

(2)主干道和次干道公路十字交叉路口都安装了车辆检测传感器(C),要求如下:(A)在每日的早、晚高峰时段,双边“C=1”则主干道通行时间是次干道通行时间的2倍;(B)全天主、次干道有车一方有优先通行权;(3)主干道公路路口安装有人员通过请求按钮(PQ),一旦有请求信息,控制器应给与放行。

(4)Online控制信号由交通控制中心发出,(Online=1)一旦它有效,则主干道放行,十字交叉路口控制器“失效”,Online=0十字交叉路口控制器恢复控制权。

(6)在每次由绿灯亮变成红灯亮的转换过程中间,要亮5s时间的黄灯作为过渡。

(7)用“开关”代替传感器作为人员通过请求和车辆是否到来的信号。

用红、绿、黄三种颜色的发光二极管作交通灯。

(8)要求显示时间,倒计时。

3. 实验环境PC 个人计算机、ISE14.2 软件、Adept软件、开发板Basys2、USB下载线4. 实验设计方案4.1 输入输出与引脚分配说明4.1.1输入信号:PQ,人员请求信号——接板子“E2”开关ONLINE, 控制中心接管信号——接“N3”SET, 控制器开关——接“P11”RST, 复位开关——接“L3”RUSH, 高峰判断开关——接“F3”CM, 主道车辆传感器——接“G3”CC, 支道车辆传感器——接“B4”CLK, 系统时钟——接“B8”4.1.2输出信号:[2:0] ML, ML0~2 主道绿、黄、红灯——分别接“G1、P4、N4”[2:0] CL , CL0~1 支道绿、黄、红灯——分别接“P7、M11、M5”[6:0] a_to_g, 七段数码管接口——a_to_g0~6分别接“M12、L13、P12、N11、N14、H12、L14”[3:0] an, 四选一控制接口——an0~4分别接“F12、J12、M13、K14”4.2 模块图4.2.1 模块层级图4.2.2 模块1.时钟生成模块4.2.3 模块2. 控制模块【1】输入信号input wire clk1s, 近似1s的时钟信号input wire PQ, 人员请求信号input wire ONLINE, 控制中心请求信号input wire SET, 控制器开关信号input wire RST, 复位信号input wire RUSH, 高峰信号input wire CM, 主道车辆检测信号input wire CC, 支道车辆检测信号【2】输出信号output reg [2:0] ML, 主道信号灯接口output reg [2:0] CL, 支道信号灯接口output [7:0] ACOUNT,存放主道两个时间数字的8421码output [7:0] BCOUNT,存放支道两个时间数字的8421码(ACOUNT、BCOUNT整合到顶层文件b[15:0]中,方便调用七段显示模块)【3】模块内部流程图4.2.4 模块3. 七段显示模块【1】显示原理使用同步扫描电路,对4位数码管的控制端口进行扫描,每一个时刻只有一个数码管亮,只要设置足够快的频率扫描,由于眼睛的视觉停留效应,就会使得显示结果达到4位同时亮的效果。

verilog课程设计—交通灯

CPLD课程设计基于FPGA 的交通灯控制器的设计姓名:学号:专业:基于FPGA 的交通灯控制器的设计摘要:现代城市在日常运行控制中,越来越多的使用红绿灯对交通进行指挥和管理。

而一套完整的交通灯控制系统通常要实现自动控制和手动控制去实现其红绿灯的转换。

基于FPGA 设计的交通灯控制系统电路简单、可靠性好。

本设计利用Verilog HDL 语言、采用层次化混合输入方式,可控制4个路口的红、黄、绿、左转四盏信号灯,让其按特定的规律进行变化。

在QUARTUSⅡ下对系统进行了综合与仿真。

仿真结果说明系统可实现十字路口红绿灯及左转弯控制和倒计时显示,并能够自动控制交通灯转变。

关键词:FPGA ;交通灯自动控制;Verilog HDL;Quartus Ⅱ1.交通信号控制器设计要求与思路设计要求在交通灯系统中〔图1〕,路口1、2、3、4均需要红、黄、绿、左转四盏灯(用RYGL分别表示) ,并且每个路口都需要一个倒数的计时器,假设绿灯每次维持的时间是40 s ,黄灯为5 s ,左转灯10s,红灯60s,黄灯亮时以一定的频率闪动。

交通灯系统大多是自动控制来指挥交通的,但有时需要由交警手动控制红绿灯,所以要求设计的该交通信号系统需要具有该功能。

图1 交通灯系统示意图设计思路为了便于讨论,我们只讨论路口1〔用A表示〕和路口4〔用B表示〕。

此交通灯控制系统一共设计有5种工作模式。

分别为:方式1 :A 向绿灯长亮,B 向红灯亮。

方式2 :A 向左转灯长亮,B 向红灯亮。

方式3 :B 向绿灯长亮,A 向红灯亮。

方式4 :B 向左转灯长亮,A 向红灯亮。

方式5 :自开工作方式,两个方向的灯按照显示的顺序,交替循环显示。

系统设有总复位开关,可在任意时间内对系统进行复位。

利用M2M1M0对系统工作的状态进行控制〔见表1〕。

A路口和B路口均需要红黄绿加左转四盏灯。

所以输出显示可以用8个LED灯代替。

又因为最大显示时间为60s,故用两个数码管即可承当显示一个倒数计时器的任务。

verilog交通灯设计(FPGA)

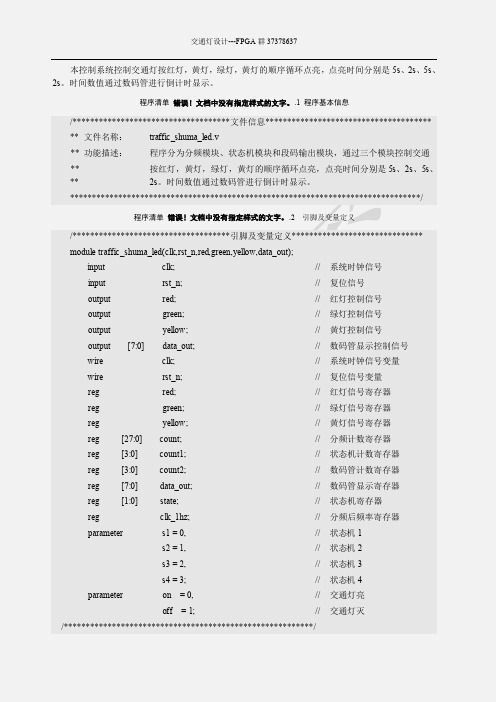

本控制系统控制交通灯按红灯,黄灯,绿灯,黄灯的顺序循环点亮,点亮时间分别是5s、2s、5s、2s。

时间数值通过数码管进行倒计时显示。

程序清单错误!文档中没有指定样式的文字。

.1 程序基本信息/************************************文件信息************************************** ** 文件名称:traffic_shuma_led.v** 功能描述:程序分为分频模块、状态机模块和段码输出模块,通过三个模块控制交通** 按红灯,黄灯,绿灯,黄灯的顺序循环点亮,点亮时间分别是5s、2s、5s、** 2s。

时间数值通过数码管进行倒计时显示。

********************************************************************************/程序清单错误!文档中没有指定样式的文字。

.2 引脚及变量定义/************************************引脚及变量定义****************************** module traffic_shuma_led(clk,rst_n,red,green,yellow,data_out);input clk; // 系统时钟信号input rst_n; // 复位信号output red; // 红灯控制信号output green; // 绿灯控制信号output yellow; // 黄灯控制信号output [7:0] data_out; // 数码管显示控制信号wire clk; // 系统时钟信号变量wire rst_n; // 复位信号变量reg red; // 红灯信号寄存器reg green; // 绿灯信号寄存器reg yellow; // 黄灯信号寄存器reg [27:0] count; // 分频计数寄存器reg [3:0] count1; // 状态机计数寄存器reg [3:0] count2; // 数码管计数寄存器reg [7:0] data_out; // 数码管显示寄存器reg [1:0] state; // 状态机寄存器reg clk_1hz; // 分频后频率寄存器parameter s1 = 0, // 状态机1s2 = 1, // 状态机2s3 = 2, // 状态机3s4 = 3; // 状态机4parameter on = 0, // 交通灯亮off = 1; // 交通灯灭/*********************************************************/// 模块名称:分频模块// 模块功能:将系统时钟信号clk分频得到1HZ的频率信号clk_1hz//****************************************************************************** always@(posedge clk or negedge rst_n)beginif(!rst_n) // 判断复位信号是否有效begincount <= 0; // 计数器清0endelsebeginif(count==28'd2*******) // 判断计数器是否计满beginclk_1hz <= 1; // 输出1Hz信号count <= 0; // 计数器清0endelsebeginclk_1hz <= 0; // 输出1Hz信号的低电平count <= count + 28'd1; // 计数器加1endendend//******************************************************************************* // 模块名称:状态机模块// 模块功能:通过时钟信号和复位信号对交通灯的状态进行控制//****************************************************************************** always@(posedge clk_1hz or negedge rst_n)beginif(!rst_n) // 判断复位信号是否有效beginstate <= s1; // 初始状态为S1count1 <= 0; // 计数器清0count2 <= 4'b0101; // 计数器置数endelsebegincase(state)s1: // 状态1begingreen <= off; // 绿灯不亮yellow <= off; // 黄灯不亮red <= on; // 红灯亮count1 <= count1 + 4'b1; // 计数器加1if (count1 == 4'b0101) // 计数器是否等于5begincount1 <= 0; // 计数器清0state <= s2; // 状态转移count2 <= 4'b0010; // 计数器置2endelsecount2 <= count2-1; // 计数器减1ends2: // 状态2beginred <= off; // 红灯不亮green <= off; // 绿灯不亮yellow <= on; // 黄灯不亮count1 <= count1 + 4'd1; // 计数器加1if(count1 == 4'b0010) // 判断计算器是否等于2begincount1 <= 0; // 计数器清0state <= s3; // 状态转移count2 <= 4'b0101; // 计数器置数endelsecount2 <= count2-1; // 计数器减1 ends3: // 状态3beginred <= off; // 红灯不亮green <= on; // 绿灯亮yellow <= off; // 黄灯不亮count1 <= count1 + 28'd1; // 计数器加1if(count1 == 4'b0101) // 计数器是否等于5begincount1 <= 0; // 计数器清0state <= s4; // 状态转移count2 <= 4'b0010; // 计数器置数endelsecount2 <= count2-1; // 计数器减1ends4: // 状态4beginred <= off; // 红灯不亮green <= off; // 绿灯不亮yellow <= on; // 黄灯亮count1 <= count1 + 4'd1; // 计数器加1if(count1 == 4'b0010) // 判断计数器是否等于2begincount1 <= 0; // 计数器清0state <= s1; // 状态转移count2 <= 4'b0101; // 计数器置数endelsecount2 <= count2-1; // 计数器减1endendcaseendend// 模块名称:数码显示模块// 模块功能:根据数码管计数器信号发送相应的断码信号是数码管显示倒计时//******************************************************************************* always@(*)case(count2)4'b0000:data_out = 8'b00111111; // 显示04'b0001:data_out = 8'b00000110; // 显示14'b0010:data_out = 8'b01011011; // 显示24'b0011: data_out = 8'b01001111; // 显示34'b0100: data_out = 8'b01100110; // 显示4 4'b0101:data_out = 8'b01101101; // 显示5 4'b0110: data_out = 8'b01111101; // 显示6 4'b0111: data_out = 8'b00000111; // 显示7 default: data_out = 8'b01111111; // 显示0 endcaseendmodule。

基于FPGA的交通灯的设计

课程设计一、设计任务要求基于FPGA的交通灯控制器设计1、总体要求:实现十字路口的交通灯有序显示2、具体要求:按照开发板上的两组红、黄、绿做为南北双向指示灯红灯亮60秒,绿灯亮55秒,黄灯亮5秒要求采用状态机实现状态切换3、附加要求:采用两组两位数码管实现时间倒计时显示二、设计思路1、总体设计方案由设计任务要求可知输入部分有:CLK时钟频率输入,可由实验板上直接提供,本设计选用1kHZ时钟频率。

输出部分有:1)东西方向和南北方向各使用3个LED显示,红黄绿各代表红黄绿灯。

2)东西方向和南北方向计时均为2位数,共需要4个LED七段数码管显示。

由于为共阴极控制,输出三个SEL0,SEL1,SEL2信号控制选择数码管显示,A,B,C,D,E,F,G信号为输出显示的内容。

3)R1,G1,Y1;R2,G2,Y2信号分别为东西南北红绿灯的输出控制信号。

总体设计软件原理图如下所示设计方案原理图:图1A对应13脚; B对应30脚;C对应15脚; D对应31脚;E对应33脚; F对应32脚;G对应35脚; R1对应4脚;R2对应5脚;Y1对应3脚;Y2对应10脚;G2对应8脚;SEL0对应14脚; SEL1对应11脚;SEL2对应12脚.CLK对应24脚;交通灯系统结构图如下所示:红黄绿红黄绿图2状态切换的状态图如下图:图2、模块设计及结果在VHDL设计中,采用自顶向下的设计思路。

顶层模块中,根据硬件设计,设置如下端口:外部时钟信号:Clk东西方向状态灯控制信号:R1,G1,Y1;南北方向状态灯控制信号:R2,G2,Y2;(1)分频模块:由于外部时钟信号clk的频率为1KHz,而实际需要的内部计时时钟频率为1Hz,需要一个分频电路。

输入端口:clk外部时钟信号输出端口:clk_out分频后信号源程序代码如下:数码管显示信号:A,B,C,D,E,F,G;数码管共阴极控制:SEL0,SEL1,SEL2;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity Frequency1 isport(clk:in std_logic; --外部时钟信号clk_out:out std_logic --分频后信号);end Frequency1;architecture Frequency1_arc of Frequency1 isbeginprocess(clk)variable temp:integer range 0 to 999;beginif(clk'event and clk='1')thenif(temp=999)then --分频计数temp:=0;clk_out<='0';elsetemp:=temp+1;clk_out<='1';end if;end if;end process;end;图4(2)状态选择模块:由于共需要显示4个数字,需要循环点亮7位数码管,该模块通过输入的时钟信号,循环输出4个选择信号。

基于FPGA的交通灯控制电路设计

基于FPGA的交通灯控制电路设计本文介绍了一种基于FPGA的交通灯控制电路设计。

交通灯控制是城市交通管理的一个重要部分,它有助于维护交通秩序,减少交通事故,提高交通效率。

在本电路设计中,我们使用FPGA作为主控制器,并通过数码管、按钮和LED模块与外部交互。

同时,我们还采用了状态机设计方法,以实现灵活的控制逻辑和连续的动态过渡。

首先介绍了本电路设计的硬件设计。

在本设计中,我们使用了FPGA作为主控制器,数码管用于显示当前状态,按钮用于进行手动控制,LED模块用于显示当前灯颜色。

在硬件设计中,我们通过适当的寄存器和时钟模块,实现了稳定的时序控制和同步操作。

接着,我们介绍了本电路设计的软件设计。

在软件设计中,我们采用了状态机设计方法,将交通控制逻辑分为多个状态,通过状态间的转移完成交通灯的切换控制。

具体地,我们将交通灯控制状态划分为三种:绿灯、黄灯和红灯。

在每种状态下,我们通过计数器和状态转移条件来实现精确的时间控制和灯颜色的自动切换。

同时,为了提高控制的灵活性,我们设计了手动控制模式,让用户可以通过按钮手动切换交通灯状态。

最后,我们介绍了本电路设计的实现结果。

在实现过程中,我们使用了Quartus II软件进行综合、布局和验证,并将设计的电路下载到FPGA开发板上进行实验。

实验结果表明,本交通灯控制电路设计实现了稳定、灵活和精确的交通控制,能够满足不同的交通道路需求。

综上所述,本文介绍了一种基于FPGA的交通灯控制电路设计,通过硬件和软件设计,实现了稳定、灵活和精确的交通控制。

该设计可以为城市交通管理提供帮助,为交通事故和交通拥堵的缓解做出贡献。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于同步FSM交通信号控制器

试验目的

1、进一步熟悉FSM原理;

2、交通信号控制逻辑的抽象建模方法;

3、掌握同步有限状态机的置位与复位方法;

3、掌握编写可综合的FSM一般指导原则;

试验原理

Verilog HDL和VHDL亍为描述用于综合还只有十年的历史,可综合风格的VerilogHDL和VHD啲语法只是它们各自语言的一个子集;HDL的可综合性研究近年来非常活跃,可综合子集的国际标准目前尚未最后形成,因此,各厂商的综合器所支持的HDL子集也略有不同;对于有关可综合的VerilogHDL的内容我们只着重于介绍RTL算法级和门级结构的描述;把一个时序逻辑抽象成一个同步有限状态机是设计可综合VerilogHDL 模块的关键。

有限状态机是设计各种时序逻辑电路的关键。

具体的有限状态机的原理可以参看试验七有关原理的介绍。

下面介绍一般的可综合有限状态机的编写原则

每个always 块只能有一个事件控制@(event_expression) ,而且要紧跟在

always 关键字后面;

always 可以表示时序逻辑或者组合逻辑;也可以用always 块既表示电平敏感的锁存器又同时表示组合逻辑;

带有posedge或negedge关键字的事件表达式表示边沿触发的时序逻辑,没有posedge或negedge关键字的表示组合逻辑或者电平敏感的锁存器,或者两者都表示;

每个表示时序的always 块只能由一个时钟跳变沿触发,置位和复位最好也由该始终跳变沿触发;

每个在always 块中赋值的信号必须定义为reg 类型或者整型;

Always 块中应该避免组合反馈回路;

实验步骤和实验内容

1、本试验交通信号控制灯的逻辑关系该交通信号灯控制器用于控制一条主干道与一

条乡村公路的交叉口的交通

( 如图8-1 所示) ,它必须具有下面的功能;由于主干道上来往的车辆较多,因此控制主干道的交通信号灯具有最高优先级,在默认情况下,主干道的绿灯点亮;乡村公路间断性地有车经过,有车来时乡村公路的交通灯必须变为绿灯,只需维持一段足够的时间,以便让车通过。

只要乡村公路上不再有车辆,那么乡村公路上的绿灯马上变为黄灯,然后变为红灯;同时,主干道上的绿灯重新点亮;一传感器用于监视乡村公路上是否有车等待,它向控制器输入信号X;如果X=1,则

表示有车等待,否则X=o;当从S1状态转换到S2状态,从S2状态转换到S3状态,从S3状态转换到S4状态,从S4状态转换到S20状态时,具有一定的延时;

2、试验内容

1 )从以上实际交通信号控制问题抽象逻辑关系;

2)画出状态转换图;

2)设计Verilog 代码;

TO START: 实验代码//基于同步FSM 交通信号灯控制器

'defi ne TRUE 1'b1

'defi ne FALSE 1'b0

//延迟

'define Y2RDELAY 3

'define R2GDELAY 2

module sig_control(hwy,cntry,X,clock,clear); output[1:0]hwy,cntry;

reg[1:0]hwy,cntry;

input X;

input clock,clear;

parameter RED=2'd0,

YELLOW=2'd1,

GREEN=2'd2;

parameter S0 =3'd0,

51 =3'd1,

52 =3'd2,

53 =3'd3,

54 =3'd4;

reg[2:0] state;

reg[2:0] next_state;

always@(posedge clock) if(clear)

state<=S0;

else

state<=next_state;

always@(state)

begin

hwy =GREEN;

cntry =RED;

case (state)

S0: ;

S1:hwy =YELLOW;

S2:hwy =RED;

S3: begin

hwy = RED;

cntry = GREEN;

end

S4: begin

hwy =RED;

cntry =~YELLOW;

end

endcase

end

always@(state or X)

begin

case(state)

S0: if (X)

next_state =S1;

else

next_state = S0;

S1:begin

repeat('Y2RDELAY)@(posedge clock); next_state = S2;

end

S2:begin

repeat('R2GDELAY)@(posedge clock); next_state = S3;

end

S3: if (X)

next_state =S3;

else

next_state = S4;

S4:begin

repeat('Y2RDELAY)@(posedge clock); next_state = S0;

end

default:next_state =S0;

endcase

end endmodule

得结果

虽然有警告,但是综合还是过了,成功了!

fcg

3 ►C WIZL I C B^igii

卜厂=

y 甲"卜血环讳讥腐血订

P Fitter (Jl&ce

/ 甲亠ftsswlil就yfcy iit 旨Lurf

# g—口帕力r Timaf bdywi t

F-lk lllk fri tfr

交通信号控制信号的状态

图如下:

4 总I A U-L L ysi= 1

Eynlkes]s B 旨」Jl tiar

+■音」AsimUsr

Tim £t:

i-ns

Qiurtu 口y"fTsi

皿WiSlOEL hl !

Tojrlevel Jnt-itj-

rwily

Dwi«

TninjV:血血ht 啓

r^qaiTETicnts

iHil fzBit

xncEEEO. nijJLijpi.Ler w

陆

以下是所得的彷真图: 放大如下 || k%- «:-l^ Ikiu.i. ry. Bio* It ^BUTI 3^ •n* • 'Ji i ・3 C4U. 'i £dlana ! <11 ■・2・>

160.0 ns 320.0 rs I 4M.0 ns I 640.0 ns 8C0 0 ns Nine

963 C ns 1.0 u 1]81JOJ irckt?-- < I d d LrL —

TL □

□。