实验一:MIPS指令集实验

MIPS单周期CPU实验报告材料

《计算机组成原理实验》实验报告(实验二)学院名称:专业(班级):学生姓名:学号:时间:2017 年11 月25 日成绩 :实验二:单周期CPU设计与实现一.实验目的(1) 掌握单周期CPU数据通路图的构成、原理及其设计方法;(2) 掌握单周期CPU的实现方法,代码实现方法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的方法;(5) 掌握单周期CPU的实现方法。

二.实验内容设计一个单周期的MIPSCPU,使其能实现下列指令:==> 算术运算指令说明:以助记符表示,是汇编指令;以代码表示,是机器指令功能:rd←rs + rt。

reserved为预留部分,即未用,一般填“0”。

符号扩展再参加“加”运算。

(3)sub rd , rs , rt功能:rd←rs - rt==> 逻辑运算指令(4)ori rt , rs ,immediate功能:rt←rs | (zero-extend)immediate;immediate做“0”扩展再参加“或”运算。

(5)and rd , rs , rt功能:rd←rs & rt;逻辑与运算。

功能:rd←rs | rt;逻辑或运算。

==>移位指令==>比较指令功能:if (rs<rt) rd =1 else rd=0, 具体请看表2 ALU运算功能表,带符号==> 存储器读/写指令(9)sw rt ,immediate(rs) 写存储器功能:memory[rs+ (sign-extend)immediate]←rt;immediate符号扩展再相加。

即将rt寄存器的内容保存到rs寄存器内容和立即数符号扩展后的数相加作为地址的内存单元中。

(10) lw rt , immediate(rs) 读存储器功能:rt ← memory[rs + (sign-extend)immediate];immediate符号扩展再相加。

计算机设计与实践——MIPS基本指令

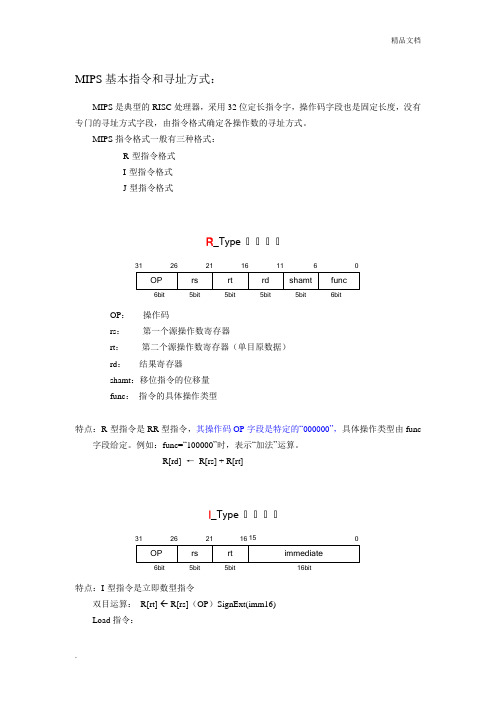

MIPS 基本指令和寻址方式:MIPS 是典型的RISC 处理器,采用32位定长指令字,操作码字段也是固定长度,没有专门的寻址方式字段,由指令格式确定各操作数的寻址方式。

MIPS 指令格式一般有三种格式: R-型指令格式 I-型指令格式 J-型指令格式R _Type 指指指指262116116316bit6bit5bit5bit5bit5bitOP : 操作码rs : 第一个源操作数寄存器rt : 第二个源操作数寄存器(单目原数据) rd : 结果寄存器 shamt :移位指令的位移量 func : 指令的具体操作类型特点:R-型指令是RR 型指令,其操作码OP 字段是特定的“000000”,具体操作类型由func字段给定。

例如:func=“100000”时,表示“加法”运算。

R[rd] ← R[rs] + R[rt]I _Type 指指指指2621163115特点:I-型指令是立即数型指令双目运算: R[rt] R[rs](OP )SignExt(imm16) Load 指令:Addr ← R[rs] + SignExt(imm16) 计算数据地址 (立即数要进行符号扩展) R[rt] ← M[Addr] 从存储器中取出数据,装入到寄存器中Store 指令:Addr ← R[rs] + SignExt(imm16) M[Addr] ← R[rt]J _Type 指令格式26316bit26bit25特点:J-型指令主要是无条件跳转指令,将当前PC 的高4位拼上26位立即数,后补两个“0”,作为跳转目标地址。

j L //goto L 指指指指指指指指指jal L //$ra 指PC+4;goto L 指指指指指指指指指R 型指令:定点运算: add / addu , sub / subu , sra , mult/multu , div/divu 逻辑运算: and / or / nor , sll / srl 比较分支: beq / bne / slt / sltu 跳转指令: jrI 型指令:定点运算: addi / addiu 逻辑运算: andi / ori 比较分支: slti / sltiu数据传送: lw / sw / lhu / sh / lbu / sb / luiJ 型指令: j / jal设计模块划分,教学安排1、MIPS格式指令系统设计2、指令存储器设计3、寄存器堆设计4、ALU设计——基本算术、逻辑单元的设计32位超前进位加法器的设计32位桶式移位寄存器的设计5、取指令部件的设计6、立即数处理单元设计7、单周期处理器设计——R型指令的数据通路设计I型指令的数据通路设计Load/Store指令的数据通路设计分支指令/转移指令的数据通路设计综合12条指令的完整数据通路设计8、ALU控制单元设计9、主控制单元的设计10、单周期处理器总体验证11、异常和中断处理及其电路实现12、带有异常和中断处理功能的处理器的设计设计示例1:指令存储器设计1、 指令存储器模块定义:指令存储器用于存放CPU 运算的程序指令和数据等,采用单端口存储器设计,设计最大为64个存储单元,每个存储单元数据宽度为32bit 。

华中科技大学HUST类MIPS单周期微处理器设计实验报告

类MIPS单周期微处理器设计实验报告专业:班级:学号:姓名:一、微处理器各模块设计各模块的框图结构如上图所示。

由图可知,该处理器包含指令存储器、数据存储器、寄存器组、ALU单元、符号数扩张、控制器、ALU控制译码以及多路复用器等。

图中还忽略了一个单元:时钟信号产生器,而且以上各个部件必须在时钟信号的控制下协调工作。

1.指令存储器的设计指令寄存器为ROM类型的存储器,为单一输出指令的存储器。

因此其对外的接口为clk、存储器地址输入信号(指令指针)以及数据输出信号(指令)。

(1)在IP wizard 中配置ROM,分配128个字的存储空间,字长为32位宽。

(2)选择输入具有地址寄存功能,只有当时钟上升沿有效时,才进行数据的输出。

(3)配置ROM内存空间的初始化COE文件。

最后单击Generate按钮生成IROM模块。

2.数据存储器的设计数据存储器为RAM类型的存储器,并且需要独立的读写控制信号。

因此其对外的接口输入信号为clk、we、datain、addr;输出信号为dataout。

数据存储器基本建立过程同ROM的建立。

3.寄存器组设计寄存器组是指令操作的主要对象,MIPS中一共有32个32位寄存器。

在指令的操作过程中需要区分Rs、Rt、Rd的地址和数据,并且Rd的数据只有在寄存器写信号有效时才能写入,因此该模块的输入为clk、RegWriteAddr、RegWriteData、RegWriteEn、RsAddr、RtAddr、reset;输出信号为RsData、RtData。

由于$0一直输出0,因此当RsAddr、RtAddr为0时,RsData以及RtData 必须输出0,否则输出相应地址寄存器的值。

另外,当RegWriteEn有效时,数据应该写入RegWriteAddr寄存器。

并且每次复位时所有寄存器都清零。

代码如下:module regFile(input clk,input reset,input [31:0] regWriteData,input [4:0] regWriteAddr,input regWriteEn,output [31:0] RsData,output [31:0] RtData,input [4:0] RsAddr,input [4:0] RtAddr);reg[31:0] regs[0:31];assign RsData = (RsAddr == 5'b0)?32'b0:regs[RsAddr];assign RtData = (RtAddr == 5'b0)?32'b0:regs[RtAddr];integer i;always @(posedge clk)beginif(!reset)beginif(regWriteEn==1)beginregs[regWriteAddr]=regWriteData;endendelsebeginfor(i=0;i<31;i=i+1)regs[i]=0;regs[31]=32'hffffffff;endendendmodule4.ALU设计在这个简单的MIPS指令集中,微处理器支持add、sub、and、or、slt运算指令,需要利用ALU单元实现运算,同时数据存储指令sw、lw也需要ALU单元计算存储器地址,条件跳转指令beq需要ALU来比较两个寄存器是否相等。

32位MIPS处理器说明

32位MIPS处理器说明一、实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

二、实验原理及实验内容该32位MIPS处理器主要需要设计ALU、单周期、流水线。

下面分别讲述这三个部分的设计原理及实验内容。

1.ALUALU即算数逻辑单元,要求设计一个32位的ALU,实现基本的算术、逻辑、关系、位与移位运算。

输入32bit的A和B作为操作数,5bit的控制输入ALUFun和一位控制输入Sign,输出32bit的结果Z。

其功能表如下图所示:根据功能表和要求,我们在顶层模块中设计了32bit输入ALUSrc1和ALUSrc2,以及5bit控制ALUFunc,1bit控制Sign,32bit输出ALUOut。

设计了四个主要模块:ALU_ADD_SUB,ALU_CMP,ALU_Logic,ALU_Shift,并根据ALUFunc的值来确定使用的模块。

设计框图思路如下:(1)ALU_ADD_SUB这部分是ALU设计中最重要的一部分。

采用了8位超前进位级联,用与门来实现32位全加器。

减法由加法实现,在运算的开始由ALUFunc判断进行的是加法还是减法,如果是加法则直接将两个操作数输入全加器,最低进位为0,如果是减法则取ALUSrc2的反码之后再做加法运算,最低进位是1。

需要注意的是运算结束之后需要判断结果是否为0(这个在branch指令中尤为重要),是否为负数,还有是否溢出。

是否为溢出还需要检查控制符号,如果控制符号为有效(即有符号计算)则两正数相加得负或两负数相加得正则溢出,溢出则结果符号位反了,再进而判断是否为负。

若为无符号运算,加法结果溢出则最高进位为1,且结果不为负;减法结果溢出等价于结果为负,即最高进位为0。

而结果为0等价于全部位都取0。

(2)ALU_Shift移位运算分别有逻辑左移,逻辑右移,算术右移三种情况。

首先判断是逻辑移位还是算术移位来决定填充0还是填充逻辑位。

之后采取先将操作数根据左移还是右移的判断做出32位扩充,再根据shamt从最高位到最低位判断是否为0来决定取那几位操作数,最后得到移位的结果。

实验1 MIPS指令系统和MIPS体系结构

实验1 MIPS指令系统和MIPS体系结构1.1 实验目的1.了解和熟悉指令集模拟器。

2. 熟练掌握模拟器MIPSsim的操作和使用方法。

3. 熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解。

4. 熟悉MIPS体系结构。

1.2 实验平台实验平台采用指令级和流水线操作级模拟器MIPSsim1.3 实验内容和步骤首先要阅读MIPSsim模拟器的使用方法,然后了解MIPSsim的指令系统和汇编语言。

1. 启动MIPSsim2. 选择“配置”→“流水方式”选项,使模拟器工作在非流水方式下。

3.参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。

可以先载入一个样例程序,然后分别以单步执行一条指令、执行多条指令、连续执行、设置断点等的方式运行程序,观察程序的执行情况,观察CPU中寄存器和存储器的内容的变化。

4.选择“文件”→“载入程序”选项,加载样例程序alltest.s,然后查看“代码”窗口,查看程序所在的位置。

(起始地址为0x00000000)5.查看“寄存器”窗口PC寄存器的值:[PC]=0x6. 执行load和store指令,步骤如下:(1)单步执行一条指令(F7)(2)下一条指令地址为0x ,是一条(有,无)符号载入(字节,半字,字)指令。

(3)单步执行一条指令(F7)(4)查看R1的值,[R1] =0x 。

(5)下一条指令地址为0x ,是一条(有,无)符号载入(字节,半字,字)指令。

(6)单步执行一条指令。

(7)查看R1的值,[R1] =0x 。

(8)下一条指令地址为0x ,是一条(有,无)符号载入(字节,半字,字)指令。

(9)单步执行一条指令。

(10)查看R1的值,[R1] =0x 。

(11)单步执行一条指令。

(12)下一条指令地址为0x ,是一条(有,无)符号载入(字节,半字,字)指令。

(13)单步执行一条指令(F7)(14)查看内存BUFFER处字的值,值为0x 。

7. 执行算术运算类指令。

mips 实验报告

MIPS实验报告1. 引言MIPS(Microprocessor without Interlocked Pipeline Stages)是一种经典的指令集架构(ISA),被广泛应用于计算机体系结构的教学和研究中。

本实验报告将介绍使用MIPS指令集实现的一系列实验,包括指令执行、流水线设计和缓存优化等。

2. 实验目标本次实验的主要目标是通过设计和实现一系列MIPS指令,加深对计算机体系结构的理解,并掌握MIPS指令的执行过程和流水线设计。

3. 实验环境为了完成实验,我们使用了MIPS模拟器和相应的开发工具。

这些工具提供了一个仿真环境,可以在计算机上执行MIPS指令,并提供了调试和测试的功能。

4. 实验步骤步骤1:设计指令首先,我们需要设计一系列MIPS指令,以实现特定的功能。

例如,我们可以设计一个加法指令,将两个寄存器中的值相加,并将结果存储到另一个寄存器中。

步骤2:实现指令接下来,我们需要在MIPS模拟器中实现这些指令。

通过编写相应的汇编代码,我们可以将指令转化为机器码,并在模拟器中执行。

步骤3:调试和测试一旦指令实现完成,我们就可以开始调试和测试。

通过单步执行指令,我们可以观察程序的执行过程,并检查寄存器和内存中的数据是否符合预期。

步骤4:性能优化在实现指令的过程中,我们还可以考虑对程序进行性能优化。

例如,通过引入流水线技术,可以提高指令的执行速度。

此外,我们还可以设计和实现缓存系统,以减少内存访问的延迟。

5. 实验结果经过一系列的设计、实现和优化,我们成功完成了MIPS指令的实验。

通过观察实验结果,我们可以得出一些结论和发现。

6. 结论本次实验通过设计和实现MIPS指令,加深了对计算机体系结构的理解,并掌握了MIPS指令的执行过程和流水线设计。

通过调试和测试,我们进一步完善和优化了指令的实现。

实验结果表明,我们的设计能够成功执行各种指令,并具有一定的性能优化。

7. 参考文献参考文献提供了关于MIPS指令集和计算机体系结构的详细信息,为本实验提供了重要的支持和指导。

mips控制器设计实验原理

mips控制器设计实验原理MIPS(Microprocessor without Interlocked Pipelined Stages)是一种32位的RISC (Reduced Instruction Set Computing)处理器架构,旨在提高处理器效率和性能。

MIPS 架构的处理器被广泛应用于各种领域,包括计算机、嵌入式系统、网络设备、数字信号处理等需要高性能的应用中。

在本实验中,我们将学习如何设计一个基于MIPS控制器的处理器。

控制器是一个能够控制处理器各个子系统如存储器、算术逻辑单元(ALU)、输入/输出设备等的模块。

MIPS控制器的设计是关键,因为它可以决定处理器的运行效率和性能。

MIPS控制器的设计需要考虑以下几个方面:1. 指令解码MIPS指令集包含了大量的指令,但是由于指令采用RISC架构,指令集中的每一个指令都很简单,只有少量的寄存器、立即数和内存操作。

控制器需要能够识别每一个指令,并正确地解码指令中的操作数。

为了实现这个目标,控制器需要包含适当的译码电路和其他必要的逻辑门电路。

2. 流水线控制流水线是一种增加处理器效率和性能的技术,通过将指令的执行拆分为多个阶段,多个指令可以在同一时刻被处理。

MIPS架构使用了5级流水线结构,即取指令、指令译码、执行、访问存储器和写回结果。

控制器需要能够控制流水线的各个阶段,确保它们按照正确的顺序执行。

3. 异常处理处理器在执行指令时可能会出现各种错误,如未定义的指令、内存访问冲突、算术溢出等。

这些错误称作异常。

处理器需要能够捕获异常并采取适当的措施,如停止当前指令的执行、中断指令流并处理异常。

控制器需要包含适当的硬件和逻辑电路来处理异常。

4. 输入/输出一个处理器需要有输入/输出接口来连接外部设备,如键盘、鼠标、显示器、网络等。

这些设备通过输入输出端口(I/O端口)与处理器相连。

控制器需要能够控制I/O端口的数据传输,并确保数据在正确的时刻被传输。

实验一:MIPS指令集实验

深圳大学实验报告课程名称:计算机系统(3)实验项目名称:MIPS指令集实验学院:计算机与软件学院专业:计算机与软件学院所有专业指导教师:*****报告人:******* 学号:********** 班级:******* 实验时间:2017年10月16日星期一实验报告提交时间:2017年10月19日星期四教务处制一、实验目标:了解WinMIPS64的基本功能和作用;熟悉MIPS指令、初步建立指令流水执行的感性认识;掌握该工具的基本命令和操作,为流水线实验作准备。

二、实验内容按照下面的实验步骤及说明,完成相关操作记录实验过程的截图:1)下载WinMIPS64;运行样例代码并观察软件各个观察窗口的内容和作用,掌握软件的使用方法。

(80分)2)学会正确使用WinMIPS64的IO方法;(10分)3)编写完整的排序程序;(10分)三、实验环境硬件:桌面PC软件:Windows,WinMIPS64仿真器四、实验步骤及说明WinMIPS64是一款指令集模拟器,它是基于WinDLX设计的,如果你对于WinDLX这款软件十分熟悉的话,那么对于WinMIPS64也会十分的容易上手。

DLX 处理器(发音为"DeLuXe")是Hennessy 和Patterson合著一书《Computer Architecture - A Quantitative Approach》中流水线处理器的例子。

WinDLX是一个基于Windows的模拟器。

本教程通过一个实例介绍WinMIPS64的使用方法。

WinMIPS64模拟器能够演示MIPS64流水线是如何工作的。

本教程使用的例子非常简单,它并没有囊括WinMIPS64的各个方面,仅仅作为使用WinMIPS64的入门级介绍。

如果你想自己了解更多的资料,在给出的winmips64.zip中,有WinMIPS64 — Documentation Summary.html和winmipstut.docx两个文件可以供你随时参考,其中涵盖了WinMIPS64的指令集和模拟器的组成与使用方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

深圳大学实验报告课程名称:计算机系统(3)实验项目名称:MIPS指令集实验学院:计算机与软件学院专业:计算机与软件学院所有专业指导教师:*****报告人:******* 学号:********** 班级:******* 实验时间:2017年10月16日星期一实验报告提交时间:2017年10月19日星期四教务处制一、实验目标:了解WinMIPS64的基本功能和作用;熟悉MIPS指令、初步建立指令流水执行的感性认识;掌握该工具的基本命令和操作,为流水线实验作准备。

二、实验内容按照下面的实验步骤及说明,完成相关操作记录实验过程的截图:1)下载WinMIPS64;运行样例代码并观察软件各个观察窗口的内容和作用,掌握软件的使用方法。

(80分)2)学会正确使用WinMIPS64的IO方法;(10分)3)编写完整的排序程序;(10分)三、实验环境硬件:桌面PC软件:Windows,WinMIPS64仿真器四、实验步骤及说明WinMIPS64是一款指令集模拟器,它是基于WinDLX设计的,如果你对于WinDLX这款软件十分熟悉的话,那么对于WinMIPS64也会十分的容易上手。

DLX 处理器(发音为"DeLuXe")是Hennessy 和Patterson合著一书《Computer Architecture - A Quantitative Approach》中流水线处理器的例子。

WinDLX是一个基于Windows的模拟器。

本教程通过一个实例介绍WinMIPS64的使用方法。

WinMIPS64模拟器能够演示MIPS64流水线是如何工作的。

本教程使用的例子非常简单,它并没有囊括WinMIPS64的各个方面,仅仅作为使用WinMIPS64的入门级介绍。

如果你想自己了解更多的资料,在给出的winmips64.zip中,有WinMIP S64 — Documentation Summary.html和winmipstut.docx两个文件可以供你随时参考,其中涵盖了WinMIPS64的指令集和模拟器的组成与使用方法。

虽然我们将详细讨论例子中的各个阶段,但你应具备基本的使用Windows的知识。

现假定你知道如何启动Windows,使用滚动条滚动,双击执行以及激活窗口。

(一)、安装请按以下步骤在Windows下安装WinMIPS64 :1.为WinMIPS64 创建目录,例如D:\ WinMIPS64 2.解压给出的winmips64.zip压缩文件到创建的目录中。

(二)、一个完整的例子1.开始和配置WinMIPS64在winmips64这个子目录下,双击winmips64.exe文件,即打开了WinMIPS64模拟器,其外观如下图:为了初始化模拟器, 点击File菜单中的Reset all(Ctrl+R)菜单项即可。

WinMIPS64可以在多种配置下工作。

你可以改变流水线的结构和时间要求、存储器大小和其他几个控制模拟的参数。

点击Configuration/Floating Point Stages(点击Configuration 打开菜单,然后点击Architecture菜单项),选择如下标准配置:如果需要,可以通过点击相应区域来改变设置。

然后,点击OK返回主窗口。

在Configuration菜单中的其他四个配置也可以设置,它们是:Multi-Step, Enable Forwarding, Enable Branch Target Buffer 和Enable Delay Slot。

点击相应菜单项后,在它的旁边将显示一个小钩。

本次实验要求不要勾选“Enable Forwarding”。

2. 装载测试程序用标准的text编辑器来新建一个名为sum.s的文件,这个文件的功能是,计算两个整数A、B之和,然后将结果传给C。

程序如下:.dataA: .word 10B: .word 8C: .word 0.textmain:ld r4,A(r0)ld r5,B(r0)dadd r3,r4,r5sd r3,C(r0)halt在将该程序装载进WinMIPS64之前,我们必须用asm.exe来检验该输入程序的语法正确性。

asm.exe程序文件在所给的winmips压缩包里有,用命令行使用它。

具体操作为,打开终端,利用cd命令进到D:\ WinMIPS64目录中,然后直接使用asm.exe sum.s命令,检查输出结果是否无误。

在开始模拟之前,至少应装入一个程序到主存。

为此,选择File / OPEN,窗口中会列出当前目录中所有汇编程序,包括sum.s。

按如下步骤操作,可将这个文件装入主存。

•点击sum.s•点击open 按钮现在,文件就已被装入到存储器中了,现在可以开始模拟工作了。

你可以在CODE窗口观察代码内容,可以在DATE窗口观察程序数据了。

3. 模拟在主窗口中,我们可以看见七个子窗口,和一条在底部的状态栏。

这七个子窗口分别是Pipeline, Code, Data, Registers, Statistics, Cycles和Terminal。

在模拟过程中将介绍每一个窗口的特性和用法。

(1) Pipeline窗口在Pipeline窗口中,展示了MIPS64处理器的内部结构,其中包括了MIPS64的五级流水线和浮点操作(加法/减法,乘法和除法)的单元。

展示了处于不同流水段的指令。

(2) Code窗口我们来看一下Code窗口。

你将看到代表存储器内容的三栏信息,从左到右依次为:地址(符号或数字)、命令的十六进制机器代码和汇编命令。

我们可以看到,初始时,第一行为黄色,表示该行指令处于“取指”阶段。

现在,点击主窗口中的Execution开始模拟。

在出现的下拉式菜单中,点击Single Cycle 或按F7键。

这时,第一行变成了了蓝色,第二行变成了黄色,这表示第一行指令处于“译码”阶段,而第二行指令处于“取指”阶段。

这些不同的颜色代表指令分别处于不同的流水线阶段。

黄色代表“取指”,蓝色代表“译码”,红色代表“执行”,绿色代表“内存数据读或写”,紫色代表“写回”。

接着按F7,直到第五个时钟周期的时候,有趣的事情发生了,“dadd r3,r4,r5”指令没有从“译码”跳到其下一个流水阶段“执行”,并且“sd r3,C(r0)”指令,仍然停留在“取指”阶段,同时在terminal窗口显示一行信息“RAW Stall in ID (RS)”,思考一下这是为什么?(3) Cycls窗口我们将注意力放到Cycls窗口上。

它显示流水线的时空图。

在窗口中,你将看到模拟正在第五时钟周期,第一条指令正在WB段,第二条命令在MeM 段,第四条命令在处于暂停状态(installed),第五条指令也因此停滞不前。

这是因为发生了数据相关(第四条指令的dadd命令需要用到寄存器r5的值,但是r5的值并不可用)。

接着点击F7,到第五个时钟周期时,再次发生相关,造成停滞。

接着点击F7,直至第十三个时钟周期全部指令执行结束。

值得一提的是,Cycls窗口是分为两个子窗口的,左边的子窗口是一系列的指令,右边的窗口是图示的指令执行过程。

其中,左边子窗口的命令是动态出现的,当一条指令在进行“取指”时,该指令才出现,而且,当出现了数据相关的时候,所涉及到的指令会变色,暂停的指令会变成蓝色,而被其影响的后续指令会变成灰色。

(4) Data窗口在Data中,我们可以观察到内存中的数据,包括数据内容和地址两个方面,其中地址使用64位表示。

如果想改变一个整型的数据的值,左键双击该值所在的行,如果是想改变一个浮点类型的数据的值,那么请右键双击该值所在的行。

上图即为第十三个时钟周期的data窗口的图示,其中,左边一行即为用64位表示的内存地址,中间行为数据的内容,右边的一行为相关的代码。

可以看出,在这个时钟周期,A与B的值分别为0xa和0x8,C的值为0x12,表明A与B的值之和已经相加并保存到了C中。

(5) Registers窗口这个窗口显示存储在寄存器中的值。

如果该寄存器为灰色,那么它正处于被一条指令写入的过程,如果它用一种颜色表示,那么就代表,该颜色所代表的的流水线阶段的值可以用来进行前递(forwarding)。

同时,这个窗口允许你交互式的该变寄存器的值,但是前提是该寄存器不能处于被写入或者前递的阶段。

如果想改变一个整型的数据的值,左键双击该值所在的行,如果是想改变一个浮点类型的数据的值,那么请右键双击该值所在的行,然后按OK来进行确定。

上图即为第十三个时钟周期的Registers窗口的图示,很显然,其中可以很清楚的看出每个寄存器的值是什么。

(6)Statistics窗口最后我们来看一下Statistics窗口。

这个窗口是用来记录一些模拟周期的统计数据。

其中包括Execution,Stalls,和Code Size 三个大项。

其中,Execution用来显示模拟周期中指令数,执行周期数和CPI(没条指令所用周期数),Stalls用来表示暂停的周期数,并且分门别类的进行了统计,其中包括RAW Stalls,WAW Stalls,WAR Stalls, Structural Stalls, Branch Taken Stalls和Branch misprediction Stalls。

Code Size表示了代码的大小,用byte表示。

上图即为Statistics窗口的图示,其中表示了该程序有13个时钟周期,5条指令,CPI 为2.600,有4个RAW Stalls,代码大小为20个Bytes。

(三)、更多操作首先,点击File/Reset MIPS64(ctrl + R)进行重置。

如果你点击File/Full Reset,你将删除内存中的数据,这样你就不得不重新装载文件,所以点击File/Reload(F10)是一个很方便的重置的方法。

你可以一次推进多个时钟周期,方法是点击Execute/Multi cycle(F8),而多个时钟周期数是在Configure/Multi-step中设置的。

你也可以通过按F4一次完成整个程序的模拟。

同时,你可以设置断点,方法是,在Code 窗口中左键双击想要设置断点的指令,该指令会变成蓝色,然后点击F4,程序就会停在这条指令执行“ 取指”的阶段,如果想要清除断点,再次左键双击改行指令。

(四)、终端I/O的简单实例通过上面对WinMIPS64的了解,我们可以开始简单的使用该工具了。

这里,需要我们编写一个简单的终端输出“Hello World!!”的小程序,运行并且截图。

所以,我们需要了解如何将数据在终端中输出输入。

下图是I/O区域的内存映射,一个是控制字,一个是数据字:所以我们需要先将CONTROL和DATA地址读取到寄存器,然后分别在这两个区域内存储相应的序列号(如上图所示)和要显示在Terminal窗口的数据,同时,设置CONTROL 为9,我们能对其进行读取数据。