一种低功耗高稳定性晶体振荡器芯片的设计

DS1302中文手册

DS1302中文手册DS1302 是一款高性能、低功耗的实时时钟芯片,被广泛应用于各种需要准确计时的电子设备中。

一、DS1302 的基本特性1、实时时钟功能能够精确记录年、月、日、时、分、秒等时间信息。

2、低功耗设计在电池供电的情况下,仍能保持长时间的计时准确性。

3、数据存储具备 31 字节的非易失性静态 RAM,可用于存储一些关键数据。

4、简单的接口通过串行接口与微控制器进行通信,易于集成到系统中。

二、DS1302 的引脚功能1、 Vcc1 和 Vcc2Vcc1 是主电源引脚,Vcc2 是备用电源引脚。

当主电源正常供电时,芯片使用 Vcc1 供电;当主电源断电时,自动切换到 Vcc2(通常为电池)以保持时钟运行。

2、 GND接地引脚。

3、 CLK时钟输入引脚,用于同步数据传输。

4、 I/O数据输入/输出引脚。

5、 RST复位引脚,高电平有效。

三、DS1302 的通信协议DS1302 采用串行通信方式,通信数据以字节为单位进行传输。

1、起始位在每个字节传输开始时,RST 引脚被置为高电平,启动通信过程。

2、控制字节首先发送一个控制字节,用于指定后续操作是读操作还是写操作,以及要操作的寄存器地址。

3、数据字节根据控制字节的指示,接着传输数据字节。

4、停止位在传输完一个字节的数据后,将 RST 引脚置为低电平,结束本次通信。

四、DS1302 的寄存器1、时钟/日历寄存器包括年、月、日、时、分、秒等寄存器,用于存储时间信息。

2、控制寄存器用于设置时钟的工作模式,如是否开启振荡器、是否进行写保护等。

3、充电寄存器用于控制备用电源的充电特性。

4、 31 字节的 RAM 寄存器用于用户自定义数据存储。

五、DS1302 的初始化与设置在使用 DS1302 之前,需要进行初始化设置,包括设置初始时间、开启振荡器、关闭写保护等操作。

1、写入初始时间通过串行通信将准确的初始时间写入到相应的时钟/日历寄存器中。

2、开启振荡器将控制寄存器的相应位设置为 1,使振荡器开始工作。

实时时钟芯片ds1388的原理与应用

实时时钟芯片DS1388的原理与应用1. 介绍实时时钟芯片DS1388是一种高精度、低功耗的实时时钟芯片。

它集成了时钟、日历、闹钟和温度传感器等功能,广泛应用于各种电子设备中,例如计算机、通信设备、工业控制系统等。

2. 原理DS1388采用了CMOS技术,内部集成了时钟振荡器、电源监控电路和温度传感器等关键部件。

其工作原理如下:•时钟振荡器:DS1388内部集成了一个高精度的时钟振荡器,用于产生稳定的时钟信号。

该振荡器基于晶振或者外部电源提供的频率源进行工作,通过精确的频率控制,使得DS1388能够提供准确的时间和日期信息。

•电源监控电路:DS1388内部集成了电源监控电路,可以监测外部电池电量,并实时记录电池电量信息。

当外部电池电量低于一定阈值时,DS1388能够及时发出警报,提醒用户更换电池。

•温度传感器:DS1388还集成了温度传感器,用于实时检测芯片的工作温度。

通过监测温度,可以避免芯片过热,保证芯片的稳定工作。

3. 应用DS1388实时时钟芯片具有广泛的应用场景,主要包括以下几个方面:3.1 计算机系统在计算机系统中,DS1388常用于计算机主板上,用于提供系统时间和日期信息。

它能够提供高精度的时钟信号,并且能够通过电源监控功能实时监测电池电量,提醒用户更换电池。

此外,DS1388还可以与计算机的BIOS系统进行通信,实现系统启动时钟同步等功能。

3.2 通信设备在通信设备中,DS1388可以被用于提供精确的时钟信号,用于同步通信设备的各个模块。

例如,在无线基站中,DS1388可以提供准确的时钟信号,用于同步各个基站之间的信号传输,提高通信质量。

此外,DS1388还可以记录设备的运行时间和故障时间,帮助用户进行设备的维护和调试。

3.3 工业控制系统在工业控制系统中,DS1388可以用于记录设备的运行时间和操作时间,用于统计设备的使用情况。

通过记录运行时间和操作时间,可以预测设备的维护周期,并且根据维护周期进行设备维护工作。

射频接收芯片中CMOS晶体振荡器的设计

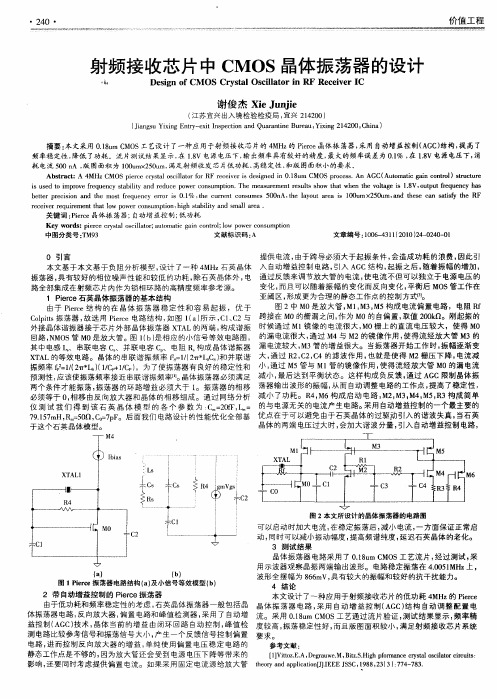

摘 要 : 文采 用 01u M S 艺设 计 了一种应 用 于射频 接 收 芯片 的 4 H 的 Pec 本 . mC O 工 8 M z i e晶体振 荡器 , r 采用 自动 增 益控 制 ( G ) A C 结构 , 高 了 提 频率稳 定性 , 降低 了功耗 。流 片测试结 果显 示, 1 电源 电压 下 , 出频率 具有较 好 的精度 , 大的频率误 差 为 0 % , 1 V 电源电压 下 , 在 v 输 最 . 1 在 _ 8 消 耗 电流 50n , 图面积 为 10 m 2 0 m 满足射 频 收发 芯片低功耗 、 0 A 版 0u X5u , 高稳 定性 、 和版 图面积 小 的要 求 。

关键词 :i c Pe e晶体振 荡器 ; r 自动增 益控制 ; 低功 耗

Ke r s ir ec sa s i ao ; uo t an c nt llw o rc n u to y wo d :p ec r t o cl tr a tmai g i o r ;o p we o s mp in y l l c o

i sd t mpo efe u n y sa ly a d r d c o rc n u to .T e me s rme tr s lss o h twh n t ev h g s .V, u p tfe u n y h s s u e o i rv r q e c tbit n e u ep we o s mp in h a u e n e ut h w ta e h o a ei 18 o t u r q e c a i b t r p e iin a d h s rq e e ro s 0.% ,h u rnt o s et rcso n te mo tfe u n y e rr i 1 e te c re c n ume 0 A,h a o tae s O m 2 u a d h s a stsy te RF s 5 0n t e ly u ra i l Ou x 50 m, n te e c n aif h rc ie e u rme tta o o rc n u to hg tbii n mala e e ev rrq ie n h tlw p we o s mp in, ih sa lt a d s l r a. y

门控时钟 低功耗芯片设计方案

门控时钟低功耗芯片设计方案全文共四篇示例,供读者参考第一篇示例:门控时钟低功耗芯片设计方案随着物联网技术的飞速发展,原本以人类为中心的智能家居和智能办公等应用场景也逐渐普及,门控时钟低功耗芯片成为这些智能设备的重要组成部分。

门控时钟低功耗芯片设计方案要求具有高性能、低功耗、稳定可靠等特点,以满足现代智能设备对芯片性能的需求。

1. 高性能:门控时钟低功耗芯片需要具有高性能的时钟控制功能,能够对设备的时序信号进行准确控制,确保设备的正常运行。

2. 低功耗:门控时钟低功耗芯片需要具有低功耗的特点,以延长设备的使用时间,提高设备的续航能力。

3. 稳定可靠:门控时钟低功耗芯片需要具有稳定可靠的性能,能够在各种工作环境下保持稳定的工作状态,确保设备的正常运行。

4. 外设接口丰富:门控时钟低功耗芯片需要具有丰富的外设接口,以支持设备与其他外部设备的连接和通讯。

5. 易集成:门控时钟低功耗芯片需要具有易于集成的特点,能够方便地与其他组件进行接口连接,实现功能的扩展和定制。

1. 芯片选用:在选择芯片时,可以考虑采用低功耗的CMOS工艺制程,以降低整体功耗。

可以选择具有高性能和稳定可靠性的时钟控制器芯片,以确保时序信号的准确控制。

2. 功耗优化设计:在芯片设计过程中,可以采用功耗优化设计策略,通过降低功耗模块的工作频率、优化电源管理电路等方式,降低整体功耗,延长设备的续航时间。

3. 时钟控制算法优化:通过优化时钟控制算法,可以提高时钟控制的准确性和稳定性,确保设备的正常运行。

可以提供丰富的时序控制功能,以满足不同应用场景对时序信号的需求。

4. 外设接口设计:在芯片设计中,可以设计丰富的外设接口,如UART、SPI、I2C等接口,以支持设备与其他外部设备的连接和通讯。

可以提供GPIO接口和PWM输出等功能,实现设备的功能扩展和定制。

5. 集成设计:在芯片设计中,可以将时钟控制器、功耗管理电路、外设接口等功能集成到同一芯片中,实现功能的集成和有效管理。

基于C8051F061的微机补偿晶体振荡器

误差 大 将 近 一 个 量 级 , 限定 A/ 引起 的 误 差 为 故 D

±2 5 0 ( 0 . ×1 一5 。 C~+9 。 。由 5C)

一 一

厂 。

() 1

2糍 50 ×.51 … 0 0—8 × 0 2 O

式 中:—— 晶体 频 率 随温 度 变 化 的最 大 斜 率 ; s T —— 温度 跨度 ; M 一 A D引入误 差; 一 / ~

宇航 计 测技 术

压控 振荡 器 ( xO) VC 等组 成 , 原 理 框 图 如 图 1所 其 示 。其 中温度 传感 器 与 VC O 中 的石 英 晶 体 之 间 X 通 过导热 硅胶 紧密 粘 合在 一 起 , 以达 到很 好 的热耦

合。

图 3 科 尔 匹兹 电路 图

作为 系统 的控制 核 心 , 85F 6 是 完 全 集 成 的混 C 0101 合 信号 片上 系统 型 MC 芯 片 , U 内部 集 成 了丰 富 的 高性能 硬件 资源 。

A src A o e kn f mir c mp tr c mp n ae rsa siao ( C b tat n v l id o co o u e o e std cy tl o c lt r M XO ) b s d o l a e n

C8 5 F 6 spe e td Th 0 1 0 1mirc n r l rh sr h h r waers u csa dma e lu e 0 1 0 1i rsn e. eC8 5 F 6 co o tol a i ad r eo re n k sf l s e c u o ot re Ot eM C fs f wa ,S h XO a a y a v na e u h a i l tu tr ,s l sz ,lw o rc n h sm n d a tg ss c ssmpesr cu e mal i e o p we o — s mpin a d s o tsatpe e t gt eec Isc mp st dct r r :fe u n y tmp rtr tbl u t n h r tr rh ai i t.t o o i i iaosae rq e c -e eau esa i— o n m en i

嵌入式低功耗上电复位与晶振电路设计

嵌入式低功耗上电复位与晶振电路设计嵌入式系统通常用于对资源有限的设备上,这些设备往往需要在功耗和成本等方面做出不少的牺牲,因此嵌入式系统的电源管理非常重要。

在嵌入式系统中,上电复位和晶振电路是非常基础并且重要的电路,本文将介绍如何设计嵌入式低功耗上电复位与晶振电路。

1. 上电复位电路设计上电复位电路是在MCU芯片在接收到电源供电后,自动将其所在的每个模块、寄存器等先设置为默认状态,并强制系统从开机时的起点开始运行,以保证系统具有可靠的运行性能。

也就是说当我们将嵌入式系统的电源接入时,每个模块都应该是按照“出厂时”的状态进行初始化操作。

而上电复位电路本身需要保证在模块处于不稳定状态时,能够使CPU被强制复位并进入到正常的执行流程中。

常规的上电复位电路设计保留了一个名为“复位端口”的引脚。

当此引脚被接通至电源时,MCU将被复位。

MCU内部的复位控制单元会确保系统重新回到开机状态。

当一个简单的氧化锌陶瓷电容被加至上电复位电路上,可提高复位电路的可靠性。

这个电容通过在上电时对复位线施加一个脉冲,确保了MCU的复位过程。

当电容充电时,CPU 的Vcc可能很快地达到满电压,但复位电路保持复位端口的输出低电平,确保MCU保持复位状态尽可能长的时间。

过去,为了能够确保复位电路在振荡器上电失效之前正常工作,电容必须由一个跨越 5 V 的 Zener 稳压二极管保护。

但是,该方法使用复位线上的氧化锌陶瓷电容会导致电流过大,且电容非常大,不适合于嵌入式系统(MCU),其较小的、低功耗微控制器可能无法将其充电。

此外,这种复位电容不适用于电平转换电路,因为当我们使用多个阶段的开关电源时,MCU的电压可能低于复位电路的起始电压。

这意味着,这个时候MCU不可用就需要等到电容电荷被释放了一段时间,才能充上电。

常规上电复位电路优点在于设计简单,不需要任何特殊的器件,只需加入少量的电容和电阻即可。

但是它的主要问题仍然是带来的系统复位延迟,因为MCU的实际复位过程必须等待复位电路的充电时间。

qco80000

qco80000概述qco80000是一款高性能的Quartz Crystal Oscillator(石英晶体振荡器)。

它具有极高的频率稳定性和精度,广泛应用于各种电子设备中。

本文档将介绍qco80000的特点、工作原理、使用方法和常见问题解答。

特点•高频率稳定性:qco80000采用优质的石英晶体材料,能够提供更高的频率稳定性,确保设备在长时间使用中保持准确的时间基准。

•高精度:qco80000内置精密的时钟电路,具有非常高的频率精度,能够满足对时间精确度要求较高的应用场景。

•低功耗:qco80000采用先进的低功耗设计,能够在提供高性能的同时,尽可能减少功耗,延长电池寿命。

•小尺寸:qco80000体积小巧,适合于各种空间有限的应用场景,方便集成到各种设备中。

工作原理qco80000的工作原理基于石英晶体振荡器的特性。

石英晶体振荡器由石英晶体和频率控制电路组成。

石英晶体在电场作用下会产生机械振动,通过频率控制电路将这种机械振动转化为准确的电信号输出。

qco80000的频率控制电路采用了高精度的数字控制系统,能够对输出频率进行精确调节。

通过精密的频率校准算法和自适应控制技术,qco80000能够实现高度稳定和准确的输出频率。

使用方法qco80000的使用非常简单。

下面是基本的使用步骤:1.将qco80000连接到电源,确保电源电压符合规格要求。

2.将qco80000的输出信号接入到目标设备的时钟输入端。

3.根据实际需求,使用控制命令或参数设置qco80000的工作模式、频率等参数。

4.启动目标设备,qco80000将提供稳定准确的时钟信号。

除了基本的使用方法外,qco80000还具有丰富的功能和扩展接口,可以满足不同应用的需求。

用户可以参考附带的使用手册和开发文档,了解更多高级功能和定制选项。

常见问题解答1. qco80000的输出频率范围是多少?qco80000的输出频率范围为X到Y,具体的频率范围取决于具体型号和配置。

cd4047用法

cd4047用法CD4047用法介绍CD4047是一种CMOS低功耗多谐振荡器,常用于电子电路中的振荡器设计。

下面将详细介绍CD4047的用法。

1. CD4047基础概述CD4047是一款集成电路,具有低功耗和高稳定性的特点。

它可用于产生稳定的多谐振荡信号,适用于各种振荡器应用。

2. 常见的CD4047用法以下是CD4047的几种常见用法:单稳多谐振荡器CD4047可用作单稳多谐振荡器,通过改变电阻和电容的数值,可以实现不同的输出频率。

可以将此用法应用于音乐合成电路、闹钟和计时器等场景。

PWM波形发生器CD4047还可用作脉宽调制(PWM)波形发生器,通过调整电阻和电容,可以改变PWM输出的频率和占空比。

该用法广泛应用于电力变换器、亮度控制和电机驱动等领域。

线路保护器CD4047还可以在电路中用作过热保护器或过载保护器。

当电路中的温度或负载超过设定值时,CD4047会发出警报或触发其他相应的保护机制,以保护电路的安全运行。

频率分频器CD4047还可以用作频率分频器。

通过将输入信号与CD4047的引脚连接,并设置适当的分频因子,可以将输入信号的频率分成更低的频率。

这种用法常用于计数器、计时器和频率测量设备等。

3. CD4047的优点和适用性•低功耗:CD4047采用CMOS技术,具有低功耗的特点,适用于需要长时间运行和低耗能的应用。

•高稳定性:CD4047的输出频率稳定性高,能够产生较为精确的振荡信号。

•多功能:CD4047可应用于单稳多谐振荡器、PWM波形发生器、线路保护器和频率分频器等多种电路设计。

•高可靠性:CD4047集成了多种保护电路,能够工作在恶劣环境下。

结论CD4047是一款常用的CMOS多谐振荡器,具有低功耗、高稳定性和多功能的特点,适用于各种电路设计。

通过合理运用CD4047的特性,可以实现不同应用场景下的振荡器设计、PWM波形发生器、线路保护器和频率分频器等功能。

4. CD4047的工作原理CD4047内部包含了一个SR(Set-Reset)触发器,通过适当的连线和外部元件,可以将其工作在不同的模式下。

一款新型高频率稳定度ATCXO芯片的设计

些 需求 , 精度 虽然 很高 , 需 要集 成 A D和 D A转 但 / / 换 器 , 图面积大 而 且不 连续 谐 振信 号散 粒 噪 声 严 版 重, 用做 频率 源 , 制特 性可 能会 恶化 。传统 模拟 补 调

其 中

A/ = 3 )+ 1 V ) A ff A ( 一 4 ( o + o 一 () 1 是 A T切 晶 体 振 荡 器 的 拐 点 温 度 ( 2 约 8

电路 , 除电源 电压 的影 响。仿真结果表 明, 4 消 在一0℃ 一 10o宽温度 范围内 , 电压为 33V 频 率温度稳 定度为 ± . × + 0 C 工作 . , 20

1 ~, 0 且随电源电压变化率小于± . x 0 最差相位 噪声 为一 1 B/ z 0 z 一 3 B / z H 。 15 1~, 15d c H @10H 和 16d cH @1k z

65 6

补 偿 电路产 生 与 晶体频 率温 度特 性离 散 相反 的 电压 信号 . 将该 电压作用 于 压控 晶体 振荡 器 , 而抵 消 频 从 率 随温度 漂移 。

。

则 将 与 电源 电压 。 关 , 偏置 电流 , 与 无 则

无关 , 反相器工作 电压 将是一恒定值 , 从而保 证 反相 器工 作在 一个 稳 定 的工 作 点 7 A E C:5 0

d i1 . 9 9 j i n 1 0 - 4 0 2 1 . 6 0 5 o :0 3 6 / .s . 0 5 9 9 . 0 1 0 . 1 s

一

款 新 型 高 频 率 稳定 度 A C O芯 片 的设 计 木 TX

陈红梅 徐 静 平 ,

1 合肥 工业 大学微电子所 , . 合肥 2 00 ; 30 9

一种低功耗CMOS晶振电路设计

一种低功耗CMOS晶振电路设计彭伟娣;张文杰;谢亮;金湘亮【摘要】A CMOS inverter of two-transistors has two transistor gates coupled together by a coupling capacitor.DC gate bias is supplied to each transistor through high value resistors.The P-channel transistor is biased to a threshold below the power and the N-channel transistor is biased to a threshold above ground.The biasing voltage are developed through the use of a current mirror so that the biasing is independent of processing variables and temperature.A crystal oscillator created using such an inverter and biasing will operate at voltage substantially below sum of P and N thresholds and at a current level about one-fifth of that of a conventional CMOS oscillator.This low power CMOS crystal oscillator circuit was designed based on MXIC's 0.5 μm CMOS process,the current consumption of the whole circuit is under 750 nA.%在组成反相器的两个晶体管的栅端添加一个串联电容,直流通过连接在反相器内部的大电阻偏置这两个晶体管,P管被低于电源电压一个阈值的电压偏置,N管被高于低电压一个阈值的电压偏置,偏置电压通过电流镜镜像,因此受温度和工艺的影响较低.一种低功耗CMOS晶体振荡电路利用上述反相器,它的开启电压低于P管和N管的阈值之和,整体电路消耗的电流大概为传统电路的1/5.此晶振电路基于MXIC 0.5μm仿真模型验证实现,整体电路消耗的功耗电流小于750 nA.【期刊名称】《电子器件》【年(卷),期】2013(036)003【总页数】4页(P336-339)【作者】彭伟娣;张文杰;谢亮;金湘亮【作者单位】湘潭大学材料与光电物理学院,湖南湘潭411105;湘潭大学材料与光电物理学院,湖南湘潭411105;湘潭大学材料与光电物理学院,湖南湘潭411105;湘潭大学材料与光电物理学院,湖南湘潭411105【正文语种】中文【中图分类】TN431随着信息科学技术的迅猛发展,低功耗设计成为集成电路发展的趋势。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 引言

在现代电子电路系统中, 石英晶体振荡器具有 高的品质因 素, 能 精确 的定义 谐振 频率 ( resonant frequency ) , 提 供 系 统 标 准 参 考 源 ( ref erence source) , 因而扮演了极其重要的角色[ 1] . 晶体振荡 器常常作为系统时钟, 低功耗、高稳定性成为设计时 要考虑的重点因素.

XT AL 和 XT ALN 端的信号 均为非标 准的正 弦信号, 特别是 XT AL N 的振幅范围有可能超过电 源电压的范围, 因此, 在振荡器输出端设计了图 4 所 示的反相器缓冲电路, 对振荡器输出信号进行差分 放大整形. 同时, 利用 XT AL 和 XT AL N 的相位差 为 180! 的 特 性, 保 证 整 形 输 出 的 方 波 占 空 比 为 50% .

图 4 振荡器输出缓冲电路

图 4 中 CB 和 C 为互补使能控制信号. 当 CB 为 低时, C 为高, M 23 和 M24 均截止, 差分电路的偏置 电流被关断, 输出为低功耗模式的高阻态; 当 CB 为 高时, C 为低, 则 M23 和 M24 快速导通, 为放大器

第12 期

陈红梅, 等: 一种低功耗高 稳定性晶体振荡器芯片的设计

107

电路提供偏置电流, 此时, XT AL 和 XT AL N 信号 进行差分放大比较. 当 XT AL 比 XT AL N 高时, 差 分输出节点 A 和 B 的电位均为高, M13 截止, M 14 导通, 节点 P 输出为低, 则缓冲后输出信号 DIV 为 低; 当 XT A L 比 XT AL N 低时, 差分输出节点 A 和 B 的电位均为低, M I13 导通, M I22 截止, 节点 P 输 出为高, 缓冲后输出信号 DIV 为高. 如此循环进行, 输出方波信号 DIV. 由于 XT AL 和 XT AL N 为相位 差为 180!, 可 以 保 证 输 出 的 方 波 信 号 占 空 比 为 50% . 3. 3 使能控制电路

图 3 低功耗振荡器电路结构

作为放大器有源负载, M 2 则作为限流电阻, 限制了 振荡电路的电 流以防止晶振因驱动能 量过大而振 坏, 同时也减少了电流损耗; 在使能关断时, M 1 和 M 2 均截止, 关断 振荡器电 路, 电 路进入低 功耗模 式, 此时只有很小的漏电流[ 3] .

关于 C1 和 C2 的取值, 从功耗的角度, C1 和 C2 应当取小一点, 因为这样 MOS 管的工作电流可以比 较小, 但从频率稳定性 和电路抗干扰 特性来说, C1 和 C2 的取值不能太小[ 4 5] . 因此, C1 和 C2 的取值需 要在功耗和频率稳定度之 间进行折中. 本 设计中, C1 和 C2 的取值分别为 8 pF 和 10 pF. 3. 2 振荡器输出缓冲电路

输出控制信号 CT L 1 为高, 关断振荡器缓冲电路, 使 后面的单元模块均被关断, 输出高阻态, 大大降低了 电路在不能起振时的功耗. 电容 C5 主要滤去输出 方波信号的高次谐波, 降低电路的输出噪声[ 6] .

4 电路仿真与版图设计

文中采用 SM IC 0. 35 m CM OS 工艺设计了整 体电路, 其石英晶体谐振器的参数如表 1 所示. 所设 计的芯片性能如表 2 所示. 结果表明: 在电源电压为 5 V、振荡频率为 30 MH z、负载电容 15 pF 的条件 下, 输出占空比为 50 0. 8% 的方波信号, 芯片消耗 总电流 低 于 5 mA, 振 荡电 路 消 耗电 流 仅 为 0. 6 mA ; 输出高阻态时, 振荡器电流降至 3 A 以下, 功 耗大大降低. 振荡电路上电起振输出波形如图 6 所 示. 根据起振时间的定义( 输出电压达 到稳定值的 90% 所用的时间) , 可见起振非常快( 140 s) .

( Depar tment of Electr onics Science and T echno log y, H uazhong U niv ersity of Science and T echnolog y, Wuhan 430074, China)

Abstract: A cr ystal o scillat or chip w ith low pow er and high stability is presented. On t he basis of analyzing the disadv ant ages o f the conventio nal Pierce crystal oscillato r, a no vel cr ystal oscillator structur e has been pr oposed. T he chip can wo rk under two modes: no rmal operating mo de and pow er dissipat ion mode. Based on 0. 35 m CM OS process, the test results sho w that total co nsumpt ion o f the chip is less than 5 mA with pow er supply vo ltag e of 5 V, o scillatio n frequency of 30 M H z, lo ad capacitance of 15 pF , and t he oscillato r circuit is only 0. 6 mA, o ut put squar e w ave signal with dut y cy cle o f 50 0. 8% , frequency stabili t y 0. 5 10- 6 . By introducing t he po wer dissipatio n mode, cur rent consumptio n of t he oscillatio n circuit is dro pped to 3 A. Co mpar ed w ith the conventional str uctur e, the po wer dissipation has been r educed 60% , f requency st abilit y raised ten times. Key words: Pier ce cr ystal o scillator ; low po wer dissipation; hig h stability ; CM O S t echnolo g y

27 卷 第12期 2010 年 12 月

微电子学与计算机 MICROEL ECT RONICS & COM PU T ER

Vo l. 27 No . 12 December 2010

一种低功耗高稳定性晶体振荡器芯片的设计

陈红梅, 徐静平, 钟德刚

( 华中科技大学 电子科学与技术系, 湖北 武汉 430074)

中图分类号: T N432

文献标识码: A

文章编号: 1000- 7180( 2010) 12- 0105- 04

Design of Crystal Oscillator Chip with Low Power and High Stability

CH EN H ong m ei, XU J ing ping, ZH ON G De gang

摘 要: 分析了传统 P ierce 振荡器不足 , 提出了改进型的振荡器结构, 并基于 0. 35 m CM OS 工艺, 设计实现了 一

款低 功耗高稳定性的晶体振荡器芯片. 芯片有两种 工作模 式: 正 常工作 模式和 低功耗 模式. 测试结 果表明, 在电 源

电压为 5 V 、振荡频率为 30 M H z、负载电容 15 pF 时 , 芯片消耗总电流低于 5 mA , 振荡电路消耗 电流仅为 0. 6 m A,

收稿日期: 2009- 09- 21; 修回日期: 2009- 11- 25 基金项目: 国家自然科学基金项目( 60776016)

10 6

微电子学与计算机

耗. 采用 SM IC 0. 35 m CMOS 工艺完成了该芯片 的设计. 结果表明, 芯片起振快、功耗低, 非常适合应 用于高精度时钟系统.

图 2 晶体振荡器芯片系统框图

3 关键电路设计

3. 1 改进型低功耗振荡器电路 文中设计的改进型低功耗振荡器电路, 集成了

一个带使能控制的 CMOS 放大器与一个外部石英 晶体的振荡器. 节点 XT AL 和 XT ALN 分别连接石 英晶振的两端. 如图 3 所示.

MP 1 和 MN1 构成 CM OS 反相器, 与石英晶体 并联, 通过对地连接 两只电容 C1 ( C11 + C12 ) 和 C2 ( C21 + C22 ) 构成基本的振荡器电路. 借助反 馈电阻 Rf 将放大器的直流工作点偏置在 V D D/ 2, 使 M OS 管工作在线性区, 以获得较大的增益. P _CT L 和 N_ CT L 信号实现使能控制, 降低了电路功耗: 在电路 正常起振时, 大尺寸管子 M1 和 M2 快速导通, M 1

表 1 30 M H z 石英晶体 参数

f / MHz 30

Rm / 17. 2

Lm/ mH 4. 36

Cm/ fF 6. 46

C0 / fF Q 2. 26 50000

图 5 CT L _GEN 控制电路的结构图

图 5 中 INH NA 和 INH N B 为 ENABLE 模块 得到的互补控制信号, XT AL N 为振荡器输出信号. EN ABL E 模 块 正 常 使 能 工 作 时, INH NA 为 高, INH N B 为低, 则 M 41 和 M 42 均截 止. INH NB 为 低, M30 快 速 饱 和 导 通, 与 二 极 管 连 接 的 M31、 M32、M33 构成基本的 偏置电路, 通过电流镜 镜像 为其它 支路提供 偏置电流. 由于 M 31、M32、M I33 均为二极管连接, M36 的 栅极电压 大小近似 为 2/ 3VDD. M36 和 M37 构成基本差分对结构, 输入的 差分信号分别为 2/ 3VDD 和 XT ALN, M 40 为差分 对电路提供微弱的偏置电 流, M 34 和 M35 为 差分 对电路的负载. 工作时, XT L AN 信号与 2/ 3VDD 相 比较, 当振 荡 电路 正 常起 振, 且 XT LAN 大 于 2/ 3VDD 时, 差分对输出为低, M 38 导通, 输出控制信 号 CT L 1 为低, 驱动振荡器输出缓冲电路正常工作, 电路输出方波信号; 当振荡电路不能正常起振, XT L AN 小于 2/ 3VDD 时, 差分输出为高, M38 截止,