计算机综合课程设计 - 东南大学

东南大学微机实验综合课程设计

东南大学自动化学院微机实验及课程设计报告《参数可调波形发生器》姓名:学号:专业:实验室:组别:同组人员:设计时间:评定成绩:审阅教师:目录一.设计目的和要求--------------------------------------3 二.原理设计--------------------------------------------4 三.方案论证与实现--------------------------------------6 四.设计思路及流程图--------------------------------------------------------7 五.编程实现--------------------------------------------------------------------10六.方案测试与结果分析----------------------------------18 六.改进与提高------------------------------------------19 七.分析与总结------------------------------------------19一、设计要求1)基本要求编制1 个参数在线可调的波形发生程序,由D/A 输出,构成参数在线可调的波形发生器,并用示波器观察波形。

函数波形可选f(t)=asin(bt),其中a、b参数在线可调(也可自己选择,但要求至少2 个参数可调且调节很明显)。

参数调节采用如下两种方式之一:(1)两个可调电位器输出通过A/D 转换后作为可调参数;(2)参数通过实验装置上的键盘实时修改(调整);(3)精确时间,开关选择标准信号输出(例如a=2V, b=100πRAD/s,即50Hz 正弦波)。

2)设计提示(1)当用电位器调节参数时,输出零不能对应相应的参数值就为零;(2)当通过键盘修改参数时,先键入参数名如“a”,显示当前参数值,修改后再键入参数名,则修改参数完成,随后输出波形发生变化。

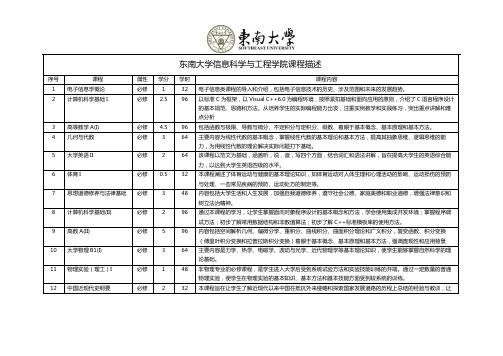

东南大学信息科学与工程学院2013级课程描述

学生了解近现代中国在改革浪潮中的大事变。

26 马克思主义基本原理必修 3 48 主要介绍马克思主义及其原理,包括世界的物质性及其发展规律,事物的普遍联系与发展,客观规律性与主

41 军事地形学与野外生存选修 2 33 介绍现代战争中地形对战略和战术的影响、现代军事侦查技术对士兵技能的要求、野外生存必备的生物、物

54 大数据(卓工)限选 2 32 内容包括大数据技术基本原理和Hadoop 的基础知识,了解SQL语言。

68 系统试验(通信组)限选 1.5 48 内容包括信道的定义、分类及模型,模拟调制系统的基本原理、性能指标及分析设计方法,让学生掌握数字。

东南大学计算机硬件课程设计报告

计算机硬件课程设计设计报告学号:09008112 姓名:马京亚成绩:学号:09008123 姓名:郭晨成绩:东南大学计算机科学与工程学院二〇一〇年十一月目录一、设计名称: (3)二、实验目的: (3)三、实验任务: (3)四、设计方案: (4)1.数据格式和指令系统 (4)2.硬件结构设计 (5)3.数据通路设计 (6)4.控制器设计 (7)5.指令的微程序表 (10)6.总电路图及Rom (11)五、设计优化 (12)1.更改时序 (12)2.增加指令 (13)3.减少ROM空间 (17)4.总电路图 (19)六、测试结果与性能分析 (20)1.测试程序 (20)2.时序图 (21)3.编译报告中资源使用情况 (22)七、课程设计总结 (23)微程序控制的模型计算机的设计与调试二、实验目的:1.综合运用“计算机组成原理”和“数字电路”等课程的知识,通过对模型机的设计和调试,加深对计算机各部件工作原理的认识。

2.进一步掌握运用EDA 技术进行设计和调试的工作方法。

3.掌握计算机硬件设计的思想,方法及工作过程,进一步培养工程设计的能力。

三、实验任务:1.自行规定数据格式和指令格式,在所提供的条件范围内设计一台由微程序控制的模型计算机。

2.根据设计方案,将模型机调试成功,对设计进行优化。

3.整理出相关文件。

(1)数据格式和指令系统。

(2)总框图。

(3)详细电路图。

(4)微指令格式和微程序。

(5)调试过程和测试结果(包括测试程序)。

1.数据格式和指令系统采用8 位数据通路,数据采用8 位二进制定点表示。

7 6 5 4 3 2 1 0.设置7 条机器指令和2条面板操作指令(1)面板操作指令a.输入地址为PC 置初始值,即输入程序的起始地址,当K1 开关置“1”,K2 开关置“0”时执行此操作;b.输入程序将程序输入到内存的指定区域,当K1,K2 开关均置“1”时,由面板输入开关输入程序;c.本模型机设置K3 开关,K3 置1 表示执行单步操作;d. START 表示启动开关。

计算机综合课程设计

指令中第3操作数可使用16位二进制立即数

相对寻址

操作数是下一条指令的PC值(PC+4)加上一个 32位偏移量

寄存器寻址

操作数存放在寄存器中,指令里放的是寄存器号

寄存器相对寻址

操作数存放在数据存储器中,其有效地址由两部 分组成,基地址放在一个寄存器中,偏移部分为 一个16位的立即数 2019/8/4 P.7

教育部-英特尔精品课程

MiniSys指令目录

算术指令-add, addu, addi, addiu, sub, subu

逻辑指令-and, andi, or, ori, xor, xori, nor, sll, srl, sra, sllv, srlv, srav

数据传送指令-lw, sw, lui 比较、条件转移指令-beq, bne, slt, slti,

教育部-英特尔精品课程

计算机系统综合课程设计

基于MIPS32的SOC设计实践(上)

(Verilog+Quartus Ⅱ+Cyclone版)

主讲 杨全胜

东南大学计算机科学与工程学院

2019/8/4 P.1

教育部-英特尔精品课程

主要内容

MiniSys 指令系统介绍 MiniSys CPU的设计

2019/8/4 P.13

教育部-英特尔精品课程

部分MiniSys指令详解

减法指令(R-format)

sub $s1, $s2, $s3 # $s1=$s2-$s3

6-bit op 0

000000

5-bit rs 18

10010

5-bit rt 19

10011

5-bit 5-bit 6-bit rd shamt funct

“计算机系统综合设计”报告

.6.

本组设计中各个部件的设计与特色概述(含关键代码)

CPU 部分 本组设计的 CPU 为 32 位 MIPS 指令单周期,全部采用 Verilog HDL 语言实

现,各模块连接时使用顶层实例化的方式。主要性能和特色如下: 1) 采用哈佛存储结构,独立的 2KB 的指令存储器和 2KB 的数据存储器。 2) 设计过程中,避免复杂电路,加快了指令的执行速度。

2.2 MIPS32 汇编器 主要功能: 1. 对用 MiniSys 汇编语言编写的 MiniSys 源程序(含伪指令)进行语法格式 检查,能够报错并定位错误语句; 2. 将检查为正确的源程序翻译成可以被 CPU 直接调用并执行的机器码。从 源程序翻译得到的机器码为两部分,代码部分翻译所得机器码存放成 prgmip32.mif 文件,数据部分翻译所得机器码存放成 dmem32.mif 文件。 主要基于编译的基本原理和方法,给出基于 LL(1)语法分析方法的 MiniSys 汇编器的设计和 C 语言实现。LL(1)分析表易于手工构造,适合用于实现 MiniSys 汇编器的实践。 MiniSys 汇编程序程序设计如下: 设栈顶符号为 X,读入单词为 a,#为输入带上字符串结束符号,栈初始化为 {#S},其中#为栈底元素,S 为语法初始符(此时,S 为栈顶,所以 X=S), 调用扫描器读入源程序文件第一个单词 a。 (1) 如果 a 是新变量名,填入变量名表。 (2) 如果 a 是新指令标号,填入标号名表。 (3) 如果 X=a=#,表示识别成功,退出分析程序。 (4) 如果 X=a≠#,匹配,如果已经识别出一个指令句子或变量定义语句, 调用机器码生成器,生成机器码,弹出栈顶符号 X,调用扫描器读入 源程序文件下一个单词 a。 (5) 如果 X 是终结符,且 X≠a,则说明程序有语法错误,退出。 (6) 如果 X 是非终结符,查预测表 M,如果 M[X,a]存放产生式编号,则 弹出 X,而将产生式右部以自右向左的顺序压入栈内,输出带上记下 产生式编号,如果 M[X,a]存放出错标志,则说明程序有语法错误, 退出。

计算机系统综合课程设计-东南大学计算机科学与工程学院

计算机系统综合设计

设计报告

组长:张冠群(09003105)

成员:杨俊(09003209)

孙啸寅(09003112)

万乾坤(09003218)

李传佑(09003214)

刘森(09003110)

黄河(09003206)

东南大学计算机科学与工程学院

二OO六年九月

注:本设计报告中各个部分如果页数不够,请大家自行扩页,原则是一定要把报告写详细,能说明本组设计的成果和特色,能够反应小组中每个人的工作。

报告中应该叙述设计中的每个模块。

设计报告将是评定每个人成绩的一个重要组成部分。

Cs138的vwf图

的vwf图

的vwf图

UART的vwf图

vwf图

的vwf图

的vwf图

的vwf图(此处为了演示方便,暂时把初值置为8)。

2011版“计算机系统综合设计”设计报告模板

计算机系统综合课程设计

设计报告

组长:

成员:

东南大学计算机学院

二0 年月

注:本设计报告中各个部分如果页数不够,请大家自行扩页,原则是一定要把报告写详细,能说明本组设计的成果和特色,能够反应小组中每个人的工作,尤其要表现出每个同学完成教材中思考题的最高难度系数。

报告中应该叙述设计中的每个模块。

设计报告将是评定每个人成绩的重要组成部分之一,因此要在报告中明确标明每个模块的设计者。

设计报告最后一页是验收表和教师综合评价,请大家打印报告的时候将此页一并打印装订。

.1.

.3.

.5.

.7.

验收报告(此表由验收人员填)

教师综合评价:

.9.

教师签名:____________。

东南大学计算机系计算机系统课程设计汇编器原理描述

汇编器:平台环境:汇编器由Java语言写成,开发IDE为Eclipse。

实现功能:汇编器实现了真实指令,伪指令以及宏指令的解析以及机器码生成。

真实指令包括除了中断相关的break,systemcall,eret指令以外的所有r型,i型以及j型指令。

伪指令包括段定义伪指令,数据定义伪指令,数据对齐伪指令,指定程序开始伪指令(.end),程序定位伪指令(ORG_CODE)。

宏指令包括push指令以及pop指令。

汇编器还实现了对于输入指令的词法语法检查,所有的错误一次扫描内全部输出。

此外,汇编器同样提供了对于ROM以及RAM的管理,代码以及数据存放位置的指定功能。

程序结构:汇编器分为四个部分:预处理,词法分析,语法分析,代码生成预处理:将存放于指定位置的汇编程序读入,去除空行,多余的空格,注释等,形成供词法分析的汇编程序。

词法分析:将预处理完成的汇编程序转换为Token序列,转换后的Token序列形成tokenset集合,token分为指令助记符,数字,标号/变量名,寄存器,字符串以及错误字符六种类型,存储其类型,值,行号的信息。

转换过程中根据空格以及逗号划分各个Token,根据行数划分不同指令,分别识别每一种类型的Token并将其存入tokenset。

语法分析:将Token序列转换为指令序列,对指令进行语法检查,将指令分为R型指令,I型指令,J型指令以及宏指令,伪指令,错误指令,处理段定义伪指令,建立ROM,RAM 管理信息集合,建立并且填充标号表,变量表,初步指定指令地址以及数据地址,初步处理数据定义,数据对齐,程序开始,程序定位伪指令。

每一条指令存储了指令类型,指令助记符,参数集合,指令地址,指令标号(可选),指令所在行数的信息。

编码:创建ROM以及RAM分别对应的文件。

对于ROM将语法分析中从伪指令中得到的数据以及地址信息写入ROM文件。

对于RAM,实现各指令标号以及变量名的检索,地址/偏移的计算。

计算机综合课程设计

内部寄存器

简单UART控制(1)

功能 负责控制将CPU来的8位数据并转串, 然后按照异步串行通信数据格式输出, 将串口来的8位串行数据串转并,并 在CPU请求的时候输入给CPU。

2019/3/10 P.23

简单UART控制(2)

设计时注意事项

XTAL可以是单独的时钟信号,和系统的CLK不 一样。 假设外部时钟XTAL的频率是波特率的16倍(本设 计采用固定波特率9600b/s) 接收器接收数据的采样率也是波特率的16倍(既 XTAL频率)采用中间值采样的原则,也就是一个 数据位占16个接收时钟宽度,在第8个时钟的时候 采样。 数据格式固定为1位起始位,8位数据位和1位停止 位。起始位为0,停止位为1。串行输出线空闲状 态为1。

4位7段LED显示控制(3)

Reset (I) 初始化 D15~D0 (I)用于写数据 CS (I) 片选端 IOW(I)写信号 led00~led06 0位led输出线 led10~led16 1位led输出线 led20~led26 2位led输出线 led30~led36 3位led输出线 数据锁存器(FF00H)

2019/3/10 P.17

4×4键盘扫描电路设计(2)

输入输出安排

D15~D0(O)用于读出数据 CS(I) 片选端 CLK(I) 时钟信号 line3~line0(I)键盘行输出线 col3~col0(O)键盘列输入线 address1~address0(I)端口地址 IOR(I)读信号

计算机系统综合课程设计

基于MIPS32的SOC设计实践(下)

(Verilog+Quartus Ⅱ+Cyclone版)

东南大学 计算结构 课程设计 CPU设计报告

COA-CPU School of Information Science and Engineering Southeast University

The Design Report of the Microinstruction CPU Design

Figure 5 shows the key elements of Microprogrammed Control Unit. The set of microinstructions is stored in the control memory. The control address register contains the address of the next microinstructions to be read. When a microinstruction is read from the control memory, it is transferred to a control buffer register. The register connects to the control lines emanating from the control unit. Thus, reading a microinstruction from the control memory is the same as executing that microinstruction. The third element shown in the figure is a sequencing unit that loads the control address register and issues a read command.

2. Design Specification

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.24

2009年教育部-英特尔精品课程

MiniSys指令格式详解

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.22

2009年教育部-英特尔精品课程

MiniSys指令格式详解

100 100

100

100

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.23

2009年教育部-英特尔精品课程

MiniSys指令格式详解

注:MiniSys采用32位MIPS指令中最常用的31条 指令,其寄存器组织,指令格式等均采用MIPS指令系 统相同的格式。

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.10

2009年教育部-英特尔精品课程

MiniSys寄存器组 共有32个32位寄存器

2013-9-10

P.14

2009年教育部-英特尔精品课程

MiniSys指令格式(3)

(3)J-format

j 10000

6-bit op 2

# go to 10000

26-bit Target Address 2500 00010 00011 0000 0000 0000 1010

000010

2013-9-10

P.18

2009年教育部-英特尔精品课程

MiniSys指令格式详解

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.19

2009年教育部-英特尔精品课程

MiniSys指令格式详解

/people/yangqs/xtzhsj1/Index.aspx

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.3

2009年教育部-英特尔精品课程

SOC概述(2)

SOC的三种形态

以微处理器为核心,外围集成各种存 储器、控制电路、输入输出、A/D、 D/A等功能于一个芯片上 以数字信号处理器(DSP)为核心,多 个A/D、D/A,大容量存储器等集成 上述两种类型的混合,或者把系统算 法和芯片结构有机地集成在一起

左移2位

4 +

Regdst

PC+4

8/16/32/64位,如MicroBlaze、Nois、8051 SDRAM 控制器、LCD 控制器、总线控制器等 FIR滤波器、DES加密、音视频编码和解码等

处理器外设IP Core

DSP算法IP Core

通信控制器IP Core

MAC、Gbit收发器、CAM、协议转换等

2013-9-10 P.8

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.9

2009年教育部-英特尔精品课程

第2章 MiniSys指令系统介绍

MiniSys寄存器组 MiniSys指令目录 MiniSys指令格式 部分MiniSys指令格式详解

2013-9-10

P.20

2009年教育部-英特尔精品课程

MiniSys指令格式详解

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.21

2009年教育部-英特尔精品课程

MiniSys指令格式详解

/people/yangqs/xtzhsj1/Index.aspx

2009年教育部-英特尔精品课程

IP 核及在SOC中的地位(1)

IP资源复用的理念

IP资源复用(IP Reuse)是指在集成电路设 计过程中,通过继承、共享或购买所需的部 分或全部知识产权内核(IP Core),进行设 计、综合和验证,从而加速流片设计过程的 设计方法 IP Core是一种商品,SOPC的技术核心: 是可编程逻辑器件设计工程师价值体现的主 要途径

Write

2013-9-10

P.28

MIPS instruction format R-format op rs rt rd func I-format op rs rt immediate J-format address op

MemtoReg MemWrite op func jal 控制 单元 Sftmd/sftm/I_format Alusrc jmp | jal jrn nBranch Branch 1 Regwrite

如:Xilinx的IP Capture和Core Generator 等

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.7

2009年教育部-英特尔精品课程

IP 核及在SOC中的地位(3)

IP核的分类

微处理器IP核

软硬件协同设计

电路的设计、综合、布局布线 软件与硬件的划分、协同设计、协同仿真 嵌入式操作系统、嵌入式系统程序和应用程序 的开发

/people/yangqs/xtzhsj1/Index.aspx

IP集成复用技术及设计环境

2013-9-10 P.5

2013-9-10 P.1

2009年教育部-英特尔精品课程

主要内容

SoC设计概述 MiniSys 指令系统介绍 MiniSys 的设计 外围电路及控制系统设计 软件的设计

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

2013-9-10 P.12

/people/yangqs/xtzhsj1/Index.aspx

2009年教育部-英特尔精品课程

MiniSys指令格式(1)

(1)R-format

5-bit rs 2 00010 5-bit rt 3 00011 5-bit rd 1 00001 5-bit shamt 0 6-bit funct 32

Байду номын сангаас

其它类型IP Core

/people/yangqs/xtzhsj1/Index.aspx

2009年教育部-英特尔精品课程

IP 核及在SOC中的地位(4)

IP Core设计:编码风格

编码风格(Coding Style)是基于HDL的 IP Core源码编写的指导性文档,关系到IP Core的可读性、易于集成性及其质量 编码风格一般包含几个方面的约定:文件 头和版本说明、联机注释、命名规则、可 综合编码(UCF)等

(2)I-format

lw $1, 10($2)

6-bit op 35 5-bit rs 2 00010

# $1=Memory[$2 +10]

5-bit rt 1 00011 16-bit Address/Immediate 10 0000 0000 0000 1010

100011

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.16

2009年教育部-英特尔精品课程

MiniSys指令格式详解

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.17

2009年教育部-英特尔精品课程

MiniSys指令格式详解

/people/yangqs/xtzhsj1/Index.aspx

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.11

2009年教育部-英特尔精品课程

MiniSys指令目录

算术指令-add, addu, addi, addiu, sub, subu 逻辑指令-and, andi, or, ori, xor, xori, nor, sll, srl, sra, sllv, srlv, srav 数据传送指令-lw, sw, lui 比较、条件转移指令-beq, bne, slt, slti, sltu, sltiu 无条件转移指令-j, jr, jal

add $1, $2, $3 # $1=$2+$3

6-bit op 0 000000

00000 100000

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.13

2009年教育部-英特尔精品课程

MiniSys指令格式(2)

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.4

2009年教育部-英特尔精品课程

SOC概述(3)

设计中的关键技术

设计描述技术

Verilog HDL/VHDL/AHDL System C、C-VHDL混合描述

2009年教育部-英特尔精品课程

计算机系统综合课程设计(3)

基于MIPS32的SOC设计实践(上)

(Verilog+Quartus Ⅱ+Cyclone版)

主讲 杨全胜

东南大学计算机科学与工程学院

/people/yangqs/xtzhsj1/Index.aspx

/people/yangqs/xtzhsj1/Index.aspx

2013-9-10

P.15

2009年教育部-英特尔精品课程