运算放大器的保护环设计

adhv4702-1 精密运算放大器-数据手册说明书

Rev. ADocument FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.O ne Technology Way, P .O . Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 ©2018-2019 Analog Devices, Inc. All rights reserved. Technical Support /cnADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

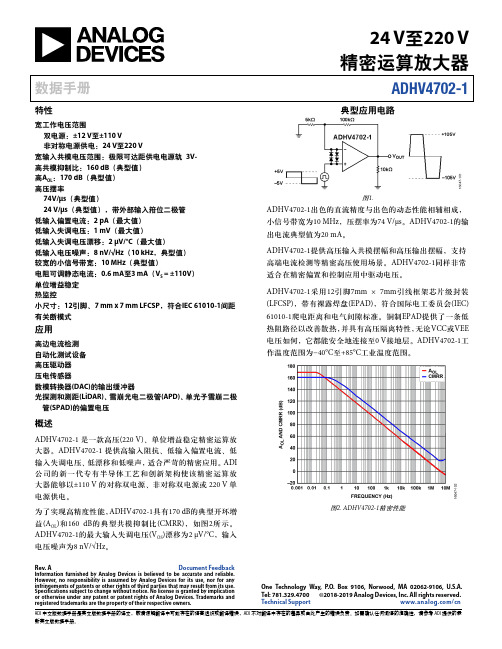

如需确认任何词语的准确性,请参考ADI 提供的最24 V至220 V 精密运算放大器数据手册ADHV4702-1特性宽工作电压范围双电源:±12 V 至±110 V非对称电源供电:24 V 至220 V宽输入共模电压范围:极限可达距供电电源轨 3V- 高共模抑制比:160 dB (典型值) 高A OL :170 dB (典型值) 高压摆率74V/μs (典型值)24 V/µs (典型值),带外部输入箝位二极管 低输入偏置电流:2 pA (最大值) 低输入失调电压:1 mV (最大值)低输入失调电压漂移:2 µV/°C (最大值)低输入电压噪声:8 nV/√Hz (10 kHz ,典型值) 较宽的小信号带宽:10 MHz (典型值)电阻可调静态电流:0.6 mA 至3 mA (V S = ±110V ) 单位增益稳定 热监控小尺寸:12引脚、7 mm x 7 mm LFCSP ,符合IEC 61010-1间距 有关断模式应用高边电流检测自动化测试设备 高压驱动器 压电传感器数模转换器(DAC)的输出缓冲器 光探测和测距(LiDAR)、雪崩光电二极管(APD)、单光子雪崩二极管(SPAD)的偏置电压概述ADHV4702-1是一款高压(220 V)、单位增益稳定精密运算放大器。

运放电路PCB设计技巧

运放电路PCB设计技巧虽然这里主要针对与高速运算放大器有关的电路,但是这里所讨论的问题和方法对用于大多数其它高速模拟电路的布线是普遍适用的。

当运算放大器工作在很高的射频(RF)频段时,电路的性能很大程度上取决于PCB布线。

“图纸”上看起来很好的高性能电路设计,如果由于布线时粗心马虎受到影响,最后只能得到普通的性能。

在整个布线过程中预先考虑并注意重要的细节会有助于确保预期的电路性能。

原理图尽管优良的原理图不能保证好的布线,但是好的布线开始于优良的原理图。

在绘制原理图时要深思熟虑,并且必须考虑整个电路的信号流向。

如果在原理图中从左到右具有正常稳定的信号流,那么在PCB上也应具有同样好的信号流。

在原理图上尽可能多给出有用的信息。

因为有时候电路设计工程师不在,客户会要求我们帮助解决电路的问题,从事此工作的设计师、技术员和工程师都会非常感激,也包括我们。

除了普通的参考标识符、功耗和误差容限外,原理图中还应该给出哪些信息呢?下面给出一些建议,可以将普通的原理图变成一流的原理图。

加入波形、有关外壳的机械信息、印制线长度、空白区;标明哪些元件需要置于PCB上面;给出调整信息、元件取值范围、散热信息、控制阻抗印制线、注释、扼要的电路动作描述……(以及其它)。

谁都别信如果不是你自己设计布线,一定要留出充裕的时间仔细检查布线人的设计。

在这点上很小的预防抵得上一百倍的补救。

不要指望布线的人能理解你的想法。

在布线设计过程的初期你的意见和指导是最重要的。

你能提供的信息越多,并且整个布线过程中你介入的越多,结果得到的PCB就会越好。

给布线设计工程师设置一个暂定的完成点——按照你想要的布线进展报告快速检查。

这种“闭合环路”方法可以防止布线误入歧途,从而将返工的可能性降至最低。

需要给布线工程师的指示包括:电路功能的简短描述,标明输入和输出位置的PCB略图,PCB层叠信息(例如,板子有多厚,有多少层,各信号层和接地平面的详细信息——功耗、地线、模拟信号、数字信号和RF信号);各层需要那些信号;要求重要元件的放置位置;旁路元件的确切位置;哪些印制线很重要;哪些线路需要控制阻抗印制线;哪些线路需要匹配长度;元件的尺寸;哪些印制线需要彼此远离(或靠近);哪些线路需要彼此远离(或靠近);哪些元器件需要彼此远离(或靠近);哪些元器件要放在PCB的上面,哪些放在下面。

穿越电流测量的无人区——pA等级电流测量

从毫安到微安再到皮安,随着电子技术的发展,以及市场对于低功耗的需求,电子设备的电流水平有往小发展的趋势,比如手机电池待机电流(10−3 A )、光电二极管暗电流(10−12 A )、OLED 的像素电流(10−12 A )等。

而如何精确测量出微弱电流,则成了一道避不开的难题。

为穿过这片“无人区”,测量出pA 等级的电流,我们必须踏入小数点后15位(fA 等级)的世界。

然而,这片了无人烟的区域并不是那么好踏足,路上的荆棘羁绊是难免的,需克服重重挑战才能成功到达终点。

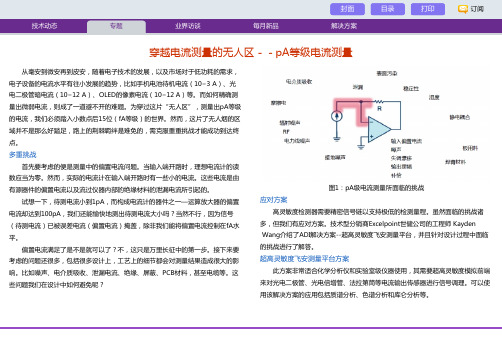

多重挑战首先要考虑的便是测量中的偏置电流问题。

当输入端开路时,理想电流计的读数应当为零。

然而,实际的电流计在输入端开路时有一些小的电流。

这些电流是由有源器件的偏置电流以及流过仪器内部的绝缘材料的泄漏电流所引起的。

试想一下,待测电流小到1pA ,而构成电流计的器件之一—运算放大器的偏置电流却达到100pA ,我们还能愉快地测出待测电流大小吗?当然不行,因为信号(待测电流)已被误差电流(偏置电流)掩盖,除非我们能将偏置电流控制在fA 水平。

偏置电流满足了是不是就可以了?不,这只是万里长征中的第一步。

接下来要考虑的问题还很多,包括很多设计上,工艺上的细节都会对测量结果造成很大的影响。

比如噪声、电介质吸收、泄漏电流、绝缘、屏蔽、PCB 材料,甚至电缆等。

这些问题我们在设计中如何避免呢?图1:pA 级电流测量所面临的挑战应对方案高灵敏度检测器需要精密信号链以支持极低的检测量程。

虽然面临的挑战诸多,但我们有应对方案。

技术型分销商Excelpoint 世健公司的工程师 Kayden Wang 介绍了ADI 解决方案--超高灵敏度飞安测量平台,并且针对设计过程中面临的挑战进行了解答。

超高灵敏度飞安测量平台方案此方案非常适合化学分析仪和实验室级仪器使用,其需要超高灵敏度模拟前端来对光电二极管、光电倍增管、法拉第筒等电流输出传感器进行信号调理。

可以使用该解决方案的应用包括质谱分析、色谱分析和库仑分析等。

放大器的精度和稳定性

电路结构建议采用典型电路形式和厂商提供的电路,许多电路结构都是经过很多工程师们反复实验和验证过的。

采用OP构成的放大器电路的精度主要与外部元器件参数有关,例如放大倍数与外接的电阻有关。

解决放大器的稳定性就比较复杂了,涉及到放大器的电路结构、PCB布局、电源供给、以及放大器所在的系统环境等等、等等。

一些建议如下:与分立器件相比,现代集成运算放大器(op amp)和仪表放大器(in-amp)为设计工程师带来了许多好处。

虽然提供了许多巧妙、有用并且吸引人的电路。

往往都是这样,由于仓促地组装电路而会忽视了一些非常基本的问题,从而导致电路不能实现预期功能——或者可能根本不工作放大器电路设计:如何避免常见问题。

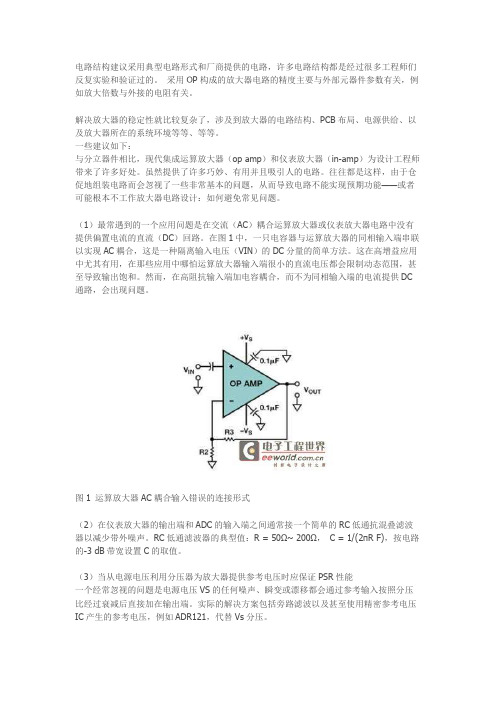

(1)最常遇到的一个应用问题是在交流(AC)耦合运算放大器或仪表放大器电路中没有提供偏置电流的直流(DC)回路。

在图1中,一只电容器与运算放大器的同相输入端串联以实现AC耦合,这是一种隔离输入电压(VIN)的DC分量的简单方法。

这在高增益应用中尤其有用,在那些应用中哪怕运算放大器输入端很小的直流电压都会限制动态范围,甚至导致输出饱和。

然而,在高阻抗输入端加电容耦合,而不为同相输入端的电流提供DC通路,会出现问题。

图1 运算放大器AC耦合输入错误的连接形式(2)在仪表放大器的输出端和ADC的输入端之间通常接一个简单的RC低通抗混叠滤波器以减少带外噪声。

RC低通滤波器的典型值:R = 50Ω~ 200Ω,C = 1/(2πR F),按电路的-3 dB带宽设置C的取值。

(3)当从电源电压利用分压器为放大器提供参考电压时应保证PSR性能一个经常忽视的问题是电源电压VS的任何噪声、瞬变或漂移都会通过参考输入按照分压比经过衰减后直接加在输出端。

实际的解决方案包括旁路滤波以及甚至使用精密参考电压IC 产生的参考电压,例如ADR121,代替Vs分压。

当设计带有仪表放大器和运算放大器的电路时,这方面的考虑很重要。

电源电压抑制技术用来隔离放大器免受其电源电压中的交流声、噪声和任何瞬态电压变化的影响。

运算放大器设计总结.概要

一.运算放大器的基本参数1.开环电压增益A OL不带负反馈的状态下,运算放大器对直流信号的放大倍数。

电压反馈运算放大器采用电压输入/电压输出方式工作,其开环增益为无量纲比,所以不需要单位。

但是,数值较小时,为方便起见,数据手册会以V/mV或V/μV代替V/V表示增益,电压增益也可以dB形式表示,换算关系为dB = 20×logAVOL。

因此,1V/μV的开环增益相当于120 dB,以此类推。

该参数与频率密切相关,随着频率的增加而减小,相位也会发生偏移。

对于反向比例放大电路,只有当AOL>>R+Rf时,Vo=-Rf/RVi才能够成立。

2.单位增益带宽B1(Gain-Bandwidth Product)开环电压增益大于等于1(0dB)时的那个频率范围,以Hz为单位。

它将告诉你将小信号(~±100mV)送入运放并且不失真的最高频率。

在滤波器设计电路中,假定运放滤波器增益为1V/V,则单位增益带宽大于等于滤波器截止频率f cut-off×100。

3.共模抑制比CMRR差分电压放大倍数与共模电压放大倍数之比,CMRR=|Ad/Ac|。

共模输入电压会影响到输入差分对的偏置点。

由于输入电路内部固有的不匹配,偏置点的改变会引起失调电压改变,进而引起输出电压改变。

其实际的计算方法是失调电压变化量比共模电压变化量,一般来说CMRR=ΔVos/ΔVcom,TI及越来越多的公司将其定义为CMRR=ΔVcom/ΔVos。

在datasheet中该参数一般为直流参数,随着频率的增加而降低。

4.输入偏置电流Ibias输入偏置电流被定义为:运放的输入为规定电位时,流入两个输入端的电流平均值。

记为IB。

为了运放能正常的工作,运放都需要一定的偏置电流。

IB=(IN+IP)/2。

当信号源阻抗很高时,就必须关注输入偏流,因为如果运放有很大的输入偏流,就会对信号源构成负载,因而会看到一个比预想要低的信号源输出电压,如果信号源阻抗很高,那么最好使用一个以CMOS或者JFET作为输入级的运放,也可以采用降低信号源输出阻抗的方法,就是使用一个缓冲器,然后用缓冲器来驱动具有很大输入偏流的运放。

奥伟斯科技为您提供3PEAK零漂运算放大器TP5591_TP5592_T5594

TP5591、TP5592、TP5594放大器是单,双和四斩波稳定的零漂移运算放大器,针对1.8V至5.5V或±0.9V至±2.75V的单电源或双电源供电进行了优化。

TP559x运算放大器具有非常低的输入失调电压和低噪声,且1 / f噪声角低至0.1Hz。

TP559x放大器设计为具有低失调电压和失调温度漂移,宽增益带宽以及轨至轨输入和输出摆幅,同时将功耗降至最低。

TP559x运算放大器可提供低失调电压(最大20μV)和接近具有出色的CMRR和PSRR,可在时间和温度范围内实现零漂移.TP5591(单个版本)采用SC70-5,SOT23-5和SO-8封装。

TP5592(双版本)以MSOP-8,SO-8封装提供。

TP5594(四版本)以TSSOP-14和SO-14封装提供。

所有版本的额定工作温度范围均为-40°C至125°C。

特点:低失调电压:20μV(最大值)零漂:0.01 µV /°C超低噪声:-输入噪声电压:1 kHz时为17 nV /√Hz-0.1Hz至10Hz噪声电压:370 nVPP-1 / f噪声角低至0.1Hz3.3 MHz带宽,2.5 V /μs压摆率低电源电流:每个放大器470μA单电源工作电压低至+ 1.8V低输入偏置电流:60 pA高增益,127 dB高CMRR和PSRR过载恢复时间:35 µs轨到轨输入和输出摆幅–40°C至125°C的工作范围应用:医疗仪器温度测量精密电流感应精密低漂移,低频ADC驱动器过程控制系统精密基准电压缓冲器Pin Configuration (Top View)Order InformationModel Name Order Number Package Transport Media, QuantityMarking InformationTP5591-TR SOT23-5 Tape and Reel, 3,000 E91T TP5591 TP5591-CR SC70-5 Tape and Reel, 3,000 91C TP5591-SR SOIC-8 Tape and Reel, 4,000 TP5591TP5591U TP5591U-CR SC70-5 Tape and Reel, 3,000 91V TP5591U-TR SOT23-5 Tape and Reel, 3,000 E91UTP5592 TP5592-SR SOIC-8 Tape and Reel, 4,000 TP5592 TP5592-VR MSOP-8 Tape and Reel, 3,000 TP5592TP5594 TP5594-SR SOIC-14 Tape and Reel, 2,500 TP5594 TP5594-TR TSSOP-14 Tape and Reel, 3,000 TP5594Absolute Maximum RatingsNote 1Supply Voltage: .....................................................6V Current at Supply Pins……………............... ±50mAInput Voltage: ....................... ……V–– 0.1 to V+ + 0.1 Operating Temperature Range.......–40°C to 125°CInput Current: +IN, –IN Note2........................... ±20mA Maximum Junction Temperature................... 150°C Output Current: OUT...................................... ±60mA Storage Temperature Range.......... –65°C to 150°COutput Short-Circuit Duration Note3…....... Indefinite Lead Temperature (Soldering, 10 sec) ......... 260°CNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure toany Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: The inputs are protected by ESD protection diodes to each power supply. If the input extends more than 500mV beyond the power supply, the input current should be limited to less than 10mA.Note 3: A heat sink may be required to keep the junction temperature below the absolute maximum. This depends on the power supply voltage and how many amplifiers are shorted. Thermal resistance varies with the amount of PC board metal connected tothe package. The specified values are for short traces connected to the leads.ESD, Electrostatic Discharge ProtectionSymbol Parameter Condition Minimum Level Unit HBM Human Body Model ESD ANSI/ESDA/JEDEC JS-001 7 kV CDM Charged Device Model ESD ANSI/ESDA/JEDEC JS-002 2Electrical CharacteristicsAt T A = 27°C, V S = 5V, R L = 10kΩ, V CM = V DD/2, unless otherwise noted.SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS V S Supply voltage range 1.8 5.5 VI Q Quiescent current per amplifier TP5591 1200 1400 μA TP5592/4 550 950 μAV OS Input offset voltage V CM = 0.05V to 4.95V ±5 ±20 μV V S = 1.8V, V CM = 0.9V ±5 ±20 μVdV OS/dT vs. Temperature 0.01 μV/°C PSRR vs power supply Vs = 3V to 5V 95 130 dBV n Input voltage noise, f=0.01Hz to 1Hz 0.1 μV pp Input voltage noise, f=0.1Hz to 10Hz 0.37 μV ppe n Input voltage noise density, f=1kHz 17 nV/√HzC IN Input capacitor differential 3 pF Input capacitor common-mode 2 pFI B Input current ±60 ±200 pA Over temperature ±800 pAI OS Input offset current ±100 ±400 pAV CM Common-mode voltage range (V-)-0.1 (V+)+0.1 V CMRR Common-mode rejection ratio V CM = 0.5V to 4.5V 110 127 dB Output voltage swing from rail R L=10kΩ 5 25 mV I SC Short-circuit current ±60 mA GBWP Unity gain bandwidth C L=100pF 3.3 MHz SR Slew rate G=+1, C L=100pF 2.5 V/μs t OR Overload recovery time G=-10 35 μs t S Settling time to 0.01% C L=100pF 20 μsA VOL Open-loop voltage gain (V-)+100mV<V O<(V+)-100mV,R L = 100kΩ100 130 dB SOT23-5 200MSOP-8 210θJA Thermal resistance junction toambientSO-8 158SC70-5 250SO-14 83°C/WTSSOP-14 100Typical Performance CharacteristicsQuiesent C urrent v s TemperatureVoltage Noise Spectral Density vs Frequency 100010090080070060010500400300200100-50 -25 0 25 50 75 100 125 150 10.01 0.1 1 10 100 1k 10kTemperature(°C)Frequency (Hz)CMRR vs FREQUENCY OPEN-LOOPGAIN vs FREQUENCY120 100 140100908012080 70 1006060508040406020 30 40201020-20 010 100 1k 10k 100k 1M 10MFrequency(Hz) 1 10 100 1k 10k 100k 1MFrequency(Hz) Small-Scale Step Response Positive Over-Voltage RecoveryG=+1R L=10KΩInputOutputTime (5μs/div) Time (50μs/div)Negative Over-Voltage Recovery Large-Scale Step ResponseG=+1R L=10KΩInputOutputTime (50μs/div)Time (10μs/div)Offset Voltage Distribution18161412108642Offset Voltage (μV)Typical ApplicationsSingle Supply, High Gain Amplifier, A V = 10,000 V/V-TP5591+Thermistor Measurement-TP5591+Pin Functions-IN:放大器的反相输入。

运放的保护电路

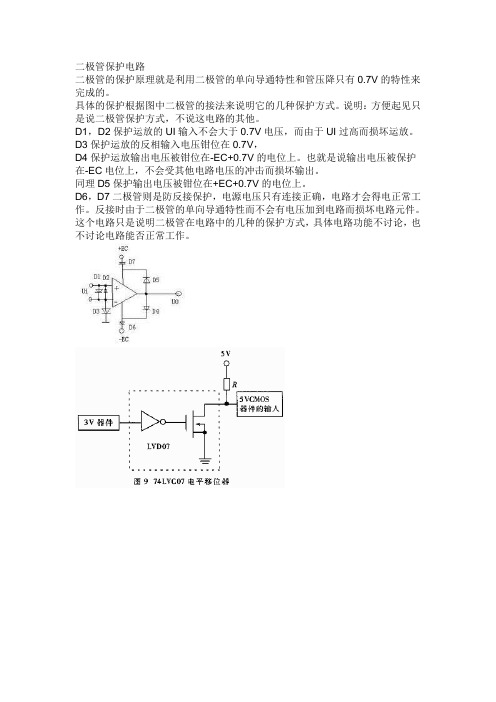

二极管保护电路二极管的保护原理就是利用二极管的单向导通特性和管压降只有0.7V的特性来完成的。

具体的保护根据图中二极管的接法来说明它的几种保护方式。

说明:方便起见只是说二极管保护方式,不说这电路的其他。

D1,D2保护运放的UI输入不会大于0.7V电压,而由于UI过高而损坏运放。

D3保护运放的反相输入电压钳位在0.7V,D4保护运放输出电压被钳位在-EC+0.7V的电位上。

也就是说输出电压被保护在-EC电位上,不会受其他电路电压的冲击而损坏输出。

同理D5保护输出电压被钳位在+EC+0.7V的电位上。

D6,D7二极管则是防反接保护,电源电压只有连接正确,电路才会得电正常工作。

反接时由于二极管的单向导通特性而不会有电压加到电路而损坏电路元件。

这个电路只是说明二极管在电路中的几种的保护方式,具体电路功能不讨论,也不讨论电路能否正常工作。

图1所示为集成运算放大器供电过压保护电路。

当运放电路块的实际供电电压较高、或供电电源产生突变时,采用上述电路后保护运放电路块,使其不至于烧坏。

图中,DW1、DW2可取稳压值略低于集成运放最大工作电源电压、而大于实际工作电源电压E+、E-的稳压二极管。

BG1、BG2接成恒流源形式,并且选用饱和漏源电流略大于集成运放电路工作电流的场效应管。

C1、C2为滤波电容,可取10~20uF。

当电源电压工作正常时,DW11、DW2不工作,BG1、BG2管呈现低阻抗,不影响集成运放电路正常工作。

当电源;电压突然增高时,DW1 、DW2工作,使集成过放电路工作电压不会超过DW1、DW2的稳压值。

BG1、BG2管这时呈现高阻抗,从而限制了DW1、DW2上流过的电流,使DW1、DW2也不至于烧坏。

由于恒流源具有恒流作用,因此在运放电路输出端短路时。

电路也有一定的保护作用。

当工作电源电压E+、E-不算高、且电源电压较稳定时,可用两只阻值为100Ω的电阻代替图中的场效应管车载逆变电源设计(过压保护电路) (2011-10-26 17:33)分类:车载逆变电源设计输入过压保护电路电路结构如图7,由DZ1、电阻R1和电阻R2、电容C1、二极管VD1组成。

TLC2652高精度放大器

TLC2652高精度放大器一、引言二、在微弱信号的测量中,常常需要放大微伏级的电信号。

这时,普通的运算放大器已无法使用了,因为它们的输入失调电压一般在数百微伏以上,而失调电压的温度系数在零点几微伏以上。

固然输入失调电压可以被调零,但其漂移则是难以消除的。

德州仪器公司生产的斩波稳零型运算放大器提供了一种解决微信号放大问题的廉价方案。

TLC2652和TLC2652A是德州仪器公司使用先进的LinCMOS工艺生产的高精度斩波稳零运算放大器。

斩波稳零的工作方式使TLC2652具有优异的直流特性,失调电压及其漂移、共模电压、低频噪声、电源电压变化等对运算放大器的影响被降低到了最小,TLC2652非常适合用于微信号的放大。

二、TLC2652的内部结构图一、TLC2652的功能框图下面对TLC2652的内部功能单元作一简单介绍:1、主放大器。

它与一般的运算放大器不同之处在于,它有三个输入端。

除引出芯片外部的同相和反相输入端外,其在芯片内部还有一个用于校零的同相输入端。

2、校零放大器。

它也有三个输入端,但与主放大器相反,在芯片内部的输入端是反相输入端。

3、时钟和开关电路。

内部时钟产生时钟信号,控制各开关按一定的时序闭合与断开。

在14和20引脚的芯片中时钟信号还可从外部引入。

4、补偿网络。

它使电路在较宽的频带内有平坦的响应。

在TLC2652中,电路的高频响应主要由主放大器决定。

5、箝位电路(CLAMP)。

它实际上是一个当输出与电源电压相差接近1V时动作的开关,把CLAMP与运放的反相输入端短接,则其引入的深度负反馈可使电路在过载时的增益大大下降以防止饱和。

它可以加速电路在过载后的恢复。

三、斩波稳零的工作原理图二、TLC2652的简化框图TLC2652芯片上的控制逻辑产生两个主要的时钟周期:校零周期和放大周期。

主放大器一直与电路的输入端和输出端相连,而校零放大器则在两个周期内分别对自己和主放大器校零。

在校零周期内,开关A闭合,使校零放大器的两个输入端短路,通过自身的反馈,校零放大器的失调电压被减到最小。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关于运放保护环

在弱信号放大的情况下,尤其是对弱电流放大的情况下,有可能需要在运放的输入端加一个保护环(guard ring,或称屏蔽环),目的是抑制漏电流对运放输入端造成影响。

先说漏电流的形成。

所谓漏电流,也是电流,它的形成也不外乎电压和电阻,这里的电压是比较复杂,包括运放供电的电压,也包括信号的电压和外界干扰的电压。

这里的电阻是漏电阻,是指两个网络节点在理想情况下应该是无穷大的实际电阻,漏电阻可能在几百兆或上百G欧姆范围。

影响漏电阻的因素有PCB的材料、劣质的PCB走线层及PCB的污染,PCB 的污染包括电路板表层的油污、空气潮湿、助焊剂和电路板清洗剂等,这些物质的存在会形成漏电流路径。

比如说,5V的供电电源处于输入引脚处之间的电压是5V,由于电路板污染的存在,它们之间的漏电阻为100G欧,那么形成的漏电阻就是50pA,这个数值可能比高精度运放的偏置电流大几十倍,这就是为什么要抑制漏电流的原因。

对于直流来说,影响可能还能校正过来,但外界的干扰或被测信号的影响来说,那可能是致命的,无法校正的。

漏电流的抑制方法。

这个方法就是加保护环,保护环的添加有几个注意点及其原因:

一是保护环与被保护对象的电位要相等或接近,目的是减小压差,在保护环内电位基本相等,从而减小漏电流,这是针对环内来说的。

二是保护环要接到尽量低的阻抗点上,即被低阻抗的源所驱动。

这一点是针对环外来说的,如果外界对保护环有漏电流,那么电流通过低阻抗源可以更容易导走,而不至于过多地影响环的电位。

如下图所示,它是AD公司推荐的两种接法,前者是反相放大形式的接法,由于同相端接地,它的阻抗是0,所以保护环绕反相端保护,而接到同相端;后者是同相放大形式的接法,同相端的阻抗是很大的,所以相比之下,把保护环保护同相端而接到反相端更好。

后面的图是保护环的画法。

下面的图是LT公司的接法,我觉得用这种跨电阻的方式来留出保护环空间的方法挺不错的,但还没想到充分的理由。

三是要尽量把被保护对象包起来,包括上下左右各个方向,建议用多层板。

有人说,芯片引脚下面有没有必要也铺一层铜,连到保护环上我个人觉得如果有条件还是要尽量这样做。

因为,垂直运放引脚的焊盘方向,它的面积最大,从下面(顶层下面的中间层)过来的信号会更容易通过电路板材料(如X4R等介质材料)像焊盘注入漏电流。

当然,中间层不存在污染问题,如果相比顶层的污染来说,这些微不足道,那也可以不加,毕竟多层板会增加成本。