cd4046

锁相环4046

cD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V -18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz 下功耗仅为600μW,属微功耗器件。

编辑本段功能CD4046的引脚排列,采用16脚双列直插式,各管脚功能:1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

编辑本段图形简介图3图3是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。

当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图4所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。

从图中还可知,fout不一定是对称波形。

对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。

它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

锁相环的CD4046应用

一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

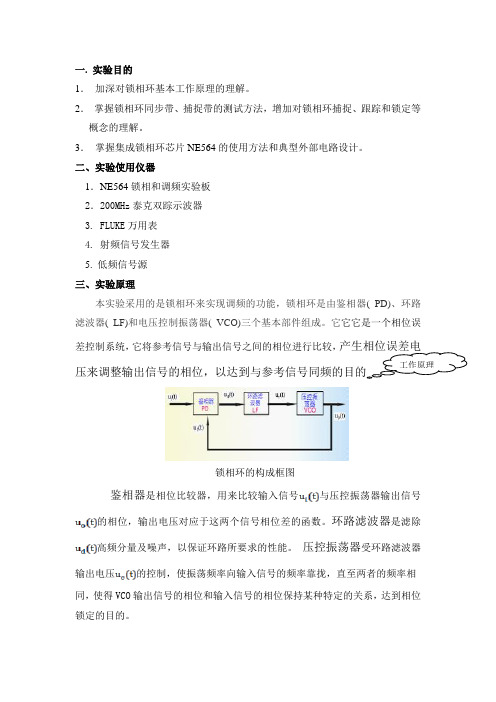

二、实验使用仪器1.NE564锁相和调频实验板2.200MHz泰克双踪示波器3. FLUKE万用表4. 射频信号发生器5. 低频信号源三、实验原理本实验采用的是锁相环来实现调频的功能,锁相环是由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

它它它是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电工作原理压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环的构成框图鉴相器是相位比较器,用来比较输入信号与压控振荡器输出信号的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的。

*判断环路是否锁定的方法在有双踪示波器的情况下,开始时环路处于失锁状态,加大输入信号频率,用双踪示波器观察压控振荡器的输出信号和环路的输入信号,当两个信号由不同步变成同步,且时,表示环路已经进入锁定状态。

锁相调频电路在普通的直接调频电路中,振荡器的中心频率稳定度较差,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

锁相调频原理框图如下图所示锁相调频原理图 正如上面锁相调频原理图所示,实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外。

使压控振荡器的中心频率锁定在稳定度很高的晶振频率上,而随着输入调制信号的变化,振荡频率可以发生很大偏移。

这种锁相环路称载波跟踪型PLL ,本实验中使用的锁相环是NE564。

NE564内部压控振荡器的最高工作频率是50MHz ,从图10-5的逻辑框图中可以看到,NE564的内部包含一个限幅放大器,对外部的输入信号进行限幅放大,抑制寄生调幅,内部还包含压控振荡器和相位比较器。

锁相环的CD4046应用

一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

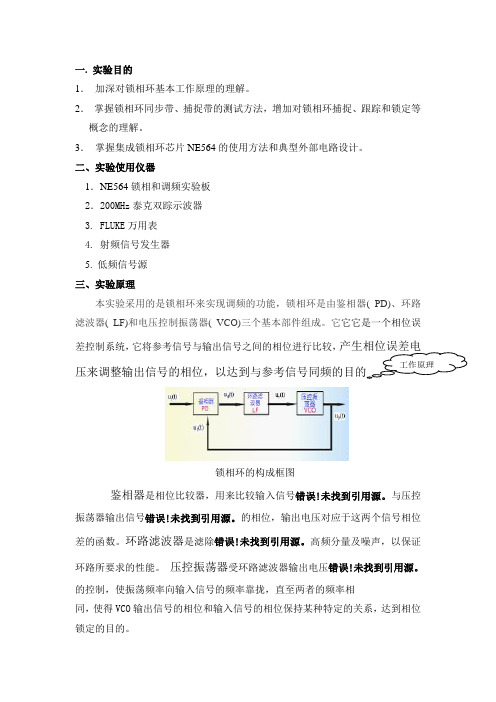

二、实验使用仪器1.NE564锁相和调频实验板2.200MHz泰克双踪示波器3. FLUKE万用表4. 射频信号发生器5. 低频信号源三、实验原理本实验采用的是锁相环来实现调频的功能,锁相环是由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

它它它是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电工作原理压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环的构成框图鉴相器是相位比较器,用来比较输入信号错误!未找到引用源。

与压控振荡器输出信号错误!未找到引用源。

的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除错误!未找到引用源。

高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压错误!未找到引用源。

的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的。

*判断环路是否锁定的方法在有双踪示波器的情况下,开始时环路处于失锁状态,加大输入信号频率,用双踪示波器观察压控振荡器的输出信号和环路的输入信号,当两个信号由不同步变成同步,且错误!未找到引用源。

时,表示环路已经进入锁定状态。

锁相调频电路在普通的直接调频电路中,振荡器的中心频率稳定度较差,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

锁相调频原理框图如下图所示锁相调频原理图 正如上面锁相调频原理图所示,实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外。

使压控振荡器的中心频率锁定在稳定度很高的晶振频率上,而随着输入调制信号的变化,振荡频率可以发生很大偏移。

锁相环CD4046 原理及应用

锁相环 CD4046 原理及应用锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示。

图1压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小CO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:图2•1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

•2脚相位比较器Ⅰ的输出端。

•3脚比较信号输入端。

•4脚压控振荡器输出端。

•5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

CD4046[1]

![CD4046[1]](https://img.taocdn.com/s3/m/ca55a38a680203d8ce2f24b0.png)

CD4046CD4046引脚图锁相环芯片CD4046原理及特性过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:图3是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。

当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图4所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。

从图中还可知,fout不一定是对称波形。

对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。

它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。

在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。

CD4046锁相环

锁相环CD4046应用介绍:频率相等,相位同步也就是相位相差一个固定值锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(V CO)。

低通滤波器三部分组成,如图1所示。

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

CD4046中文资料_数据手册_参数

CD4046B型号采用16铅密封双线陶瓷封装(F3Asuffix)、16铅双线塑料封装(Esuffix)、16铅小外径封装(nsr后缀)和16铅薄收缩小外径封装 (PW和PWR后缀)(1)营销状态值定义如下:ACTIVE:推荐用于新设计的产品设备。LIFEBUY:德州仪器公司宣布该设备将停产,终身购买 期已经生效。NRND:不推荐用于新设计。该设备正在生产中,以支持现有客户,但TI不建议在新设计中使用该部件。预览:设备已宣 布,但尚未投产。样品可能有也可能没有。过时的:TI已经停止生产该设备。(2)Eco Plan—可能目前不可用—请查看以获得最新的可用 信息和额外的产品内容详细信息。没有:还没有可用的铅(Pb-Free)。无铅(RoHS): TI的术语“无铅”或“无铅”是指与所有6种物质的现 行RoHS要求兼容的半导体产品,包括在均质材料中铅的重量不超过0.1%的要求。CD4046设计用于高温焊接的无钛pb产品适用于特定 的无铅工艺。环保(RoHS &没有某人/ Br): TI定义“绿色”意味着“Pb-Free”,此外,使用包装材料,不含卤素,包括溴(Br)或锑(某人)总数的 0.1%以上产品的重量。(3)实验室,峰值温度。湿度敏感性级别评级根据JEDECindustry标准分类和soldertemperature峰值。重要信息和免 责声明:本页所提供的信息代表德州仪器自提供之日起的知识和信念。TI的知识和信念基于第三方提供的信息,对于这些信息的准确性 不作任何陈述或保证。目前正在努力更好地整合来自第三方的信息。TI已采取并将继续采取合理措施,提供具有代表性和准确的信 息,但可能未对来料和化学品进行破坏性测试或化学分析。TI和TI供应商认为某些信息是专有的,因此CAS号码和其他有限的信息可 能无法发布。在任何情况下,TI因该等信息而产生的责任都不应超过.CD4046客户在本文件中每年销售的TI部件的采购总价无铅 (RoHS): TI的术语“无铅”或“无铅”是指与当前所有6种物质的RoHS要求兼容的半导体产品,包括在均质材料中铅的重量不超过0.1% 的要求。设计用于高温焊接的无钛pb产品适用于特定的无铅工艺。无铅(免RoHS):该组件具有免RoHS的任何1)基于铅的倒装芯片焊料 凸点之间使用的模具和封装,或2)基于铅的模具胶粘剂之间使用的模具和铅框架。否则,该CD4046组件被认为是如上定义的无pb (RoHS兼容)的。绿色(RoHS & no Sb/Br):TI定义“绿色”意味着Pb-Free (RoHS兼容),和自由的溴(Br)和(某人)锑阻燃剂(Br或某人不超过 0.1% weightin均质材料)(3)实验室,峰值温度。湿度敏感性级别评级根据电平行业标准分类,和峰值焊接温度。(4)CD4046可能有额外的标 记,与标志,许多跟踪代码的信息,(5)多个设备标记将在括号内。只有一个设备标记包含在括号中,并以“~”分隔,将出现在一个设备 上。如果一条线是缩进的,那么它是前一条线的延续,这两条线代表了该设备的整个设备标记。Finish选项由一条垂直的直线分隔。如 果结束值超过最大列宽,则铅/球结束值可以绕成两行。重要信息和免责声明:本页所提供的信息代表德州仪器自提供之日起的知识和 信念。TI的知识和信念基于第三方提供的信息,对于这些信息的准确性不作任何陈述或保证。目前正在努力更好地整合来自第三方的 信息。TI已经并将继续采取合理措施,提供具有代表性和准确的信息,但可能没有对来料和化学品进行破坏性测试或化学分析。TI和 TI供应商认为某些信息是专有的,因此CAS编号和其他有限的信息可能无法发布。在任何情况下,TI因该等信息而产生的责任,都不 应超过TI在本文件中每年向客户出售的TI务,只售 原装现货库存,万联芯城电子元器件全国供应,专为终端生产, 研发企业提供现货物料,价格优势明显,BOM配单采购可节省 逐个搜索购买环节,只需提交BOM物料清单,商城即可为您报 价,万联芯城完善的供应链体系能够满足多种报价需求,为客 户节省成本,点击进入万联芯城。

cd4046原理

cd4046原理CD4046是一种常用的集成电路,用于频率锁定环路和相位比较器。

它由一个VCO(Voltage Controlled Oscillator)和两个相位比较器组成。

我们来了解一下CD4046的基本原理。

CD4046是一种锁相环(PLL)电路,它可将输入信号锁定在特定的频率上。

PLL是一种负反馈控制系统,它通过调整输出信号的相位和频率来与输入信号保持一致。

CD4046的输入信号经过一个相位比较器与VCO的输出信号进行比较,然后通过一个滤波器对比较结果进行平滑处理,最后输出给VCO进行频率调整。

CD4046中的相位比较器有两个,分别为相位比较器1和相位比较器2。

相位比较器1用于锁定输入信号的相位,相位比较器2用于锁定输入信号的频率。

相位比较器1的输出信号经过一个低通滤波器来获得一个平均值,然后输入给VCO进行频率调整。

相位比较器2的输出信号则直接输入给VCO进行相位调整。

CD4046中的VCO是一个电压控制的振荡器,它的频率可以通过控制输入信号的电压来调整。

VCO的输出信号经过一个分频器后又反馈给相位比较器1和相位比较器2,形成一个闭环控制系统。

当输入信号的频率与VCO的输出频率不一致时,相位比较器1和相位比较器2会产生不同的输出信号,通过调整VCO的频率和相位,使得两个输入信号保持一致。

CD4046的频率锁定环路具有很多应用。

一种常见的应用是频率合成器,它可以将一个稳定的参考信号通过CD4046锁定在所需的频率上,用于无线电调谐器和通信系统中。

另一种应用是相位比较器,它可以用于数字通信系统中的时钟恢复和数据同步。

总结一下,CD4046是一种用于频率锁定环路和相位比较器的集成电路,它通过相位比较器和VCO的组合来实现输入信号的锁定。

CD4046广泛应用于无线电调谐器、通信系统和数字通信系统等领域。

通过对CD4046的深入了解,我们可以更好地理解和应用这一集成电路。

CD4046应用资料

CD4046中文资料锁相环CC4046为数字PLL,内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。

它具有电源电压范围宽、功耗低、输入阻抗高等优点,其工作频率达1MHz,内部VCO 产生50% 占空比的方波,输出电平可与TTL电平或CMOS 电平兼容。

同时,它还具有相位锁定状态指示功能。

信号输入端:允许输入0.1V左右的小信号或方波,经A1放大和整形,提供满足PD要求的方波。

PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率。

通常输入信噪比以及固有频差较小时采用PDI,输入信噪比较高或固有频差较大时,采用PDⅡ。

R1 、R2、C确定VCO 频率范围。

R1控制最高频率,R2控制最低频率。

R2=∞时,最低频率为零。

无输入信号时,PDⅡ将VCO调整到最低频率。

锁相环CD4046的一个重要功能是:内部压迫、控振荡器的输出信号从第4脚输出后引至第3脚输入,与从第14脚输入的外部基准频率信号和相位的比较。

当两者频率相同时同,压控振荡器的频率能自动调整,直到与基准频率相同。

CD4046引脚图DC Supply Voltage 直流供电电压(VDD) −0.5 to +18 VDC Input Voltage输入电压(VIN) −0.5 to VDD +0.5 VDC Storage Temperature Range储存温度范围(TS) −65℃ to +150℃Power Dissipation功耗(PD)Dual-In-Line 普通双列封装700 mWSmall Outline 小外形封装500 mW焊接温度(TL)(焊接10秒)260℃Recommended Operating Conditions 建议操作条件:DC Supply Voltage 直流供电电压(VDD) 3 to 15 VDC Input Voltage输入电压(VIN) 0 to VDD VDC Operating Temperature Range工作温度范围(TA) −55℃ to +125℃符号引脚号名称功能PH1114相位比较器输入端(基准信号输入),相位比较器输入信号,输入允许将0.1V左右的小信号或方波信号在内部放大并再经过整形电路后,输出至相位比较器。

cd4046构成的fsk调制解调电路

cd4046构成的fsk调制解调电路全文共四篇示例,供读者参考第一篇示例:CD4046是一种集成电路,常用于FSK调制和解调电路中。

FSK (Frequency Shift Keying)调制技术是一种数字调制技术,通过改变信号的频率来携带数字信息。

在通信系统中,FSK调制技术被广泛应用于数据传输和调频调制解调。

本文将详细介绍CD4046构成的FSK 调制解调电路的原理和应用。

一、CD4046简介CD4046是一种集成数字数字锁相环PLL(Phase Locked Loop)电路,由德州仪器公司生产。

它由一个相位比较器、一个VCO (Voltage Controlled Oscillator)和一个低通滤波器组成。

CD4046可以将输入信号的频率与VCO的频率进行比较,并自动调节VCO的频率,使得输入信号与VCO的频率同步。

这种锁相环的原理可以用于FSK调制和解调电路中。

二、FSK调制解调电路原理1. FSK调制原理:在FSK调制中,输入的数字信号被转换成两种不同频率的信号,并分别控制两个不同频率的载波信号。

这两种载波信号通过一个开关切换器,使得输出信号在两种频率之间切换,从而携带数字信息。

2. FSK解调原理:在FSK解调中,接收到的信号经过解调器解调,得到两种不同频率的信号。

这两种信号再经过一个比较器比较,得到解调后的数字信号。

CD4046通过其内部的相位比较器和VCO实现了FSK调制解调电路。

其电路连接如下:1. 输入信号经过一个低通滤波器,去除噪声和高频成分,然后输入到CD4046的相位比较器。

2. CD4046的VCO的频率由输入信号的频率控制,当输入信号的频率高于VCO的频率时,VCO的频率会增加;反之,当输入信号的频率低于VCO的频率时,VCO的频率会减小。

3. CD4046的输出信号通过一个比较器进行信号处理,得到FSK调制或解调后的数字信号。

1. 数据传输:FSK调制技术可以将数字信号转换成模拟信号进行传输,提高数据传输效率和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Block

Connection Diagrams

Dual-In-Line Package

TL F 5968 – 2

Top View Order Number CD4046B

TL F 5968 – 1

FIGURE 1

C1995 National Semiconductor Corporation

TL F 5968

RRD-B30M115 Printed in U S A

Absolute Maximum Ratings (Notes 1

2)

If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications DC Supply Voltage (VDD) Input Voltage (VIN) Storage Temperature Range (TS) Power Dissipation (PD) Dual-In-Line Small Outline Lead Temperature (TL) (Soldering 10 seconds)

Features

Y Y

Y Y

Y

Wide supply voltage range 3 0V to 18V Low dynamic 70 mW (typ ) at power consumption fo e 10 kHz VDD e 5V VCO frequency 1 3 MHz (typ ) at VDD e 10V Low frequency drift 0 06% C at VDD e 10V with temperature High VCO linearity 1% (typ )

b 0 51 b1 3 b3 4 b0 1

5 20 50 0 0 0 4 95 9 95 14 95 5 10 15 2 25 45 6 25 2 75 55 8 25 0 88 2 25 88

b 0 88 b 2 25 b8 8

35 350 900 0 05 0 05 0 05 4 95 9 95 14 95 15 30 40 35 70 11 0 0 36 09 24

b 0 36 b0 9 b2 4

185 650 1500 0 05 0 05 0 05

mA mA mA V V V V V V

VOH

VIL

15 30 40

V V V V V V mA mA mA mA mA mA

VIH

IOL

Low Level Output Current VDD e 5V VO e 0 4V (Note 4) VDD e 10V VO e 0 5V VDD e 15V VO e 1 5V High Level Output Current VDD e 5V VO e 4 6V (Note 4) VDD e 10V VO e 9 5V VDD e 15V VO e 13 5V Input Current All Inputs Except Signal Input VDD e 14V VIN e 0V VDD e 15V VIN e 15V Any Input (Note 3) fo e 10 kHz R1 e 1 MX R2 e % VCOIN e VDD 2 VDD e 5V VDD e 10V VDD e 15V

Units

Min Quiescent Device Current Pin 5 e VDD Pin 14 e VDD Pin 3 9 e VSS VDD e 5V VDD e 10V VDD e 15V Pin 5 e VDD Pin 14 e Open Pin 3 2 e VSS VDD e 5V VDD e 10V VDD e 15V VOL Low Level Output Voltage VDD e 5V VDD e 10V VDD e 15V High Level Output Voltage VDD e 5V VDD e 10V VDD e 15V Low Level Input Voltage Comparator and Signal In High Level Input Voltage Comparator and Signal In VDD e 5V VO e 0 5V or 4 5V VDD e 10V VO e 1V or 9V VDD e 15V VO e 1 5V or 13 5V VDD e 5V VO e 0 5V or 4 5V VDD e 10V VO e 1V or 9V VDD e 15V VO e 1 5V or 13 5V 35 70 11 0 0 64 16 42

b 0 64 b1 6 b4 2

Max

Min

Typ

MaxBiblioteka MinMax5 10 20

0 005 0 01 0 015

5 10 20

150 300 600

mA mA mA

45 450 1200 0 05 0 05 0 05 4 95 9 95 14 95 15 30 40 35 70 11 0 0 51 13 34

Applications

Y Y Y Y Y Y Y Y

FM demodulator and modulator Frequency synthesis and multiplication Frequency discrimination Data synchronization and conditioning Voltage-to-frequency conversion Tone decoding FSK modulation Motor speed control

IOH

IIN

b 10 b 5 b 0 1

b1 0

01

10b5

01

10 75

mA mA pF

CIN PT

Input Capacitance Total Power Dissipation

0 07 06 24

mW mW mW

2

DC Electrical Characteristics CD4046BC (Note 2)

CD4046BM CD4046BC Micropower Phase-Locked Loop

November 1995

CD4046BM CD4046BC Micropower Phase-Locked Loop

General Description

The CD4046B micropower phase-locked loop (PLL) consists of a low power linear voltage-controlled oscillator (VCO) a source follower a zener diode and two phase comparators The two phase comparators have a common signal input and a common comparator input The signal input can be directly coupled for a large voltage signal or capacitively coupled to the self-biasing amplifier at the signal input for a small voltage signal Phase comparator I an exclusive OR gate provides a digital error signal (phase comp I Out) and maintains 90 phase shifts at the VCO center frequency Between signal input and comparator input (both at 50% duty cycle) it may lock onto the signal input frequencies that are close to harmonics of the VCO center frequency Phase comparator II is an edge-controlled digital memory network It provides a digital error signal (phase comp II Out) and lock-in signal (phase pulses) to indicate a locked condition and maintains a 0 phase shift between signal input and comparator input The linear voltage-controlled oscillator (VCO) produces an output signal (VCO Out) whose frequency is determined by the voltage at the VCOIN input and the capacitor and resistors connected to pin C1A C1B R1 and R2 The source follower output of the VCOIN (demodulator Out) is used with an external resistor of 10 kX or more The INHIBIT input when high disables the VCO and source follower to minimize standby power consumption The zener diode is provided for power supply regulation if necessary