哈工大电大数字电子技术基础大作业

数字电子技术基础作业

《数字电子技术基础》作业第一部分:1.P17 思考题P29 思考题题1.3.3 题1.3.6 题1.3.7 题1.3.8P47 习题1.7 习题1.142.P37思考题题1.4.1 题1.4.2 题1.4.4P47 习题1.16 习题1.18第二部分:1.P54 思考题题2.1.2 题2.1.3 题2.1.4P71 思考题题2.2.1 题2.2.5 题2.2.7 题2.2.8P100 习题2.7 习题2.10 习题2.122.P85 思考题题2.4.3 题2.4.6 题2.4.10.P89 思考题题2.5.2P94 思考题题2.6.1 题2.6.3.P102 习题2.14 习题2.17 习题2.18第三部分:1.P112 思考题题3.1.1P116 思考题题3.2.1 题3.2.3P156 习题3.4 习题3.92.P145 思考题题3.4.3 题3.4.8 题3.4.10.P156 习题3.10 习题3.11第四部分:1.P166 思考题题4.1.1 题4.1.2 题4.1.3P169 思考题题4.2.2 题4.2.5P183 习题4.2 习题4.42.P175 思考题题4.3.1 题4.3.6 题4.3.7.P179 思考题题4.4.1 题4.4.3 题4.4.4P182思考题题4.5.2 题4.5.4P185 习题4.7 习题4.10第五部分:1.P191 思考题题5.1.2 题5.1.3 题5.1.4P197 思考题题5.2.1 题5.2.4P252 习题5.1 习题5.2 习题5.32.P211 思考题题5.3.3 题5.3.4 题5.3.5P226 思考题题5.4.1 题5.4.6 题5.4.7 题5.4.8P253习题5.6 习题5.11 习题5.133.P245 思考题题5.5.5 题5.5.8P257 思考题题5.6.1 题5.6.4P252 习题5.19 习题5.20第六部分:1.P155 思考题题3.5.3 题3.5.4 题3.5.5 题3.5.8P158 习题3.14 习题3.152.P261 思考题题6.1.1 题6.1.2 题6.1.3P269 思考题题6.2.2 题6.2.6 题6.2.8P275 习题6.63.P273 思考题题6.3.1 题6.3.3P290 思考题题7.2.1P298 思考题题7.3.1第七部分:1.P329 思考题题9.1.4 题9.1.5P339 思考题题9.2.1 题9.2.2 题9.2.3 题9.2.6 题9.2.8 P348 习题9.1 习题9.2 习题9.42.P346 思考题题9.3.1 题9.3.2 题9.3.3 题9.3.4P349 习题9.5 习题9.9第八部分:1.P303 思考题题8.1.1 题8.1.2 题8.1.4P307 思考题题8.2.2 题8.2.5P321 习题8.8 习题8.102.P313 思考题题8.3.2 题8.3.4P319 思考题题8.4.2 题8.4.3 题8.4.6。

数字电子技术基础课后习题及参考答案

《数字电子技术基础》课后习题及参考答案(总90页)-CAL-FENGHAI.-(YICAI)-Company One1-CAL-本页仅作为文档封面,使用请直接删除第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)21(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

《数字电子技术基础》课后习题及参考答案

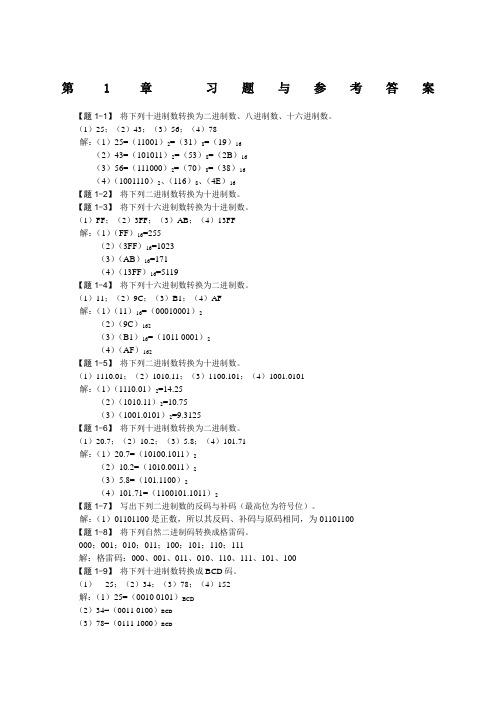

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)162(3)(B1)16=(1011 0001)2(4)(AF)162【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

哈尔滨工业大学数字电子技术基础课程设计报告:基于Verilog HDL语言的计数器设计

H a r b i n I n s t i t u t e o f T e c h n o l o g y

数字电子技术基础大作业报告

课程名称:数字电子技术基础

设计题目:V erilog HDL 计数器编程

院系:航天学院控制科学与工程系班级:0904102班

姓名:某某某

学号:xxxxxxxxxx

指导教师:王淑娟

设计时间:2011年12月

哈尔滨工业大学

Verilog HDL计数器编程

1设计任务

利用Verilog HDL设计一个模为学号后三位的计数器,设计要求:

1)编写源程序;

2)给出仿真电路图和仿真波形图。

2设计步骤

1.安装Quartus II软件并破解。

2.根据设计要求编写程序代码。

3.生成仿真电路图和波形如图。

3程序代码

4仿真电路图和波形图

如下图所示。

哈工大数字电路大作业

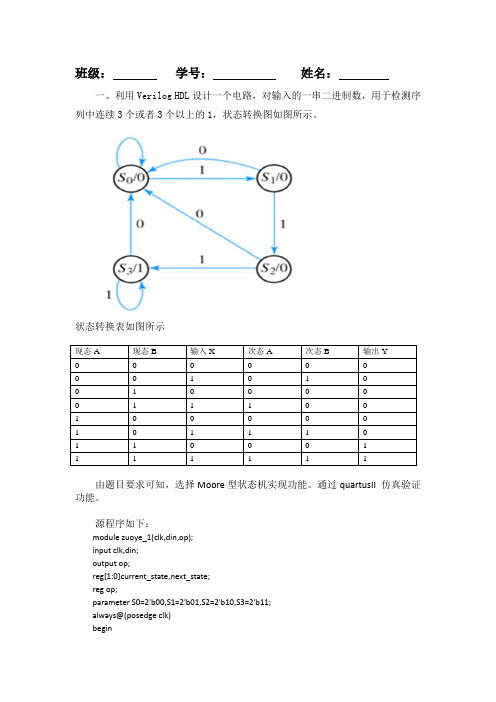

班级:学号:姓名:一、利用Verilog HDL设计一个电路,对输入的一串二进制数,用于检测序列中连续3个或者3个以上的1,状态转换图如图所示。

状态转换表如图所示由题目要求可知,选择Moore型状态机实现功能。

通过quartusII 仿真验证功能。

源程序如下:module zuoye_1(clk,din,op);input clk,din;output op;reg[1:0]current_state,next_state;reg op;parameter S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11;always@(posedge clk)begincurrent_state <= next_state;endalways@(current_state or din)begincase(current_state)S0: beginop=0;if(din==0)next_state=S0;elsenext_state=S1;endS1: beginop=0;if(din==0)next_state=S0;elsenext_state=S2;endS2: beginop=0;if(din==0)next_state=S0;elsenext_state=S3;endS3: beginop=1;if(din==0)next_state=S0;elsenext_state=S3;enddefault:beginop=0;next_state=S0;endendcaseendendmodule编写激励文件如下:预置输入为:1001101110111101111100001101110`timescale 1 ns/ 1 psmodule cj_1_vlg_tst();reg clk;reg din;wire op;cj_1 i1 (.clk(clk),.din(din),.op(op));initialbeginclk=0;din=1; 1001101110111101111100001101110 #1 din=0;#2 din=1;#2 din=0;#1 din=1;#3 din=0;#1 din=1;#4 din=0;#1 din=1;#5 din=0;#1 din=0;#1 din=0;#2 din=1;#2 din=0;#1 din=1;#3 din=0;#1 $stop();$display("Running testbench");endalwaysbegin#(0.5) clk=~clk;endendmodule以下为仿真逻辑原理图:RTL VIEWERTechnology map viewer(mapping)Technology map viewer(fitting)以下为仿真波形图:。

哈工大数字电子技术基础习题册2010-答案6-7章

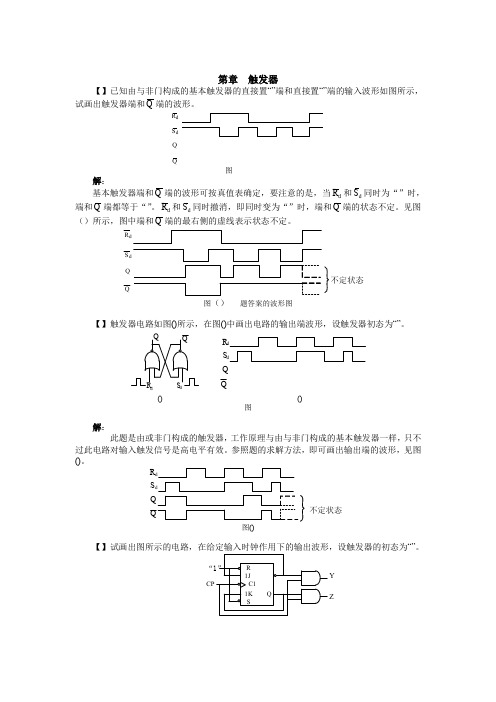

第章 触发器【】已知由与非门构成的基本触发器的直接置“”端和直接置“”端的输入波形如图所示,试画出触发器端和Q 端的波形。

R dSdQ Q图 解: 基本触发器端和Q 端的波形可按真值表确定,要注意的是,当d R 和d S 同时为“”时,端和Q 端都等于“”。

d R 和d S 同时撤消,即同时变为“”时,端和Q 端的状态不定。

见图()所示,图中端和Q 端的最右侧的虚线表示状态不定。

R d S dQQ不定状态图() 题答案的波形图【】触发器电路如图()所示,在图()中画出电路的输出端波形,设触发器初态为“”。

Q dS dQQ R() ()图解:此题是由或非门构成的触发器,工作原理与由与非门构成的基本触发器一样,只不过此电路对输入触发信号是高电平有效。

参照题的求解方法,即可画出输出端的波形,见图()。

dS dQR 不定状态图()【】试画出图所示的电路,在给定输入时钟作用下的输出波形,设触发器的初态为“”。

“CP Y ZCP图 解:见图()所示,此电路可获得双相时钟。

Q QCPYZ图()【】分析图所示电路,列出真值表,写出特性方程,说明其逻辑功能。

Q图 解:.真值表(时,保持;时,如下表)D n Q n Q n+10 0 00 1 01 0 11 1 1.特性方程.该电路为锁存器(时钟型触发器)。

时,不接收的数据;时,把数据锁存,但该电路有空翻。

【】试画出在图所示输入波形的作用下,上升和下降边沿触发器的输出波形。

设触发器的初态为“”。

CPJK。

数电答案 哈工大

D+ +

d

(3) P3 = A C D ABCD ABCD AD ACD BCD ABD+ + + + = + + (或 )

AB+AC=0

(4) P4 = ABCD ABCD+ = A + B

耦,加速,隔直)。

+5V

+3V

C

Rc

AB

ui Rb

T

uo

图 4.1

G3

G1 G2

图 4.2

2.由 TTL 门组成的电路如图 4.2 所示,已知它们的输入短路电流为 IS=1.6mA,高电

平输入漏电流 IR=40μA。试问:当 A=B=1 时,G1 的灌(拉,灌)电流为 3.2mA ;A=0 时,

G1 的 拉 (拉,灌)电流为 160µA 。

UI − 0.7 ≥ VCC ;c. UI − 0.7 < VCC )。在饱

和状态,UI 需满足的条件为 b (a.UI>0;b.

Rb β Rc

Rb β Rc

电路中其他参数不变的条件下,仅 Rb 减小时,晶体管的饱和程度 加深 (减轻,加深,不

变);仅 Rc 减小时,饱和程度 减轻 (减轻,加深,不变)。图中 C 的作用是 加速 (去

(ABCD 为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为 1)

【3-6】 已知: Y1 = AB+ AC+ BD Y2 = ABCD+ ACD+ BCD+ BC 用卡诺图分别求出 Y1 ⋅Y2 , Y1 +Y2, Y1 ⊕Y2。

哈尔滨工业大学数字电子技术基础课程设计报告2:基于Verilog HDL语言的状态机编程

H a r b i n I n s t i t u t e o f T e c h n o l o g y数字电子技术基础大作业报告课程名称:数字电子技术基础设计题目:V erilog HDL 状态机编程院系:航天学院控制科学与工程系班级:0904102班姓名:某某某学号:1090410200指导教师:王淑娟设计时间:2011年12月哈尔滨工业大学Verilog HDL状态机编程1设计任务利用Verilog HDL设计一个电路,对输入的一串二进制数,用于检测序列中连续3个或者3个以上的1,状态转换如图所示。

图 12设计步骤1.安装Quartus II软件并破解。

2.根据设计要求编写程序代码。

3.生成仿真电路图和波形如图。

3程序代码module moore(clk,din,op);input clk,din;output op;reg[1:0] current_state,next_state;reg op;parameter S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11;always@(posedge clk)begincurrent_state<=next_state;endalways@(current_state or din)begincase(current_state)S0:beginop=0;if(din==0)next_state=S0;elsenext_state=S1;endS1:beginop=0;if(din==0)next_state=S0;elsenext_state=S2;endS2:beginop=0;if(din==0)next_state=S0;elsenext_state=S3;endS3:beginop=1;if(din==0)next_state=S0;elsenext_state=S3;enddefault:beginop=0;next_state=S0;endendcaseendendmodule4仿真电路图和波形图如下图所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

哈工大电大数字电子技术基础大作业

H a r b i n I n s t i t u t e o f T e c h n o l o g y

数字电子技术基础大作业

课程名称:数字电子技术基础

设计题目:血型与状态机

院系:

班级:

设计者:

学号:

哈尔滨工业大学

血型逻辑电路设计

一实验目的

1.掌握采用可编程逻辑器件实现数字电路与系统

的方法。

2.掌握采用Xilinx_ISE软件开发可编程逻辑器件

的过程。

3.学会设计血型能否输血的数字电路。

4.掌握Verilog HDL描述数字逻辑电路与系统的方

法。

二设计要求

1.采用BASYS2开发板开关,LED,数码管等制作验

证能否输血的电路。

2.采用Xilinx_ISE软件进行编程、仿真与下载设

计到BASYS2开发板。

三电路图

1.电路模块图(简化)

应用:

2.内部电路组成(简化)。