硬件设计模块参考原理图(不完整)

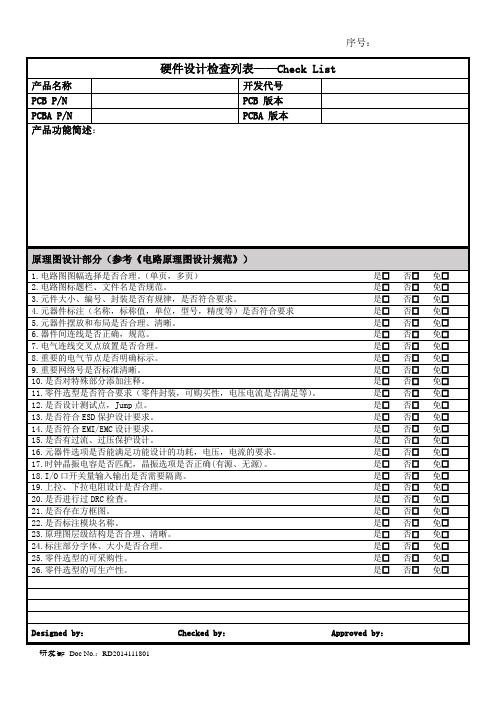

硬件-原理图布线图-设计审核表

23.当前版本的BOM是否需要变更确认。BOM 版本:_______, ECN:_________

是否免

24.过流保护是否工作正常,是否可靠

25.过压保护是否工作正常,是否可靠

Designedby:

Checkedby:

Approvedby:

是否免

4.元器件标注(名称,标称值,单位,型号,精度等)是否符合要求

是否免

5.元器件摆放和布局是否合理、清晰。

是否免

6.器件间连线是否正确,规范。

是否免

7.电气连线交叉点放置是否合理。

是否免

8.重要的电气节点是否明确标示。

是否免

9.重要网络号是否标准清晰。

是否免

10.是否对特殊部分添加注释。

是否免

11.零件选型是否符合要求(零件封装,可购买性,电压电流是否满足等)。

是否免

5.去耦电容摆放位置是否符合要求。

是否免

6.线宽,线距,GAP是否满足要求。

是否免

7.走线是否存在锐角、直角。

是否免

8.高频信号走线是否符合标准。

是否免

9.是否存在阻抗匹配要求。 阻抗匹配要求:

是否免

10.电源,GND是否符合要求。

是否免

11.器件PAD、焊盘大小是否符合要求。

是否免

12.过孔,通孔是否符合要求。

是否免

19.是否进行长时间可靠性测试(>=48H)。

是否免

20.当前版本是否需要Rework。ECN:___________________

是否免

21.当前版本原理图是否需要变更。原理图版本:________

是否免

22.当前版本PCB布线图是否需要变更。PCB版本:_______, ECN:_________

F8L10D 系列 LoRa 模块用户硬件设计手册说明书

本手册适用于F8L10D 系列LoRa 模块厦门四信通信科技有限公司Add:厦门市集美区软件园三期诚毅大街370号A06栋11层客户热线:400-8838-199电话:+86-592-6300320传真:+86-592-5912735网址F8L10D LoRa 模块用户硬件设计手册文档版本密级V2.0.1产品名称:F8L10D共29页文件修定记录日期版本号备注作者2016-09-14V1.0.0初始版本XQ.QIU 2017-07-04V1.1.0修改硬件设计部分参数XQ.QIU 2017-09-23V2.0.0更新地址Faine2017-11-23V2.0.1修改Uart接口RX引脚编号YSL著作权声明本文档所载的所有材料或内容受版权法的保护,所有版权由厦门四信通信科技有限公司拥有,但注明引用其他方的内容除外。

未经四信公司书面许可,任何人不得将本文档上的任何内容以任何方式进行复制、经销、翻印、连接、传送等任何商业目的的使用,但对于非商业目的的、个人使用的下载或打印(条件是不得修改,且须保留该材料中的版权说明或其他所有权的说明)除外。

商标声明Four-Faith、四信、、、均系厦门四信通信科技有限公司注册商标,未经事先书面许可,任何人不得以任何方式使用四信名称及四信的商标、标记。

目录目录 (4)前言 (5)1概述 (6)1.1技术规格 (6)1.1.1规格说明 (6)1.1.2基本功能 (6)1.1.3模块接口 (7)1.1.4LoRa参数 (7)1.1.5供电 (7)1.1.6功耗 (8)1.2相关文档 (8)1.3缩略语 (8)2F8L10D模块产品框图 (11)3管脚描述 (12)4硬件接口描述 (14)4.1概述 (14)4.2电源 (14)4.3UART接口 (15)4.3.1硬件连接 (15)4.3.2通讯传输字节格式 (16)4.3.2F8L10D通信对象为PC机 (17)4.3.2F8L10D通信对象为工控机 (17)4.4复位 (17)4.5GPIO口 (18)4.5.1控制LED灯 (19)4.5.2ADC采集参考电路 (19)4.5.3IO口保护电路 (20)4.6模块休眠 (20)4.6.1休眠控制脚SLEEP_RQ (21)4.9LoRa通过MCU对模块升级 (21)4.9.1双串口升级模式 (21)4.9.2MCU单串口升级模式 (22)4.10天线 (22)4.10.1F8L10D兼容2种天线模式: (22)4.10.2天线安装 (23)5模块硬件设计 (25)5.1硬件设计 (25)5.2模块封装尺寸 (25)5.3Re-flow回流焊温度范围 (27)订购信息 (29)前言概述本文档适用的产品是:F8L10D系列模块。

M_Translator_485_SP3485 模块硬件设计手册说明书

M_Translator_485_SP3485模块硬件设计手册文档名M_Translator_485_SP3485模块硬件设计手册作者Jinyi完成日2021.06.01版本V1.0文档状态发布修改记录:日期作者版本修改说明2021.06.01Jinyi 1.0新建1.概述合宙系列电路模组,是为了降低开发者硬件设计难度为目的,将嵌入式硬件开发常用的硬件功能部件封装成模组形式,省去客户选型,调试的步骤,通过标准化的设计来降低客户开发时间和成本,同时LGA的管脚形式兼顾成本和批量贴片生产可靠性。

M_Translator_485_SP3485是一款3.3V供电、半双工、低功耗的TTL转485模块,内部包括两路电平转换电路,一个驱动器和一个接收器,最高可允许256个SP3485收发器并接在同一通信总线上,体积小巧,适用于2G,3G,4G蜂窝通信系统,NB,MCU等嵌入式系统。

2.电气特性型号M_Translator_485_SP3485电源电压3V To3.6V工作电流1mA(Max)关断电流10uA(Max)输入逻辑低0.7V以下电平输入逻辑高1.3V以上电平最大数据传100kbps输速率驱动差分输3.3V出输出共模电3V(Max)压输出短路时250mA(Max)的电流工作温度–40°C~+85°C过温关断阈140°C值温度M_Translator_485_SP3485模块硬件设计手册3.模块内部框图4.封装信息M_Translator_485模块采用LGA 封装,其管脚定义以及尺寸如下图:图1(顶视图)MOS 电平匹配电路485收发器滤波电容TVS +PTCTTL485图2推荐PCB封装:图3注意:官方提供模块的原理图和PCB封装库,下载地址:https:///wiki/21?wiki_page_id=2774。

5.管脚详细定义NO.管脚名称Type描述备注1VCC_IO P外接TTL参考匹配电平,支持1.8V~VCC内置滤波电容2RO O485接收器输出端,连接至MCU的RXD 内置电平转换电路,与VCC_IO电平一致3RD I接收/驱动器使能控制内部上拉至VCC,与输入信号同向,与RD同时只能使用一路,推荐优先使用,不用则悬空4RD I接收/驱动器使能控制内置电平反向电路,与输入信号反向,与RD同时只能使用一路,不用则悬空5DI I485驱动器输入端,连接至MCU的TXD 内置电平转换电路,与VCC_IO电平一致6GND P参考地管脚7A I/O接收器同相输入和驱动器同相内置PTC+ESD静电防护输出端8GND P参考地管脚9B I/O接收器反相输入和驱动器反相内置PTC+ESD静电防护输出端10VCC P模块电源输入管脚,3.0~3.6V内置滤波电容11GND P模块底部焊盘,接地处理6.参考设计原理图图4485模块参考设计注意:1.VCC_IO为输入的TTL信号的参考匹配电平,用户根据接入的TTL电平信号进行匹配,如果不外接VCC_IO参考电平,用户可配置主控端的TX,RX管脚为上拉进行匹配。

联盛德微电子 W0802P模块硬件设计指导书说明书

W0802P模块硬件设计指导书V7.1北京联盛德微电子有限责任公司 (winner micro)地址:北京市海淀区阜成路67号银都大厦6层电话:+86-10-62161900公司网址:文档历史北京联盛德微电子有限责任公司目录1概述 (1)2模块管脚定义 (1)3模块原理图设计 (3)4典型外围电路设计 (3)4.1电源供电 (3)4.2Reset电路设计 (4)4.3Wakeup电路设计 (4)4.4Boot下载功能 (4)4.5GPIO功能 (4)4.6ESD防护 (4)5模块外围设计 (4)5.1模块封装设计 (4)5.2模块布局设计 (5)5.3模块GPIO Layout设计 (6)6产品结构设计 (7)1概述W0802P是基于嵌入式Wi-Fi/蓝牙双模 SoC芯片W800设计的物联网无线模块。

该模块支持2.4G IEEE802.11 b/g/n Wi-Fi协议,内置完整的TCP/IP协议栈;支持蓝牙/BLE 4.2协议,支持蓝牙配网,支持蓝牙Mesh。

模块适用于智能家电、智能家居、无线音视频、智能玩具、医疗监护、工业控制、医疗监护等广泛的物联网领域,是物联网应用的理想解决方案。

W0802P采用SMD封装,邮票孔式接口,PCB板载天线。

可通过标准SMT设备实现产品的快速生产,为客户提供高可靠性的连接方式,特别适合自动化、大规模、低成本的现代化生产方式,方便应用于各种物联网硬件终端场合。

2模块管脚定义模块管脚排列及尺寸信息如图2-1所示:图2-1 模块引脚排列及尺寸图模块管脚说明如表2-1所示:表2-1 模块管脚说明3模块原理图设计44.1 电源供电建议模块电源输入脚至少放置一个47uF 滤波电容,且外部供电电源的最大输出电流建议在500mA 及以上。

CON1J24.2Reset电路设计模块上电自动复位,如果外部主控单元控制该管脚,低电平条件下模块复位。

4.3Wakeup电路设计Wakeup脚为外部唤醒脚,当芯片进入睡眠状态后,Wakeup脚给高电平时,芯片唤醒。

硬件设计_进度表

编号 计划节点 时间节点 负责人 2016年10月18号——2016年10月22日 人员 任务 1、去深圳考察可满足铭通智能硬件设计的厂家 2、商务洽谈,签订合作协议 3、厂商提方案、做设计,铭通现场技术跟进。 4、总体设计完成。 1、双方技术审核总体设计。 2、出审核报告 1、提请购单、签字、审批 2、下单,收货。 3、测试 4、测试报告 各个模块的详细设计出图 1、总体原理图、分模块原理图 2、PCB图 3、CAD组装图 4、 1、双方技术审核 2、出审核报告 3、 4、 1、印刷、焊接 2、 3、

1

总体设计

2

审核

3

关键器件的选购 购买、测试

4

5

审核

6

集成板的印刷、焊接

编号

计划节点 集成板的组装、测试、 序烧写 程

时间节点

负责人

人员 1、组装测试 2、程序编写测试 3、 4、 1、联调计划 2、联调 3、联调报告 4、 1、双方技术审核 2、审核报告 3、 4、 1、外壳生产

任务

7

8

系统联调

9

审核

10

外收 2、验收报告 3、 4、 5、 1、根据上述技术要求批产 2、 3、 4、 5、

12

批量生产

PROTEUS软件介绍及原理图

一、进入Proteus ISIS

双击桌面上的ISIS 6 Professional图标或者单击屏幕左下方的“ 开始”→“程序”→“Proteus 6 Professional” →“ISIS 6 Professional”,出现如图1-1所示屏幕,表明进入Proteus ISIS集成 环境。

二、工作界面

移动多个元件并且复制:在原理图编辑区中,右键选中要选

的元件,然后点击按钮,就可以移动复制的元件。 旋转元件:在原理图编辑区中,选中目标元件,然后点击以 下按钮或图标以旋转目标的方向。

删除元件:在原理图编辑区中,右键双击目标,或者选中

目标后,点击按钮 图标删除目标元件。 打开元件的属性:右键单击目标元件,然后左键单击目标 元件,就会出现一个对话框就是了。 添加元件到原理编辑区中:元件列表中,选中目标元件, 然后在原理图编辑区中,左键点击就可以了。

局部文件(*.SEC)设计图的一部分,可输出为一 个局部文件,以后可以导入到其他的图中。在文 件菜单中以导入(Import)、导出(Export)命 令来操作。 模快文件(*.MOD) 库文件(*.LIB)元器件和库。 网表文件(*.SDF)当输出到PROSPICE AND ARES 时产生的网表文件。

N

2.1.1 Proteus ISIS的编辑环境设置

Proteus ISIS编辑环境的设置主要是指模板的选择、 图纸的选择、图纸的设置和格点的设置。绘制电路 图首先要选择模板,模板控制电路图外观的信息, 比如图形格式、文本格式、设计颜色、线条连接点 大小和图形等。然后设置图纸,如设置纸张的型号、 标注的字体等。

第4章 集成化的电路虚拟仿真软件 Proteus

Proteus 软件是由英国 Labcenter Electronics 公司开发的EDA工具软件,已有近20年的历史,在 全球得到了广泛应用。Proteus 软件的功能强大, 它集电路设计、制版及仿真等多种功能于一身,不 仅能够对电工、电子技术学科涉及的电路进行设计 与分析,还能够对微处理器进行设计和仿真,并且 功能齐全,界面多彩,是近年来备受电子设计爱好 者青睐的一款新型电子线路设计与仿真软件。

硬件设计要点和原理图检查要点

硬件设计要点和原理图检查要点目录1目的及意义 (2)2原理图设计要点 (2)3原理图检查要点 (6)4PCB检查要点 (9)1目的及意义本文主要目的有如下几点:1.论述硬件原理图设计时一些重要的要点,这些要点是以前设计经验的总结。

根据这些原则设计原理图,可以使设计更规范,更正确。

2.规范原理图Review时一些关键的检查点,根据这些检查点,可以避免一些低级的错误,从最大程度上保证工程师的设计初衷是和所画出来的原理图是完全一致的。

3.规范PCB Review时一些关键的检查点,可以从最大程度避免工程师在PCB上所犯的低级失误。

以下符号表示的意义:●表明必须要遵循的要求●表明强烈推荐的要求●表明建议的要求工程师可以●确认此个检查项●确认检查项不能被满足2原理图设计要点1)芯片的外围电路设计尽量使用参考设计,以及芯片的硬件设计指南2)尽量拷贝别人已经验证过的原理图3)时钟以及高速信号要有正确的端接方式,要求不高的可采用源端串联方式4)时钟信号尽量采用点对点连接方式5)高速并行总线的时钟应该从同一片芯片发出6)在PCB空间足够的情况下,每个电源PIN上都保证有一个去耦电容.并且靠近电源PIN7)尽量使用oscillators而不是crystals.8)对于时钟分发芯片,使用带有PLL功能的Distribution提高时钟性能.9)选择适当的电容耐压值,对于一般钽电容应该按2X标准选择10)按钮信号应该有去抖功能11)接口器件是否有ESD保护功能.12)对于载板/子板/背板的接口信号,逐个检查接口信号是否一致.13)单板的功耗/散热必须满足实际工作环境14)在相同功能的情况下,选用接口尽量简单,元器件管脚数尽量少的元器件15)运用仿真工具,确定高速信号正确的端接方式16)在无特殊的情况下,尽量选用标准的电源模块,电源的输出能力要达到负载峰值电流的20%以上17)对于有几种电源供电的IC,必须注意上电顺序问题18)没有特别需要,请使用已验证过的元器件.19)高速串行总线的时钟源必须选用所要求的时钟精度/Jitter20)对于PCI信号,严格遵循上/下拉原则:●以下信号无需上下拉:AD[0:31],CBE[0:3]#,IDSEL,PAR●以下信号必需上拉(4.7K):AD[32:63],FRAME#, TRDY#, IRDY#,DEVSEL#, STOP#, SERR#, PERR#, LOCK#, INTA#, INTB#, INTC#,INTD#, REQ64#, ACK64#,CBE[4:7]#,另外还有仲裁器的REG#/GNT#信号21)对于CompactPCI单板,背板CPCI接口应遵循如下原则:●总线串阻原则i.所有总线型的PCI信号都应该串有10欧姆的电阻,这些信号有:AD0-AD31, C/BE0#-C/BE3#, PAR, FRAME#, IRDY#, TRDY#,STOP#, LOCK#, IDSEL, DEVSEL#, PERR#, SERR#, RST#.ii.如果以下信号被使用,也需要串接10欧姆的电阻: INTA#, INTB#, INTC#, INTD#, SB0#, SDONE, AD32-AD63, C/BE4#-C/BE7#,REQ64#, ACK64#, PAR64.iii.以下是点到点信号不需要串接10欧姆的电阻: CLK, REQ#, GNT#, TDI, TDO, TCK, TMS, TRST#, BD_SEL#, HEALTHY#●总线预充电原则,如无括号内注明默认的上拉电阻值都为10K:iv.预充电偏差电压为VP(1V左右的预充电电压)的信号为: 所有总线型信号原则上都预充电到VP,其中有:AD0-AD31, C/BE0#-C/BE3#,PAR, FRAME#, IRDY#, TRDY#, STOP#, LOCK#, IDSEL,DEVSEL#, PERR#, SERR#v.预充电偏差电压是VIO(因为是长针也算是前级电源)的信号为: PCI_RST#, ENUM#, INTA#, INTB#, INTC#, INTD#, REQ#,GNT#(上拉电阻100K), BD_SEL#(上拉电阻1.2K), M66EN,PCIXCAPvi.特例:HEALTHY#不需要预充电电压,但由于其开集电极输出特性,所以上拉到VIO(2K),PCI_CLK可以接到VP,也可以接到VIO,一般还是接到VP22)I2C/SMBus必须要有上拉电阻23)对于不用的具有输入特性的PIN,应接到无效电平。

rtl8211f硬件设计

rtl8211f硬件设计RTL8211F是一种高性能的以太网接口芯片,广泛应用于各种网络设备中。

在进行RTL8211F的硬件设计时,需要参考以下内容:1. 数据手册和应用指南:RTL8211F的制造商通常提供数据手册和应用指南,这些文档详细描述了芯片的功能、特性、引脚定义和电气特性等。

可以通过这些文档来了解芯片的技术规格,以及如何正确使用和连接它。

2. 原理图:根据RTL8211F的设计要求和应用场景,最好参考厂商提供的参考设计原理图。

原理图将显示芯片与其他组件的连接方式,以及必要的外部电路,如滤波器、电源电路、隔离电路等。

3. PCB布局指导:RTL8211F是封装在表面贴装设备(SMD)中的芯片,因此其PCB布局非常重要。

制造商通常会提供PCB布局指导,以确保良好的信号完整性和抗干扰性能。

这些指导通常涵盖部分布局、地线和电源平面规划、差分信号匹配和信号控制等方面。

4. 额定电器参数:在设计RTL8211F的硬件时,需要确保其工作在其额定电器参数的范围内,以保证性能和可靠性。

这些参数包括工作电压、工作温度、峰值功耗、电气特性(如输出电流、输入电阻、信号电平等)等。

5. ESD和EMI设计指南:在网络设备中,如交换机和路由器,对于抗静电击穿(ESD)和抗电磁干扰(EMI)的能力要求非常高。

因此,在RTL8211F的硬件设计中,应参考相关的ESD和EMI设计指南,以确保设备具备足够的抗干扰能力和可靠性。

6. 控制器和主机接口设计:RTL8211F通常与外部控制器或主机芯片一起使用,如以太网控制器或微控制器。

在硬件设计中,需要参考相关的控制器或主机接口设计,以确保正确连接和通信。

7. 瞬态保护电路:为了保护RTL8211F免受电气快速变化和干扰的影响,应该在其电源线和输入输出端口上添加适当的瞬态保护电路。

这些电路包括TVS二极管、瞬态电压抑制器(TVR)和滤波器等。

总之,在进行RTL8211F的硬件设计时,需要参考数据手册、应用指南、参考设计原理图和相关设计指南,以确保设计满足其技术要求,具备良好的信号完整性和抗干扰能力。