IC工艺几种IC工艺流程演示文稿

IC的生产工序流程以及其结构

IC的生产工序流程以及其结构IC(集成电路)是一种通过技术手段将多个电子器件集成到一个芯片上的电子器件。

IC的生产工序流程包含了多个环节,每个环节都需要严格的控制和测试,以确保最终产品的质量和性能。

IC的生产工序流程可以大致分为晶圆制备、晶圆加工、封装和测试四个阶段。

第一阶段:晶圆制备晶圆制备是IC生产的第一步,即将选择好的硅片制备成适用于IC加工的基片。

该阶段主要包括以下步骤:1.基片选择:选择具有较高晶片质量的硅片作为基片。

2.磨平:使用化学机械研磨等技术将硅片的表面进行磨平,以提高晶片的表面质量。

3.清洗:通过化学清洗等方法清除硅片表面的杂质,以增加晶片的纯度。

4.涂覆:将具有特殊光敏性的光刻胶均匀涂覆在硅片表面,用于后续的芯片图案制作。

第二阶段:晶圆加工晶圆加工是IC生产的核心阶段,主要是通过光刻、蚀刻、沉积等工艺,将芯片的电路图案逐层刻制在硅片上。

该阶段主要包括以下步骤:1.光刻:使用光刻胶模具和紫外光照射,将芯片电路的设计图案转移到硅片上。

2.蚀刻:使用化学或物理蚀刻方法,将光刻胶以外的硅片材料去除,形成芯片电路的各个层次。

3.沉积:使用化学气相沉积、物理气相沉积等方法,将金属、氧化物等材料沉积在芯片表面,形成电路的导线、阻抗等元件。

4.清洗和检查:对加工后的芯片进行清洗和检查,确保电路图案和元件的质量和完整性。

第三阶段:封装封装是将完成加工的芯片封装成IC产品的过程,主要是为了保护芯片、便于使用和连接外部元件。

该阶段主要包括以下步骤:1.切割和研磨:将加工好的硅片切割成单个的芯片,并通过研磨等方法将芯片的厚度调整到设计要求。

2.封装设计:根据芯片的功能和尺寸要求,设计适用的封装结构和材料,并设计电路连接引脚和封装外壳。

3.芯片安装:将芯片粘贴或焊接到封装结构的基座上,并通过线键和焊球等方法与引脚进行连接。

4.密封:将芯片和引脚密封在封装外壳中,以保护芯片免受环境影响。

5.清洗和测试:对封装好的芯片进行清洗和测试,确保封装的质量和性能。

IC封装工艺范文

IC封装工艺范文

SMD封装工艺

SMD,即表面贴装安装工艺,是一种把元件安装在主板上的新型集成

电路封装工艺。

相比传统的封装工艺,它的特点是采用贴片方式,将元件

安装在主板上,因此又叫做“表面贴装”。

SMD封装工艺流程

1、确定元件安装位置:将记录在PCB板上的器件位置和数量传输到

贴片机。

2、把每个元件放入滑台:将元件以元素的方式装入滑台,以便贴片

机轻松地进行抓取和定位。

3、把元件放入贴片位置:把滑台上的元件放入贴片机上的固定位置,以便贴片机可以抓取和定位元件。

4、用贴片机夹紧元件:将固定位置上的元件用贴片机夹紧,以便在

安装过程中不会发生移位现象。

5、把元件移动到指定位置:将夹紧的元件移动到PCB板上器件的指

定安装位置,以便将其与PCB板接触并固定住。

6、把元件焊接到基板:将元件焊接到PCB板上,完成元件的安装过程。

7、检查并确认安装质量:检查所有安装的元件,确认安装的质量,

确保元件的电性能和机械性能正确无误。

优点:

1、SMD封装工艺的优势在于可以在相同的尺寸限制内有效地安装更多的元器件,可以实现更高的集成度。

2、SMD封装工艺非常省时,因为元器件可以用贴片机直接安装,减少安装所需的时间。

3、SMD封装工艺具有非常高的安装精度。

半导体IC的制做工艺图解

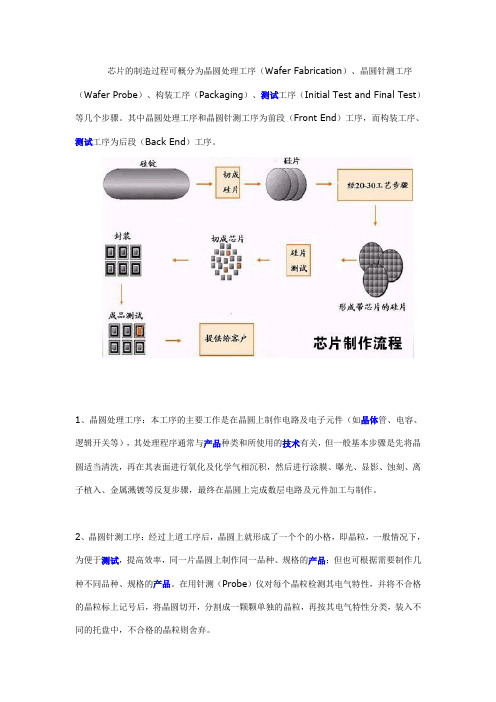

芯片的制造过程可概分为晶圆处理工序(Wafer Fabrication)、晶圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial Test and Final Test)等几个步骤。

其中晶圆处理工序和晶圆针测工序为前段(Front End)工序,而构装工序、测试工序为后段(Back End)工序。

1、晶圆处理工序:本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2、晶圆针测工序:经过上道工序后,晶圆上就形成了一个个的小格,即晶粒,一般情况下,为便于测试,提高效率,同一片晶圆上制作同一品种、规格的产品;但也可根据需要制作几种不同品种、规格的产品。

在用针测(Probe)仪对每个晶粒检测其电气特性,并将不合格的晶粒标上记号后,将晶圆切开,分割成一颗颗单独的晶粒,再按其电气特性分类,装入不同的托盘中,不合格的晶粒则舍弃。

3、构装工序:就是将单个的晶粒固定在塑胶或陶瓷制的芯片基座上,并把晶粒上蚀刻出的一些引接线端与基座底部伸出的插脚连接,以作为与外界电路板连接之用,最后盖上塑胶盖板,用胶水封死。

其目的是用以保护晶粒避免受到机械刮伤或高温破坏。

到此才算制成了一块集成电路芯片(即我们在电脑里可以看到的那些黑色或褐色,两边或四边带有许多插脚或引线的矩形小块)。

4、测试工序:芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。

经测试后的芯片,依其电气特性划分为不同等级。

而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。

IC封装工艺介绍(PPT45页)

Die Attach质量检查: Die Shear(芯片剪切力)

IC封装工艺介绍(PPT45页)

Logo

FOL– Wire Bonding 引线焊接

※利用高纯度的金线(Au) 、铜线(Cu)或铝线(Al)把 Pad 和引线通过焊接的方法连接起来。Pad是芯片上电路的外接点

IC Design IC设计

SMT IC组装

Wafer Fab 晶圆制造

Wafer Probe 晶圆测试

Assembly& Test IC 封装测试

IC封装工艺介绍(PPT45页)

IC封装工艺介绍(PPT45页)

Logo

IC Package (IC的封装形式)

Package--封装体:

➢指芯片(Die)和不同类型的框架(L/F)和塑封料(EMC) 形成的不同外形的封装体。

SMT SMT

IC封装工艺介绍(PPT45页)

Logo

IC Package (IC的封装形式)

• 按封装外型可分为: SOT 、QFN 、SOIC、TSSOP、QFP、BGA、CSP等;

封装形式和工艺逐步高级和复杂

• 决定封装形式的两个关键因素: ➢ 封装效率。芯片面积/封装面积,尽量接近1:1; ➢ 引脚数。引脚数越多,越高级,但是工艺难度也相应增加;

第二,支撑:支撑有两个作用,一是支撑芯片,将芯片固 定好便于电路的连接,二是封装完成以后,形成一定的外形以 支撑整个器件、使得整个器件不易损坏。

IC封装工艺介绍(PPT45页)

IC封装工艺介绍(PPT45页)

Logo

半导体封装的目的及作用

第三,连接:连接的作用是将芯片的电极和外界的电路连 通。引脚用于和外界电路连通,金线则将引脚和芯片的电路连 接起来。载片台用于承载芯片,环氧树脂粘合剂用于将芯片粘 贴在载片台上,引脚用于支撑整个器件,而塑封体则起到固定 及保护作用。

芯片生产工艺流程ppt课件

SiO 2

外延层

发射区

基区

集电区

55

背金合金

SiO 2

外延层

发射区

基区

集电区

56

芯片测试

SiO 2

外延层

发射区

基区

集电区

测试系统

57

N型片制造(一般)工艺流程

N

一次氧化

基区光刻

干氧氧化

硼离子注入

基区扩散

发射区光刻

发射区磷预淀积

发射区扩散

发射区低温氧化

氢气处理

3次光刻

铝蒸发

四次光刻

氮氢合金

铝上CVD

先进光刻曝光设备

11

单项工艺-光刻(2)

现场用光刻曝光设备

12

单项工艺-光刻(3)

检查用显微镜

13

单项工艺-光刻(4)

清洗

淀积/生长隔离层

(SiO2 Si3N4 金属…)

匀胶

-HMDS喷淋(增加Si的粘性) -匀光刻胶

14

单项工艺-光刻(5)

前烘

-增加黏附作用 -促进有机溶剂挥发

对版

-对每个圆片必须按要求对版

匀胶

-用弧光灯将光刻版上的图案转 移到光刻胶上。

15

单项工艺-光刻(6)

显影/漂洗

-将圆片进行显影/漂洗,不需要的 的光刻胶溶解到有机溶剂。

坚

膜

-硬化光刻胶。 -增加与硅片的附着性。

腐蚀

-干法腐蚀/湿法腐蚀

去胶

16

单项工艺-光刻(7)

光刻工艺过程

17

单项工艺-CVD(1)

18

单项工艺-CVD(2)

溅射原理示意图

27

单相工艺-蒸发(3)

IC制作流程范文

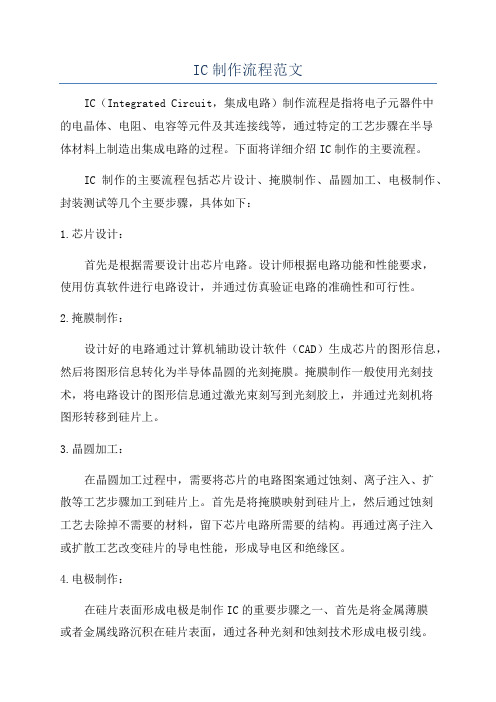

IC制作流程范文IC(Integrated Circuit,集成电路)制作流程是指将电子元器件中的电晶体、电阻、电容等元件及其连接线等,通过特定的工艺步骤在半导体材料上制造出集成电路的过程。

下面将详细介绍IC制作的主要流程。

IC制作的主要流程包括芯片设计、掩膜制作、晶圆加工、电极制作、封装测试等几个主要步骤,具体如下:1.芯片设计:首先是根据需要设计出芯片电路。

设计师根据电路功能和性能要求,使用仿真软件进行电路设计,并通过仿真验证电路的准确性和可行性。

2.掩膜制作:设计好的电路通过计算机辅助设计软件(CAD)生成芯片的图形信息,然后将图形信息转化为半导体晶圆的光刻掩膜。

掩膜制作一般使用光刻技术,将电路设计的图形信息通过激光束刻写到光刻胶上,并通过光刻机将图形转移到硅片上。

3.晶圆加工:在晶圆加工过程中,需要将芯片的电路图案通过蚀刻、离子注入、扩散等工艺步骤加工到硅片上。

首先是将掩膜映射到硅片上,然后通过蚀刻工艺去除掉不需要的材料,留下芯片电路所需要的结构。

再通过离子注入或扩散工艺改变硅片的导电性能,形成导电区和绝缘区。

4.电极制作:在硅片表面形成电极是制作IC的重要步骤之一、首先是将金属薄膜或者金属线路沉积在硅片表面,通过各种光刻和蚀刻技术形成电极引线。

然后通过热处理来实现电极与半导体器件之间的连接,并形成稳定的电路结构。

5.封装测试:在IC制作完成后,需要将元器件和电路在硅片上面封装成IC。

同时还需要进行电性能测试、可靠性测试等。

封装是将芯片放置到适当的封装载体中,并通过焊接或粘接进行可靠地连接。

6.封装完成后,对IC进行电性能测试和可靠性测试。

测试包括功能测试、性能测试、温度测试、电压测试、电流测试等。

这些测试主要是为了验证芯片的各项电性能指标的准确性和稳定性。

以上是IC制作的主要流程,其中每个步骤都包括了一系列的操作和工艺方法。

整个IC制作流程需要高度的技术和严格的控制,以确保制造出优质的集成电路产品。

集成电路ic--芯片制造工艺的八大步骤

集成电路ic--芯片制造工艺的八大步骤集成电路(Integrated Circuit,IC)是现代电子技术的核心组成部分,广泛应用于计算机、通信、消费电子等领域。

IC的制造工艺涉及多个步骤,以下将详细介绍其八大步骤。

第一步,晶圆制备。

晶圆是IC制造的基础,它通常由高纯度的硅材料制成。

首先,将硅材料熔化,然后在石英坩埚中拉制出大型硅棒。

接着,将硅棒锯成薄片,形成晶圆。

第二步,沉积。

沉积是指在晶圆表面上沉积一层薄膜,用于制作电路的不同部分。

常用的沉积方法包括化学气相沉积和物理气相沉积。

通过这一步骤,可以形成绝缘层、导体层等。

第三步,光刻。

光刻是一种利用光敏物质的特性进行图案转移的技术。

首先,在晶圆表面涂覆光刻胶,然后使用掩膜板将光刻胶进行曝光,形成所需的图案。

接着,用化学液体将未曝光的部分去除,留下所需的图案。

第四步,蚀刻。

蚀刻是指将多余的材料从晶圆表面去除,以形成所需的结构。

蚀刻方法主要有湿法蚀刻和干法蚀刻两种。

通过这一步骤,可以制作出电路的导线、晶体管等元件。

第五步,离子注入。

离子注入是将特定的杂质离子注入晶圆表面,以改变材料的导电性能。

通过控制离子注入的能量和剂量,可以形成导电性能不同的区域,用于制作场效应晶体管等元件。

第六步,金属化。

金属化是将金属材料沉积在晶圆表面,形成电路的导线和连接器。

常用的金属化方法包括物理气相沉积和电镀。

通过这一步骤,可以形成电路的互连结构。

第七步,封装测试。

封装是将晶圆切割成独立的芯片,并封装到塑料或陶瓷封装中,以保护芯片并便于安装和使用。

测试是对封装好的芯片进行功能和可靠性测试,以确保芯片的质量。

第八步,成品测试。

成品测试是对封装好的芯片进行全面测试,以验证其功能和性能是否符合设计要求。

测试包括逻辑测试、温度测试、可靠性测试等。

通过这一步骤,可以筛选出不合格的芯片,确保只有优质的芯片进入市场。

以上就是集成电路IC制造工艺的八大步骤。

每个步骤都至关重要,缺一不可。

集成电路ic工艺流程

集成电路ic工艺流程

集成电路(IC)的制作过程,就像精心烹制一道高科技大餐,一步步来解析:

画蓝图:

首先,工程师们坐下来想:“我们要这个芯片干啥?”确定好它需要完成的任务。

接着,他们像搭积木一样,在电脑上设计出由各种小开关(逻辑门)组成的电路图。

然后,设计师得把这些电路“摆放”到一个虚拟的芯片板子上,规划好每个部分的位置,这就叫版图设计。

最后,用电脑模拟一下,看看设计出来的芯片能不能正常工作,这一步相当于在厨房里试菜。

硅片烹饪:

拿一块超级纯净的硅,做成又圆又平的晶圆,就像准备一张完美的烤盘。

在硅片上做“化学魔法”,加上一层薄薄的绝缘外套(氧化层),再巧妙地加入杂质,让它有的地方能导电,有的不能,这就形成了电路的基本元素。

开始“光影魔术手”——光刻,用光照和特殊胶水在硅片上印上电路图案,就像在蛋糕上做精细的糖霜装饰。

反复用化学方法“雕刻”和“堆积”,加层减层,做出多层的复杂电路,就像一层层叠加不同的食材。

打包出厂:

把晶圆切成一块块小芯片,每块都得先简单测验下,看看是不是都能“跑起来”。

给这些小芯片穿上“保护服”,用金属线连上外面的世界,就像给美食打包,方便食用。

再来一次全面体检,确认每个芯片都是健康强壮的,能胜任任务。

最后,根据它们的表现分等级,贴上标签,就可以出厂啦!

整个过程非常精细,而且全是高科技设备自动完成,保证了我们日常使用的电子设备里,那些微小而强大的芯片能够顺利诞生。

半导体IC的制做工艺图解(精)

芯片的制造过程可概分为晶圆处理工序(Wafer Fabrication)、晶圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial Test and Final Test)等几个步骤。

其中晶圆处理工序和晶圆针测工序为前段(Front End)工序,而构装工序、测试工序为后段(Back End)工序。

1、晶圆处理工序:本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2、晶圆针测工序:经过上道工序后,晶圆上就形成了一个个的小格,即晶粒,一般情况下,为便于测试,提高效率,同一片晶圆上制作同一品种、规格的产品;但也可根据需要制作几种不同品种、规格的产品。

在用针测(Probe)仪对每个晶粒检测其电气特性,并将不合格的晶粒标上记号后,将晶圆切开,分割成一颗颗单独的晶粒,再按其电气特性分类,装入不同的托盘中,不合格的晶粒则舍弃。

3、构装工序:就是将单个的晶粒固定在塑胶或陶瓷制的芯片基座上,并把晶粒上蚀刻出的一些引接线端与基座底部伸出的插脚连接,以作为与外界电路板连接之用,最后盖上塑胶盖板,用胶水封死。

其目的是用以保护晶粒避免受到机械刮伤或高温破坏。

到此才算制成了一块集成电路芯片(即我们在电脑里可以看到的那些黑色或褐色,两边或四边带有许多插脚或引线的矩形小块)。

4、测试工序:芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。

经测试后的芯片,依其电气特性划分为不同等级。

而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。

图解芯片制作工艺流程图课件

PPT学习交流

31

• 丢弃瑕疵内核:晶圆级别。测试过程中发现的有 瑕疵的内核被抛弃,留下完好的准备进入下一步。

PPT学习交流

32

PPT学习交流

33

• 放置晶圆的黑盒子

PPT学习交流

34

PPT学习交流

35

• 单个内核:内核级别。从晶圆上切割下来的单个 内核,这里展示的是Core i7的核心。

7

单晶硅锭:整体基本呈圆柱形,重 约100千克,硅纯度99.9999%。

PPT学习交流

8

PPT学习交流

9

PPT学习交流

处 理 晶 圆 的 机 器

10

• 硅锭切割:横向切割成圆形的单个硅片,也就是我们常说 的晶圆(Wafer)。顺便说,这下知道为什么晶圆都是圆形的 了吧?

PPT学习交流

11

• 晶圆:切割出的晶圆经过抛光后变得几乎完美无瑕,表面甚至可以当 镜子。事实上,Intel自己并不生产这种晶圆,而是从第三方半导体企 业那里直接购买成品,然后利用自己的生产线进一步加工,比如现在 主流的45nm HKMG(高K金属栅极)。值得一提的是,Intel公司创立之初 使用的晶圆尺寸只有2英寸/50毫米。

PPT学习交流

12

PPT学习交流

•芯 片 加 工 无 尘 车 间

13

PPT学习交流

14

• 光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过程 中浇上去的光刻胶液体,类似制作传统胶片的那种。晶圆 旋转可以让光刻胶铺的非常薄、非常平。

PPT学习交流

15

PPT学习交流

16

• 光刻:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得 可溶,期间发生的化学反应类似按下机械相机快门那一刻胶片的变化。 掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上, 就会形成微处理器的每一层电路图案。一般来说,在晶圆上得到的电 路图案是掩模上图案的四分之一。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Gas cabinet Ion source Filament Plasma

Extraction assembly Analyzing magnet Ion beam

Lighter ions

Mass resolving slit Acceleration column

2.

画出典型的流程图

2. Give an overview of the six major process areas and the sort/test area in the wafer fab.

3.

对6种主要工艺的应用和测试有大概的认识

3. For each of the 14 CMOS manufacturing steps, describe its primary purpose.

Wafer Cassettes

Wafer Transfer System

Soft Bake

Cool Plate

Cool Plate

Hard Bake

Simplified Schematic of Dry Plasma Etcher

Gas distribution baffle Anode electrode

Ionized CCl4 gas oxide

Polysilicon Deposition

Polysilicon Mask and Etch

Scanning ion beam

GSD

Active Regions

silicon nitride

top nitride S GD

oxide

Photoresist Develop

Ionized CF4 gas photoresist

oxide

Ionized oxygen gas oxide

Oxide Etch

Photoresist Strip

oxygen gate oxide

Oxidation (Gate oxide)

Dopant gas Silane gas polysilicon

4.

描述CMOS工艺14个步骤的主要目的

4. Discuss the key process and equipment used in each CMOS manufacturing step.

5.

能讨论每一步流程的关键工艺和设备

Major Fabrication Steps in MOS Process Flow

Quartz tube

Temperaturesetting voltages

Heater 1 Heater 2 Heater 3

Three-zone Heating Elements

Pressure controller

Exhaust

Photolithography Bay in a Sub-micron Wafer Fab

Model of Typical Wafer Flow in a Sub-Micron CMOS IC Fab

Wafer Fabrication (front-end)

Wafer Start

Unpatterned Wafer

Thin Films

Polish

Completed Wafer

Diffusion

IC工艺几种IC工艺流程演示文 稿

After studying the material in this chapter, you will be able to:

1. Draw a diagram showing how a typical wafer flows in a submicron CMOS IC fab.

Nitride Deposition

Contact holes

S GD

Contact Etch

Metal contacts

dS rGaiDn

Metal Deposition and

Etch

CMOS Process Flow

• Overview of Areas in a Wafer Fab

– Diffusion – Photolithography – Etch – Ion Implant – Thin Films – Polish

Simplified Schematic of a Photolithography Processing

Module

Load Station

Vapor Prime

Resist Develop- Edge-Bead

Coat

Rinse Removal Transfer Station

Wafer Stepper (Alignment/Exposure System)

oxygen

Silicon dioxide

Silicon substrate

Oxidation (Field oxide)

photoresist

UV light

Mask

exposed photoresist

Photoresist

Mask-Wafer

Exposed

Coating Alignment and Exposure Photoresist

Photo

Etch

Test/Sort

Implant

Simplified Schematic of High-Temperature Furnace

Temperature controller

Thermocouple measurements

Gas flow controller

Process gas

RF coax cable Photon Glow discharge (plasma) Vacuum gauge Wafer

Cathode electrode

Flow of byproducts and process gases

Exhaust to vacuum pump

Simplified Schematic of Ion Implanter

Etchant gas entering gas inlet

Electromagnetic field Free electron

Ion sheath

ee-

e-

+ Chamber wall

Positive ion

R

Radical chemical

Vacuum line

High-frequency energy