一种新型扫频仪的设计

一种低功耗扫频仪的设计与实现

• 79•针对国内的传统扫频仪价格昂贵,体积庞大且电路结构复杂等问题,本文提出了采用STC89C52微处理器作为控制电路核心,将DDS技术引入到AD9851芯片中,通过按键选择自动扫频模式和步进调频模式,利用数码管显示当前输出信号频率,通过信号调理模块对信号进行了修正。

经过测试,本系统可以在自动扫频和步进调频模式输出0-40MHZ频率范围内的波形,实验结果表明,系统具有成本低、功耗小、实时性好、失真度小和输出响应快等优点,本系统可广泛用于实用电源、电子测量、调频通讯等领域。

近年来,电子产业的发展日渐迅速,函数信号发生器在电子技术实验和设备检测中具有不可替代的用途。

目前,传统的扫频仪存在价格昂贵、功耗高、体积庞大且电路结构复杂等问题,在实际实践和实验操作中会,特别是微小型系统开发中产生许多不便。

目前,扫频仪已经历2代开发,第一代扫频仪主要以锯齿波调制需求信号源,并且通过阴极射线管显示结果;第二代扫频仪是一压控振荡器为核心,控制锁相频率合成技术,通过A/D或D/ A转换器将信号送入微处理器处理生成目标扫频信号。

前两代扫频仪由于压控振荡器特性限制,不能再够根据实际需求实时调节频率,除非额外加入波段切换硬件电路,所以系统成本也较高。

另外在扫频信号发生过程中由于采用闭环控制,系统响应时间较长,不能够适应快速响应场合。

1971年3月,美国学者J.Tierncy,C.M.Rader和B.Gold首次提出了直接数字频率合成(DDS-Direct Digital Synthesis)技术。

现在直接数字频率合成器(DDS)相比于其他频率合成方法,在许多方面较低了函数发生器的复杂度,提高了函数发生器的稳定性,降低了制造成本。

本设计采用ST89C52单片机作为控制部分,通过微处理器控制AD9851模块,利用AD9851内部A/D转换电路,产生原始波形,本系统针对DDS 技术,提出了合理的技术方案和任务划分,对AD9851模块进行了任务划分和底层驱动程序编写,为优化输出信号加入电压跟随器与RC滤波器,提高信号源的稳定性,输出波形失真小。

一种基于DDS的简易便携式扫频仪设计

一种基于DDS的简易便携式扫频仪设计

柴西林;范满红;张维昭;李锦珑

【期刊名称】《自动化与仪器仪表》

【年(卷),期】2014(0)8

【摘要】本设计是以STC89C52单片机作为主控芯片,控制一片高速DDS数字频率合成器AD9850,产生两路相正交的扫频信号并实现闭环稳幅,通过D/A和A/D 转换器等接口电路,实现扫频信号频率的步进调整、数字显示等。

本设计克服了传统模拟扫频仪的缺点,针对目前中低频段的扫频仪比较少的现状,具有很大的应用前景。

【总页数】3页(P41-43)

【关键词】扫频仪;STC89C52;AD9850;STC89C52;AD9850;LCD

【作者】柴西林;范满红;张维昭;李锦珑

【作者单位】西北师范大学知行学院;西北师范大学物电学院;兰州工业学院

【正文语种】中文

【中图分类】TN741

【相关文献】

1.基于DDS和PLL技术的便携式数字扫频仪的设计 [J], 芦莉;黄倩;郑光绪

2.基于数字零中频解调技术的便携式宽频扫频仪研制∗ [J], 张学斌;钱莹晶;张仁民;邓志明

3.基于AD9851的简易数字扫频仪的设计与制作 [J], 黄邓平;邱灿鹏

4.基于嵌入式系统便携式扫频仪的设计 [J], 孙鹏;胡兵;王育生

5.基于DDS技术的虚拟扫频仪的设计与实现 [J], 陈晓争

因版权原因,仅展示原文概要,查看原文内容请购买。

一种新型高速扫频仪设计及其实现

【 摘 , 要】 目前移动通信领域中设备研发、 网络建设、 网络优化的测试装置大多只支持单一的网络制式, 同时面临扫频速度不够

高 的问题 , 为运 营商带来诸 多不便 。提 出了一种 新型 多模 高速 扫频仪硬 件 架构 , 支持 各种 网络制 式 , 同 时采 用 多通道 基 带处理 方式显著提 高 了扫频速度 , 增加打 点数 目, 反映 了网络覆 盖细节 , 为 网络性能测试 、 网络优化测试 提供 了可 靠的分 析数据 。

瞻S

T E

【 本文献信息】施锋 , 朱宇霞.一种新型高速扫频仪设计及其实现[ J ] . 电视技术, 2 0 1 3 , 3 7 ( 7 )

种新型高速扫频仪设计及其实现

施 锋 , 朱 宇霞

( 1 . 武汉邮电科学研究院 , 湖北 武汉 4 3 0 0 7 5 ; 2 . 北京北方烽 火科技 有限公司, 北京 1 0 0 0 8 5 )

【 关键词】多模; 高速 ; 扫频仪; 多通道 【 中图分类号】T N 9 8

【 文献标志码】A

De s i g n a nd I m pl e me n t a t i o n o f Hi g h S pe e d S c an ni ng Fr e q ue nc y Equ i p me nt

r e l i a b l eh t h e n e t wo r k p e r f o r ma n c e nd a t h e n e t wo r k o p t i mi z a t i o n t e s t .

【 A b s t r a c t 】 T h e i f e l d s o f m o b i l e c o m m u n i c a t i o n s e q u i p m e n t r e s e a r c h a n d d e v e l o p m e n t , n e t w o r k c o n s t r u c t i o n , n e t w o r k o p t i m i z a t i o n t e s t d e v i c e s m o s l t y

一种新型扫频仪的设计

多个频 率 的系 统 元 件 的 组 合 I 。随 着 技 术 的 进 步 , 4

尤 其是 迅速 发展 的通 信领 域 对于频 率 精度 和稳 定度 的

要 求越来 越 高 ,频率 合成 技术 也受 到 了越来 越 多 的挑 战 。总地 来 说 ,频 率 合 成 技 术 的发 展 经 过 了 3个 阶

2 1 频 率合成 技 术 .

大 ,灵 活性强 ,能够进 行 编程 、除错 、再编 程 和重 复

操作 ,可以充 分地 进行 设计 开发 和 验证 。因此 由 D P S

频 率 合成 是 由一个 或几 个参 考频 率源 产生 一 个或

பைடு நூலகம்

芯 片和 F G P A可编 程逻 辑器 件所 组 成 的控 制 及数 据 处 理模块 外 围 电路少 ,运算 速 度快 。

MaWe ri a gP i n nu ,Y n e u j

( c olo lcrnc E gn eig iin U iest,X ’ 1 0 1 hn ) S h o f e t i n ier ,X da nv ri E o n y i n7 0 7 ,C ia a

A b ta t A e RF s e i g s se b s d o tu tr o o e fDS n GA i rs ne sr c n w we p n y tm a e n asr cu ec mp s d o P a d FP sp e e td, wih f— t o

a 叶技21 第2卷 5 0年 4 第 期 1

Elcr n c S i & Te h. e to i c . c /M a .1 y 5. 2 011

一

种 新 型 扫 频 仪 的 设 计

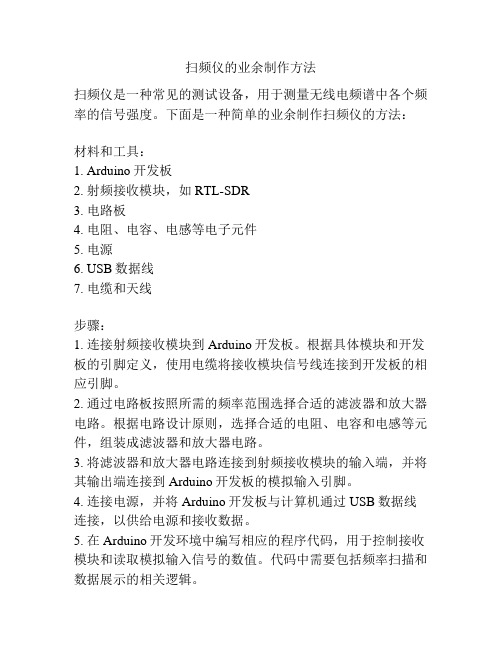

扫频仪的业余制作方法

扫频仪的业余制作方法

扫频仪是一种常见的测试设备,用于测量无线电频谱中各个频率的信号强度。

下面是一种简单的业余制作扫频仪的方法:

材料和工具:

1. Arduino开发板

2. 射频接收模块,如RTL-SDR

3. 电路板

4. 电阻、电容、电感等电子元件

5. 电源

6. USB数据线

7. 电缆和天线

步骤:

1. 连接射频接收模块到Arduino开发板。

根据具体模块和开发板的引脚定义,使用电缆将接收模块信号线连接到开发板的相应引脚。

2. 通过电路板按照所需的频率范围选择合适的滤波器和放大器电路。

根据电路设计原则,选择合适的电阻、电容和电感等元件,组装成滤波器和放大器电路。

3. 将滤波器和放大器电路连接到射频接收模块的输入端,并将其输出端连接到Arduino开发板的模拟输入引脚。

4. 连接电源,并将Arduino开发板与计算机通过USB数据线连接,以供给电源和接收数据。

5. 在Arduino开发环境中编写相应的程序代码,用于控制接收模块和读取模拟输入信号的数值。

代码中需要包括频率扫描和数据展示的相关逻辑。

6. 烧录程序代码到Arduino开发板中,运行程序。

这是一个简单的业余制作扫频仪的方法,但需要一定的电子知识和技能。

如果没有相关经验,建议先学习使用现有的扫频仪设备,然后再考虑自己制作。

基于DDS和PLL技术的便携式数字扫频仪的设计

De s i g n o f p o r t a b l e d i g i al t f r e q ue n c y s we e p e r

b a s e d o n DDS a n d PLL t e c h n o l o g y

文章编号 : 1 0 0 6—0 4 5 6 ( 2 0 1 4 ) 0 3— 0 2 7 8— 0 5

基于 D D S和 P L L技 术 的便 携 式 数 字 扫 频 仪 的设 计

芦莉 , 黄倩 , 郑光绪

( 南昌工程 学院机械 与电 气工程学 院, 江西 南昌 3 3 0 0 9 9 ) 摘要: 设计 了一款体积小 、 功耗低 、 使用灵活 、 成本低廉 的便携式数字扫频仪 。系统 的硬件设 计采用 D D S ( 直接 数 字式 频率 合成 器) 技术产生 0~ 7 0 MH z 的输 出频率 , 电容 三点式压控 振荡 电路及 MB 1 5 0 7琐 相环 电路产生 7 0~ 5 0 0 M Hz 的输 出频 率 , 并用 自动 电平控制 电路 , 保 持输 出振幅 的稳 定 , 用程控 衰减 电路实现 输 出幅度的连 续可调 。

p l i t u d e s t a b i l i t y , w i t h t h e p r o g r a m ma b l e a t t e n u a t i o n c i r c u i t r e a l i z i n g t h e c o n t i n u o u s a d j u s t a b l e o u t p u t a mp l i t u d e . D e -

第3 6卷第 3期 2 0 1 4年 9月

基于虚拟仪器的扫频仪的设计与实现

表起始频率、结束频率、频率点、For循环的中间变量、 循环次数。

(3)激励信号的产生。由PxI_5412产生所需频率的信 号、频率由卜一步的R确定。存信号发生时,信号的幅值 固定不变,仅频率不同。

(4)延时。目的是使得电路板加激励后进人工作稳定 状态。

(5)数据采集与处理。采用PXl6132采集电路板的输 出,调用Extract slgnal 1、one InfonnatioIL vi计算被测信号 的幅值,该函数功能强大,不仅误差小而且可以同时计算 山幅值和相位,但LabIVEw对其进行了算法加密,Help 中也没有对其进行任何说明。在每次循环中,将经过 Extract signal Tone Inforfnation.vi分析后的响应信号幅 值与信号源的幅值相除,实现归一化。

在虚拟仪器技术环境下,扫频所需的激励信号在计算 机中以软件方法产生且频率准确,网络(电路)响应信号由 采集卡采集送到计算机后,通过计算机强大的数值计算和 数据处理能力对采集到的信号进行分析处理,可以很方便 地得到被测网络(电路)的幅频特性.这是传统仪器难以独 立完成的。

在虚拟仪器环境下测量网络(电路)频率特性的方法 主要有以下4种;(1)多步法;(2)使用正弦波组合的单步 法;(3)使用Chirp信号的单步法;(4)使用随机信号的单步 法。这4种方法各有利弊,详见文献[3]。

·78·

万方数据

l基于虚拟仪器的扫

频仪设计 在开发某电路板自动

测试系统的过程中,由于需

要检测部分用于对信号进

行带通滤波的电路板,所以

基于多步法开发了检测该

类型电路板的扫频仪用户

程序。

扫频仪是~种与手工

测量原理最接近的方法,换

句话说,该方法将通常用的

简易低频扫频仪的设计与制作

。

频 率误 差 在

・

电子 翻作

, 料 翔

,

的数据处理能 力 强

、

速 度快

。

降低 原始 信 号 的 最 高 频 率 所 以在 对 信

,

是凌阳 公司 的 一 款

,

位

号进 行 采 样 之 前 要 通 过 低 通 滤 波 器 将 原始信 号 中较 高 的 频 率 分 量 滤 掉 如音

频 信号 的 频 率 范 围是

,

。

微 控 制 器 内部 框 图 如 图

,

。

本 系统 采 用 波

图 系统框 圈

。

单 片机 控 制 正 弦 信 号 发 生 器 芯 片 可 控 在时钟频 率为

,

来产 生 正 弦

时

。

,

的特性如 下 输 出频 率 为

频 率 分 辨 率可 达 到 和 失 真率极低 采用 三 线

电压 工 作 范 围 宽 输 出 信 号 的 峰 一 峰 值 为 兼 容 串行接 口 可 以方便地 与 单 片 机接 口

翻范目田目

实 用 电子制 作 目日协皿习

简 易低 频 扫 频 仪 的设 计 与 制 作

浙 江工业 职 业技 术学 院 刘 友澈

在对 模 拟 信 号进 行数 字化 处 理 时

必 须首 先 经 过 采样 量 化 编 码

、 、 。

,

由奈 奎

二 电路 设 计

单片机

由于 扫 频 仪 需 要 采

、

斯特

公 采 样 定 理 可 知 若 要无

、 、

,

正 弦 信 号发 生器 的原 理 框 图 如 图

所示

,

。

以 高稳定度的 时钟 为 参 考

扫频式超声波治疗仪[实用新型专利]

专利名称:扫频式超声波治疗仪专利类型:实用新型专利

发明人:刘思吕

申请号:CN202021214609.6申请日:20200628

公开号:CN213159037U

公开日:

20210511

专利内容由知识产权出版社提供

摘要:本实用新型涉及一种扫频式超声波治疗仪,属于超声波治疗仪器技术领域。

本实用新型包括横向放置的治疗仪的主机,主机底部安装有四根支腿,主机顶部设置有呈流线型的控制面板;主机内设置有控制器、超声波换能器、电源和散热器,控制器分别与控制面板、超声波换能器、电源和散热器连接;主机侧部安装有线缆,线缆一端与超声波换能器相连,另一端与探头振子相连;探头振子包括壳体,以及位于壳体底部的屏蔽栅、位于壳体内部的圆锥振子;圆锥振子的振荡频率范围为0.5MHz‑3.0MHz,探头振子的屏蔽栅与人体表面相接触。

本实用新型可广泛运用于超声波治疗仪器场合。

申请人:刘思吕

地址:230010 安徽省合肥市包河区巢湖南路88号元一柏庄16栋102室

国籍:CN

代理机构:青岛发思特专利商标代理有限公司

更多信息请下载全文后查看。

虚拟数字音频扫频仪的设计

p o e s r o p s le ngcr ut ewo k t e me sr d,a t—la ig f trn ic i a d h s o rc so ,lw— a sftr ic i,n t r o b au e i i n iaisn le gcr ut n o tc mpue o to nef c i i trc nrlitra e.Th lo tms eag r h i

f tr . u u e

Kewod :Vr a is u n Fe u n ys e p r A lu e ̄ q e c hrce sc Dgtlsga rcso DS y r s iu l nt me t rq e c w e e mpi d 一 e u ny c aa tr t s t r t ii ii i l po esr( P) Di c ii l a n r tdg a e t  ̄ q e c ytei DD ) e u n ysnh s s( S

的算 法 。现场测 试 数据 表明 , 能够 在容 许误 差范 围 内测 出待测 网络 在音 频范 围 内的 幅频特 性 , 明 了系 统设 计 方案 的 合理 性 , 系统 证 同

时也 证 明 了虚拟 数字音 频扫 频仪 可 能成 为今后 数字 音频 扫频 仪 的发展 趋 势。

关键 词 :虚 拟仪器

虚 拟数字音频扫频仪的设计

周

涛, 等

虚 拟 数 字 音 频 扫 频 仪 的设 计

De in o h ru lDii l di r q en y S e p sg ft e Vi a gt t a Au o F e u c w e er

周 游 饧 墨 常 郝 明 日

本设计 的幅频 特性测试 编程 思路 为 : eWM 中 用 P 断子程 序产生单频扫频信 号 , 通过置 位标 志位 的方 并 式通知主程序 , 主程序记 录 当前 待测 网络输 出端 的频 率 ; 后启 动模数转换器 , 对当前 待测网络输 出端的 然 并

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FOUT

=

FS

×

FTW 232

( 3)

系统选用 25 MHz 有源晶振,通过设置寄存器中的

倍频 参 数,使 AD9959 内 部 的 锁 相 环 电 路 倍 频 产 生

500 MHz的系统时钟,这一设置D9959 的技术手册,设计电路如图 5 所示。

图 5 DDS 电路设计

www. dianzikeji. org

71

电子·电路

马文瑞,等: 一种新型扫频仪的设计

图 6 PLL 电路设计

4 结束语

该扫频仪系统采用 DSP + FPGA 结构的设计方案。 信号源是设计中的一个重要环节,决定了整个系统的 指标和设计复杂度。本文在介绍 PLL 和 DDS 原理的 基础上选用 DDS 激励 PLL 完成射频扫频信号源的设 计,充分利用了 DDS 输出频率的灵活性和高分辨率, 以及 PLL 电路的高输出频率,实现了优势互补。

由 PLL 工作机理可知,当输出频率和分辨率越高

时,倍频次数 N 很大,相位噪声恶化。而全数字结构

的 DDS 也有不足: 输出频率低,输出谱中杂散多,故

难以应用于射频频率段。适当地组合 PLL 和 DDS 技术

实现 优 势 互 补,可 以 使 合 成 信 号 兼 顾 两 者 的 优 点, DDS + PLL 频率合成主要有 3 种[6 -7]: ( 1) DDS 激励锁 相环; ( 2) PLL 内嵌 DDS; ( 3) PLL 与 DDS 环外混频。

[4] 葛健. 基于 AD9858 宽带线性扫频源研究[D]. 南京: 南京理工大学,2005.

[5] 徐媛媛. 基于 AD9858 的 DDS + PLL 频率合成器[J]. 实 验科学与技术,2009,7( 5) : 4 - 6.

[6] 邓贤进,李家胤,张健,等. 宽带锁相扫频源设计[J]. 现代电子技术,2005( 24) : 123 - 126.

参考文献

段: ( 1) 直接频率合成技术; ( 2) 锁相频率合成技术 ( PLL) ; ( 3) 直接数字频率合成技术( DDS) 。

直接频率合成由于采用了大量的混频、分频、倍

研究生。研究方向: 电子设计自动化与嵌入式技术。

频和滤波,使得频率合成器体积庞大、成本高、不易

www. dianzikeji. org

[7] 干敏梁,聂佰玲. 基于 C8051F060 SOC 芯片的高频网络 分析仪[J]. 测控技术,2006,25( 增刊) : 271 - 273.

檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪檪

( 上接第 58 页)

4 结束语

本文给出了完全用 FPGA 实现 无 线 传 感 器 网 络 MAC 控制器的设计方法,该方法只需外接物理层芯 片和 MCU 便可完成网络功能。从而有效降低了成本, 减少了版面积,提高了整个系统的集成度。

图 1 扫频仪系统设计框图

DSP 作为主控芯片完成整个系统的控制及采集后 的数据处理,FPGA 的应用使 DSP 接口控制简单容易 实现。编写 DSP 程序,可以设置频率起止点和步进, 完成频率扫描。

2 DDS + PLL 结构频率合成法原理

大,灵活性强,能够进行编程、除错、再编程和重复 操作,可以充分地进行设计开发和验证。因此由 DSP 芯片和 FPGA 可编程逻辑器件所组成的控制及数据处 理模块外围电路少,运算速度快。

设计锁相环电路,对 DDS 输出信号完成 32 倍频, 频率步进为 10 Hz。后续混频电路将该路信号作为本 振信号,所以其相位噪声和杂散指标对最终输出信号 的相位噪声以及杂散有着直接的影响。考虑鉴相频率 范围、相位噪声等指标,设计选用 Analog Devices公 司的 PLL 频率合成器 ADF4107。ADF4107 由低噪声数 字鉴频鉴相器、精密电荷泵、可编程参考分频器、可 编程 A 和 B 计数器以及双模预分频器( P /( P + 1) ) 组

参考文献

[1] 代阳,李刚,陈欣,等. 电子测量技术的应用与发展 [J]. 计量与测试技术,2010,37( 8) : 10 - 11.

[2] 朱国锋. 基于 DSP 的频率特性分析仪设计[D]. 西安: 西安电子科技大学,2010.

[3] Vadim Manassewitsch. 频率合成原理与设计[M]. 何松 柏,宋亚梅,鲍 景 富,等,译. 北 京: 电 子 工 业 出 版 社,2008.

图 2 锁相环结构图

PD 检测 f1 与 f2 相位差,输出平均值与该相位差 成比例的直流电流。PD 产生的脉冲电流经过 LF 产生

调节电压,该电压驱动 VCO 来增加或减小输出频率

直到 PD 平均输出为零。输出信号 FOUT为

FOUT

=

N

×

XTAL R

( 1)

2. 3 DDS 技术

DDS 技术从相位的角度出发直接进行频率合成,

1 扫频仪系统设计

该系统的设计主要由控制及数据处理电路、扫频 信号源电路、幅度检测电路、相位检测电路、键盘输 入及显示电路构成[2]。控制及数据处理电路采用 DSP + FPGA 的 结 构 设 计,DSP 具 有 强 大 的 数 据 处 理 能 力、较高的运行速度和稳定 的 性 能,而 FPGA 容 量

2. 1 频率合成技术 频率合成是由一个或几个参考频率源产生一个或

多个频率的系统元件的组合[3 - 4]。随着技术的进步, 尤其是迅速发展的通信领域对于频率精度和稳定度的

要求越来越高,频率合成技术也受到了越来越多的挑

战。总地来说,频率合成技术的发展经过了 3 个阶

收稿日期: 2010-12-13 作者简介: 马 文 瑞 ( 1985 - ) ,男,硕 士 研 究 生。研 究 方 向: 电子设计自动化与嵌入式技术。杨培君 ( 1986 - ) ,男,硕士

AD9959 是 Analog Devices 公司生产的一款高采样

频率、高精度的 DDS 芯片,由 4 个直接数字频率合

成器内核构成,每个通道均可提供独立的频率、相位

和幅度控制。最高采样频率 500 MHz,最高输出时钟

频率 250 MHz,频率分辨率可达 0. 12 Hz,能够满足

系统的设计要求。设系统时钟为 FS,FTW 为频率控 制字,则 DDS 输出频率与控制字的关系为

成。A( 6 位) 、B( 13 位) 计数器与双模预分频器( P / ( P + 1) ) 配合,可实现 N 分频器( N = BP + A) 。此外, 14 位 参 考 分 频 器 ( R 分 频 器 ) 允 许 PFD 输 入 端 的 REFIN频率为可选值。如果频率合成器与外部环路滤 波器和电压控制振荡器( VCO) 一起使用,则可以实现 完整的锁相环。ADF4107 最高鉴相频率为104 MHz, 相噪基为 - 219 dBc / Hz,采用 ADIsimPLL 软件可以方 便的仿真并设计出外部锁相环路滤波器。

Design of a Novel Frequency Sweeper

Ma Wenrui,Yang Peijun ( School of Electronic Engineering,Xidian University,Xi'an 710071,China) Abstract A new RF sweeping system based on a structure composed of DSP and FPGA is presented,with focus on the design of the sweeping signal generator. The trend of frequency synthesizers is discussed. After introducing the theory of phase locked loop and direct digital frequency synthesis technology,a design of signal generator based on the DDS + PLL structure is put up in the end of this paper. Keywords DSP; frequency sweeper; PLL; DDS

DDS 激励锁相环方式电路简单,但是 DDS 的杂 散和相位噪声在带内被恶化,其频率分辨率也会由于 PLL 的倍频作用下降到原来的 1 / N。PLL 内嵌 DDS 难 点在于系统中的带通滤波器很难实现,杂散抑制也难 以获得比较高的指标。设计要求实现 100 ~ 1 000 MHz 的全程扫频信号源,而环外混频方式只能在一个较窄 的频率范围内实现。综合考虑成本及电路实现的难易 程度,该方案选择 DDS 激励锁相环的方式实现射频 扫频信号源的设计。由于输出的频段较宽,将频段搬 到较高的频段实现,降低相对带宽,然后下混频得到 所需频段。实现原理框图,如图 4 所示。

图 4 DDS 激励锁相环频率合成方法结构框图

70

www. dianzikeji. org

马文瑞,等: 一种新型扫频仪的设计

电子·电路

3 扫频信号源电路设计

设计使用晶体振荡器,一路由锁相环频率合成器 产生 2 180 MHz 信号作为混频射频信号,可以选择博 威公司的固定锁相频率源 MPS2180; 另一路由主控芯 片 DSP 控制 DDS 产生 71. 25 ~ 99. 375 MHz 的信号, 经过滤波之后由 PLL 电路锁相至 2 280 ~ 3 180 MHz。 低通滤波器( LPF2) 的作用是滤除混频后产生的高频 分量,采用 Mini_Circuits 公司的低通滤波器 LFCN - 1400,通带范围 DC ~ 1 400 MHz,在 1 000 MHz 时的 插入损耗为 0. 41 dB。