3分钟教你看懂PCB叠层文件

PCB各层含义简介浅显易懂图文展示

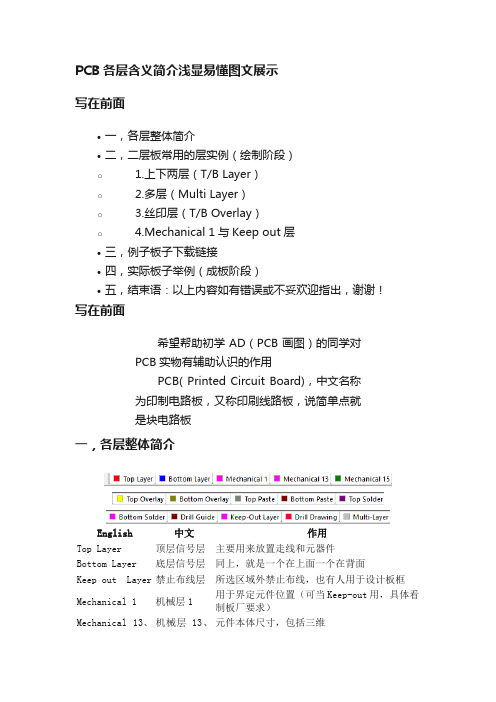

PCB各层含义简介浅显易懂图文展示写在前面•一,各层整体简介•二,二层板常用的层实例(绘制阶段)o 1.上下两层(T/B Layer)o 2.多层(Multi Layer)o 3.丝印层(T/B Overlay)o 4.Mechanical 1与Keep out层•三,例子板子下载链接•四,实际板子举例(成板阶段)•五,结束语:以上内容如有错误或不妥欢迎指出,谢谢!写在前面希望帮助初学AD(PCB画图)的同学对PCB实物有辅助认识的作用PCB( Printed Circuit Board),中文名称为印制电路板,又称印刷线路板,说简单点就是块电路板一,各层整体简介English 中文作用Top Layer 顶层信号层主要用来放置走线和元器件Bottom Layer 底层信号层同上,就是一个在上面一个在背面Keep out Layer 禁止布线层所选区域外禁止布线,也有人用于设计板框Mechanical 1 机械层1 用于界定元件位置(可当Keep-out用,具体看制板厂要求)Mechanical 13、机械层13、元件本体尺寸,包括三维English 中文作用14 14Mechanical 15、16 机械层15、16用于在设计极早期估算线路板尺寸Top Overlay 顶层丝印层用来标注各种标识,元件号,商标等Bottom Overlay 底层丝印层底层丝印,同上,就是在底层Top Paste 顶层锡膏防护层定义不被盖油的层,用于焊接或SMT加工Bottom Past 底层锡膏防护层同上Top Solder 顶层阻焊层定义不可焊接的区域保护铜箔不被氧化等作用Top Solder 底层阻焊层同上,即板子上绿(其他)色的外面这一层Drill Guide 钻孔定位层焊盘及过孔的钻孔的中心定位坐标层(注意是中心)Drill Drawing 钻孔描述层焊盘及过孔的钻孔尺寸孔径尺寸描述层Multi-Layer 多层过孔穿透此层二,二层板常用的层实例(绘制阶段)1.上下两层(T/B Layer)上下两层主要用于布线和放置元器件,红色线是顶层的走线(即导线),蓝色线是底层的二维图例:三维图例:2.多层(Multi Layer)用于绘制过孔,比如需要直插元件或者固定螺丝在封装库独立封装设计时(红色标记):多层过孔用于固定螺丝的效果(绿色标记):二维:三维:3.丝印层(T/B Overlay)这个层就很有意思了,甚至可以图案上去,常规用法就是表元器件标号、说明、商标:二维(绿色):三维(红色):加图案:二维:三维:4.Mechanical 1与Keep out层这两个层都可以用来做板框和限制走线,但是严格划分的话,Mechanical 1层是用来制定板框的,而Keep out 层是用来设置禁止布线区域的,严格上讲Mechanical 1 的面积要大于Keep out一点才符合设计初衷。

多层PCB堆叠描述

多层PCB堆叠描述叠层结构采用0.3 1/1+1080*2+0.2 1/1+ 1080*2+0.3 1/1(0.265/0.22/0.265)详细描述:该板为6层板,采用3块2层板叠压而成,0.3 1/1,表示第一个双层板的介质厚度加上第一层铜箔厚度为0.3mm,1/1表示第一个双层板铜箔厚度为1盎司;1080×2,表示半固化板(软胶)厚度为0.12mm,1080为0.06mm;0.2 1/1,表示第二个双层板的介质厚度加上两层铜箔厚度为0.2mm,1/1表示第二个双层板铜箔厚度为1盎司;1080×2,表示半固化板(软胶)厚度为0.12mm,1080为0.06mm;0.3 1/1,表示第三个双层板的介质厚度加上两层铜箔厚度为0.3mm,1/1表示第二个双层板铜箔厚度为1盎司;结合目前PCB板加工厂家的工艺能力,在用polar公司阻抗计算器CITS25计算PCB板上迹线特性阻抗时,对影响PCB板迹线控制阻抗的几个相关参数分述如下:1、铜层厚度铜层厚度代表了PCB迹线的高度T。

内层铜箔通常情况下用到1OZ(厚度为35微米),也有在电源层要流过大电流时用到2OZ(厚度为70微米)。

外层铜箔常用1/2OZ(18微米),但由于经过板镀和图形电镀最终成品外层铜厚将达到48微米(实际计算时用该值),设计成其他铜厚将较难控制铜厚厚度公差。

若外层使用1OZ铜箔,则最终铜厚将达到65微米。

2、 PCB板迹线的上下线宽由于侧蚀的影响,PCB迹线的截面为一梯形,上下线宽差距以1mil来计算,其中下线宽=要求线宽,而上线宽=要求线宽-1mil。

3、阻焊层阻焊层厚度按10um为准(选择盖阻焊模式),但有机印后将会有所增厚,但其变化将基本不会带来阻抗值的变化。

4、介质厚度常用板材(芯板):(mm OZ/OZ *表示其数值为不包括铜箔厚度的芯板厚度)0.13* 1/1 0.21* 1/1 0.25* 1/1 0.36* 1/10.51* 1/1 0.71* 1/1 0.80* 1/11.0 1/1 1.2 1/1 1.6 0.5/0.5 1.6 1/1 1.6 2/22.0 1/1 2.0 2/2 2.4 1/13.0 1/1 3.2 1/1芯板在计算控制阻抗时的实际厚度:芯板规格0.13 0.21 0.25 0.36 0.51 0.71 0.80厚度(mm)0.13 0.21 0.25 0.36 0.51 0.71 0.80厚度(mil)5.12 8.27 9.84 14.17 20.08 27.95 31.50芯板规格1.0 1.2 1.62.0 2.4 2.5厚度(mm)0.99 1.15 1.55 1.95 2.35 2.45厚度(mil)38.98 45.28 61.02 76.77 92.52 96.46常用半固化片:(mm/mil)7628: 0.175/6.92116: 0.11/4.31080: 0.066/2.6实际计算厚度时注意半固化片随着两面线路结构不同而有所不同:(mil)HOZ 半固化片规格Copper/Gnd Gnd/Gnd Copper/Signal Gnd/SignalSignal/Signal1080 2.8 2.6 2.5 2.4 2.22116 4.6 4.4 4.2 4.0 3.87628 7.3 7.0 6.8 6.7 6.61OZ 半固化片规格Copper/Gnd Gnd/Gnd Copper/Signal Gnd/SignalSignal/SignalCopper/Gnd1080 2.8 2.6 2.5 2.4 2.22116 4.5 4.3 4.1 3.9 3.77682 7.1 6.8 6.6 6.56.4其中GND层包括铜面积占80%以上的线路层。

PCB层叠设计方法和基本原则介绍

PCB层叠设计方法和基本原则介绍

PCB设计工程师在完成预布局后,重点需要对板子布线瓶颈处进行分析,再结合PCB设计软件关于布线要求来确定布线层数,综合单板的性能指标要求与成本承受能力,确定单板的电源、地的层数以及它们与信号层的相对排布位置。

本节主要介绍PCB层叠设计方法:PCB设计软件CrossSecTIon界面、PCB层叠设计的基本原则。

一、CrossSecTIon 界面介绍

Allegro提供了一个集成、方便、强大的层叠设计与阻抗计算控制的工具,叫做Cross SecTIon。

如下图所示,可以非常直观地进行材料选择,参数确定,然后得到最终阻抗结果。

其中各选项的含义:

1.Type:选择各层的类型:电导、介质、平面

2.Material:材料,常用为 FR-4

3.Thickness:每一层的厚度

4.ConducTIvity:电导率

5.Dielectric Constant:介电常数

6.LossTangent:损耗角

7.NegativeArtwork

8.Shield:参考平面

技术专区

•FPC整个制造组装的流程介绍

•软板厂抢备货积极,臻鼎成为国内PCB首家营收破千亿•ADS生成bin的方法 ADS路径问题

•富智康计划加速印度制造印度本地设立PCB产线•14nm纳米是全球半导体工艺的壁垒或者“坎”?

-全文完-。

PCB叠层结构知识多层板设计技巧

PCB叠层结构知识多层板设计技巧PCB(Printed Circuit Board)叠层结构是指将多个层(Layer)的电路板通过堆叠的方式组合在一起形成一个整体。

多层板设计技巧包括了布线规则、信号与电源分离、地电平整、阻抗控制等方面的知识。

下面将详细介绍PCB叠层结构知识和多层板设计技巧。

首先,关于PCB的叠层结构。

PCB的叠层结构可以根据电路设计的需要选择不同的层数,一般常见的有4层、6层、8层等不同层数的叠层结构。

叠层结构具有以下几个优点:1.紧凑性:叠层结构可以将电路板的整体尺寸缩小,提高电子产品的集成度。

2.信号完整性:通过在内层设置地电平、电源电平和信号层,可以有效减少信号串扰和引入的干扰,提高信号完整性。

3.电路效率:叠层结构可以实现电路的分区布局,提高电路的工作效率。

在进行多层板设计时,需要注意以下一些设计技巧:1.PCB分区:将电路板按照不同功能进行分区,将信号层、地电平、电源电平等布局在不同的分区内,以减小信号串扰和电磁干扰。

2.信号与电源分离:将高频信号与低频信号的电源层分离开来,以减小高频信号对低频信号的干扰。

3.地电平规划:在每一层中都设置地电平层,通过整体的地电平规划和细致的连接,可以有效减小信号引入的误差和电磁辐射。

4.阻抗控制:针对高频信号的传输需要控制信号线的阻抗,通过在叠层结构中选择合适的层间间距和层间介质常数,可以实现所需的阻抗匹配。

5.差分信号布线:对于差分信号,要注意将两条线平行布线,且长度相等,以减小信号的模式转换和串扰。

6.信号引线规划:信号引线的布线应尽量短且直,以减小传输延迟和信号失真。

7.确保电源稳定:多层板设计中,要保证各个层的电源电平稳定,避免因电源干扰导致的工作异常。

综上所述,PCB的叠层结构是一种优化电路设计的方法,可以提高电路性能和可靠性。

在进行多层板设计时,需要根据具体的电路要求选择合适的叠层结构,并采用相关的设计技巧,以确保电路板的性能达到设计目标。

PCB叠层设计解析

PCB叠层设计1、叠层的目的和作用现在的单板及系统速率越来越高,单板PCB的叠层越来越重要。

单板PCB的叠层就是将信号层、电源平面层和地平面层在既符合机械工艺要求又符合单板性能要求下合理的堆叠在一起,其目的和作用主要有以下几方面:(1)为信号提供基准参考平面,如GND平面;(2)为有源器件提供一个低阻抗的电源分配系统,如电源平面;(3)平面层为信号提供低阻抗的最小回流路径,信号与回流组成的环流面积与EMC关联很大;(4)隔离信号层,防止相邻信号层间的串扰,同时对信号层产生的噪声加以屏蔽和吸收;(5)相邻电源地平面形成的平板电容是一个大容值几乎无寄生电感的去耦傍路电容;电源地平面可被当作一个平板电容器来对待,尤其在中低频时,其ESR,ESL都很小。

在这种情况下,电源、地平面作为一个去耦电容,对RF能量的抑制具有电容器无可比拟的优越性,通常电容器在500MHz以上,由于分布参数的影响,电容基本上曾现感性,已经失去作用,而电源、地平面则100MHz以上直至GHz的范围内具有良好的去耦滤波特性。

但是由于电源、地平面通常由于设计的需要,会被分割,这样就造成了平面的不完整,因此此时平面的电容特性会变得非常复杂,而且,在高频时,由于分布电感ESL的影响,电源、地平面相当于一个谐振腔,具有谐振特性,而且自谐振频率是物理结构和外置的函数高速PCB的叠层设计在保证电源/地阻抗及EMI控制方面有较大影响。

而当该电源、地平面的位置有激励源,就很容易起振。

故通过增加滤波电容或适当调整芯片的外置,从而达到我们的设计要求。

(6)合理的叠层不仅能起到信号传输线阻抗控制的作用,同时又起到抑制板上系统噪声的作用;(7)在PI仿真中,电源平面与参考地平面之间的距离是与电源平面的阻抗成正相关的,可通过合理的叠层去改善电源层的阻抗。

2、信号回流的层间跳转多层PCB中,每个布线层都应该和一个镜像层相邻,信号的返回电流在其对应的镜像层上流动。

PCB叠层结构知识

PCB叠层结构知识较多的PCB工程师,他们经常画电脑主板,对Allegro等优秀的工具非常的熟练,但是,非常可惜的是,他们居然很少知道如何进行阻抗控制,如何使用工具进行信号完整性分析.如何使用IBIS模型。

我觉得真正的PCB高手应该还是信号完整性专家,而不仅仅停留在连连线,过过孔的基础上。

对布通一块板子容易,布好一块好难。

小资料对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题;层的排布一般原则:元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;所有信号层尽可能与地平面相邻;尽量避免两信号层直接相邻;主电源尽可能与其对应地相邻;兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:元件面、焊接面为完整的地平面(屏蔽);无相邻平行布线层;所有信号层尽可能与地平面相邻;关键信号与地层相邻,不跨分割区。

注:具体PCB的层的设置时,要对以上原则进行灵活掌握,在领会以上原则的基础上,根据实际单板的需求,如:是否需要一关键布线层、电源、地平面的分割情况等,确定层的排布,切忌生搬硬套,或抠住一点不放。

以下为单板层的排布的具体探讨:*四层板,优选方案1,可用方案3方案电源层数地层数信号层数 1 2 3 41 1 12 S G P S2 1 2 2 G S S P3 1 1 2 S P G S方案1 此方案四层PCB的主选层设置方案,在元件面下有一地平面,关键信号优选布TOP层;至于层厚设置,有以下建议:满足阻抗控制芯板(GND到POWER)不宜过厚,以降低电源、地平面的分布阻抗;保证电源平面的去藕效果;为了达到一定的屏蔽效果,有人试图把电源、地平面放在TOP、BOTTOM层,即采用方案2:此方案为了达到想要的屏蔽效果,至少存在以下缺陷:电源、地相距过远,电源平面阻抗较大电源、地平面由于元件焊盘等影响,极不完整由于参考面不完整,信号阻抗不连续实际上,由于大量采用表贴器件,对于器件越来越密的情况下,本方案的电源、地几乎无法作为完整的参考平面,预期的屏蔽效果很难实现;方案2使用范围有限。

PCB叠层设计规范文档

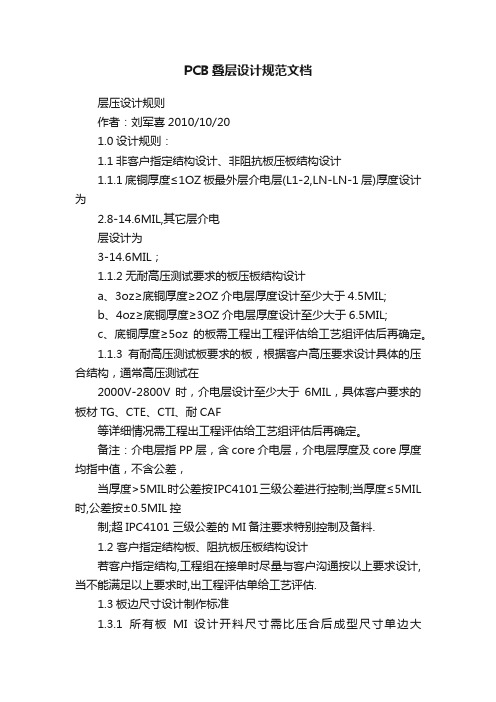

PCB叠层设计规范文档层压设计规则作者:刘军喜2010/10/201.0设计规则:1.1非客户指定结构设计、非阻抗板压板结构设计1.1.1底铜厚度≤1OZ板最外层介电层(L1-2,LN-LN-1层)厚度设计为2.8-14.6MIL,其它层介电层设计为3-14.6MIL;1.1.2无耐高压测试要求的板压板结构设计a、3oz≥底铜厚度≥2OZ介电层厚度设计至少大于4.5MIL;b、4oz≥底铜厚度≥3OZ介电层厚度设计至少大于6.5MIL;c、底铜厚度≥5oz的板需工程出工程评估给工艺组评估后再确定。

1.1.3有耐高压测试板要求的板,根据客户高压要求设计具体的压合结构,通常高压测试在2000V-2800V时,介电层设计至少大于6MIL,具体客户要求的板材TG、CTE、CTI、耐CAF等详细情况需工程出工程评估给工艺组评估后再确定。

备注:介电层指PP层,含core介电层,介电层厚度及core厚度均指中值,不含公差,当厚度>5MIL时公差按IPC4101三级公差进行控制;当厚度≤5MIL 时,公差按±0.5MIL控制;超IPC4101三级公差的MI备注要求特别控制及备料.1.2 客户指定结构板、阻抗板压板结构设计若客户指定结构,工程组在接单时尽量与客户沟通按以上要求设计,当不能满足以上要求时,出工程评估单给工艺评估.1.3板边尺寸设计制作标准1.3.1所有板MI设计开料尺寸需比压合后成型尺寸单边大0.1~0.2″,同时预留开料刀具损耗每刀0.1″。

1.3.2四层板板边一般设计为≥0.5″,特殊情况下可以做到0.4″,但必须满足以下条件:A、非阻抗板;B、介电层厚<8.0MIL;C、内层铜厚<2OZ;1.3.3六层及以上板按照板边≥0.75″控制,六层板特殊情况下可做0.6″(min),但需满足上述a、b、c条件。

1.3.4两张及以上芯板压合的四层板板边设计要求同六层板。

1.3.5 OPE系统设计单元边到开料边一般为≥0.9″,最小可生产0.80″。

多层PCB层叠结构

多层PCB层叠结构多层PCB层叠结构是指将多层电路板垂直堆叠在一起形成的复合结构。

每层电路板通过内层连接铜箔或盲孔连接进行互联,形成多层互联的电路板结构。

多层PCB层叠结构在电子产品中广泛应用,可以提供更高的集成度、更好的信号完整性和更好的电磁兼容性。

以下是对多层PCB层叠结构的详细介绍。

1.多层PCB层叠结构的形成在多层PCB层叠结构中,每一层电路板都通过内层连接铜箔或盲孔连接进行互联。

内层连接铜箔是涂覆在电路板表面的一层薄铜箔,用于互联内层电路板。

而盲孔连接是通过在电路板上钻孔并在钻孔内填充导电材料,实现不同层之间的互联。

通过这些互联方式,多层PCB层叠结构中的各层电路板可以实现信号的传输和电力的供应。

2.多层PCB层叠结构的优势-更高的集成度:多层PCB层叠结构可以将大量的电路布局在一个小尺寸的电路板上,提高了电子产品的集成度,降低了产品的体积和重量。

-更好的信号完整性:多层PCB层叠结构可以通过控制互联线的长度和层间电容来降低信号的传输延迟和传输损耗,提高信号的完整性和稳定性。

-更好的电磁兼容性:多层PCB层叠结构可以通过分层布局、层间隔绝、屏蔽层等措施来减少电磁干扰和串扰,提高产品的电磁兼容性。

-更高的可靠性:多层PCB层叠结构中的内层连接铜箔和盲孔连接可以提供更好的连接可靠性,降低连接线路的应力和故障率。

3.多层PCB层叠结构的设计考虑在设计多层PCB层叠结构时,需要考虑以下因素:-信号/电源分层:将不同类型的信号和电源分层布局在不同的层次,避免信号和电源之间的互相干扰。

-分层布局:在多层PCB层叠结构中,需要将布局相似或相关的电路放在相邻层,以便进行互联。

-地面层设置:在多层PCB层叠结构中,通常在每一层上设置一个地面层,用于减少电磁噪声和提供良好的地面引用。

-信号层与地面层的隔离:为了减少信号层和地面层之间的串扰,通常在它们之间设置一层隔离层。

-控制层间阻抗:在多层PCB层叠结构中,需要控制层间连接线的宽度和间距以满足特定的阻抗要求,以确保信号传输的完整性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3 分钟教你看懂PCB 叠层文件

我们都知道,电路板的叠层安排是对PCB 的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的emc 性能。

那幺下面就和咱一起来看看到底如何才看懂叠层文件吧~

下图是我们一般情况下看到的叠层好的文件图示:

一、对(图一)解析如下:

首先,我们可以看出叠层是8 层板,有5 个走线层(TOP、ART03、

ART04、ART06、BOTTOM),有2 个地层(GND02、GND05),有1 个电源

层(PWR07)。

其次我们可以获得整个板子的使用的PP 片情况,GND02-ART03 一张芯

板(core),ART4-GND05(core) 一张芯板,ART06-PWR07(core) 一张芯板, 其

它的用PP 加铜箔,最后压合在一起而成的。

TOP、GND02 层中间的PP 片是2116 半固化片,ART03、ART04 层中间的PP 片是由2 个3313 半固化片和

1 个7628 半固化片压合而成,GND05、ART06 层中间的PP 片是由

2 个3313

半固化片和1 个7628 半固化片压合而成,PWR07、BOTTOM 层中间的PP

片是2116 半固化片。