第五节触发器的逻辑功能及其描述方法

5 边沿触发器的逻辑功能总结

0

m1 m4 m5 m6

0 1 1

00

01

11 10 代数化简

0n 0

0 1

1 1 KQ n J Q n

Q n1 J Q n KQ n

3.状态转换图

J=1 K=× J=0 K=× 0 J=× K=1 1 J=× K=0

1 1

1 1

0 1

1 0

翻 转

5.6.2 JK 触发器

三、触发器逻辑功能的描述方法

1、触发器的逻辑功能:

是指次态与现态、输入信号之间的逻辑关系。 即:

次态= f(现态,输入)

注意:逻辑功能与电路结构是两个不同的概念, 同一逻辑功能的触发器可以用不同的电路结构实 现;同时,以同一基本电路结构,也可以构成不 同逻辑功能的触发器。本节讨论触发器的逻辑功 能,暂不考虑内部电路结构。

Q n 1 S RQ n

SR=0(约束条件) 3. 激励表

Qn

Qn+1

S

0 1 0 X

R

x 0 1 1

0 0 1 1

0 1 0 1

5.6.4 SR 触发器

4. 状态图

S=1 R=0 S=0 R=× 0 S=0 R=1 1 S=× R=0

5.6.4 SR 触发器

4. 时序图

设上升沿 有效 初态为0

0 0 1 1 Qn+1=0 Qn+1=1

5.6.2 JK 触发器

2.特性方程 1.特性表

J K Qn Qn+1 说 明 状态不变 置 0 置 1

KQn

Q

J n 1

0 0

0 0 1 1

0 0

1 1 0 0

数字电路--触发器原理

2、CP=1时跟随,下降沿到来时才锁存, 锁存的内容是CP下降沿瞬间D的值。

D (b) CP 符号

(二)工作原理:

(a)

将S=D、R=D代入同步SR触发器的特性方程,得D锁存器的特性方程:

Q* S RQ = D+ DQ = D

CP=1期间有效

第五章

• §5.1 概述

• §5.2 SR 锁存器ne NhomakorabeatQ

0

1

Q

S

R

Q 0

1

& &

0

S

1

0

R

①R=0、S=1时:由于R=0,不论原来Q为0还是1,都有Q=1; 再由S=1、Q=1可得Q=0。即不论锁存器原来处于什么状态都 将变成0状态,这种情况称将锁存器置0或复位。 R端称为置0端或复位端。

ok

Q

1

0

Q

S 1

R 0

Q 0 1

&

&

0

1

S

0

1

R

②R=1、S=0时:由于S=0,不论原来Q为0还是1,都有Q=1; 再由R=1、Q=1可得Q=0。即不论锁存器原来处于什么状态都 将变成1状态,这种情况称将锁存器置1或置位。

Q* Q

Q* 0

保持 置0 置1

特 性 表

0 0 1 1 1 1

Q* 1

Q* Q

翻转

主要特点

①主从JK触发器采用主从控制结构,从根本上解决了输入信号直 接控制的问题,具有CP=1期间接收输入信号,CP下降沿到来 时触发翻转的特点。 ②输入信号J、K之间没有约束。 ③存在一次变化问题。

二、触发器的两个基本特点: 1.具有两个稳定状态—0状态和1状态 2.能够接收、保存和输出信号

触发器(电子技术课件)

触发器•1.概述•2.SR锁存器•3.电平触发的触发器•4.边沿触发的触发器•5.触发器的逻辑功能及其描述方法一、概述1.触发器的特点(1)有两个稳定状态(简称稳态),用来表示逻辑0和1。

一个触发器可存储 1 位二进制数码(2)在输入信号作用下,触发器的两个稳定状态可相互转换(称为状态的翻转)。

(3)输入信号消失后,新状态可长期保持下来,具有记忆功能。

2.触发器的分类(1)按电路结构分(不同的电路结构在状态变化过程中有不同的动作特点)基本触发器:输入信号电平直接控制同步触发器:时钟电平直接控制;CP=1或0时有效主从触发器:主从控制脉冲触发;CP下降沿或上升沿到来时有效边沿触发器:时钟边沿控制;CP下降沿或上升沿时刻有效(2)按逻辑功能分RS 触发器JK触发器D触发器T触发器3.触发器的逻辑功能指触发器输出次态Q n+1与输出的现态Q n及输入信号之间的逻辑关系。

触发器逻辑功能的描述方法主要有特性表、特性方程、驱动表(激励表)、状态转换图(状态图)和波形图(时序图)等。

SR(Set-Reset)锁存器(又叫基本RS触发器)是各种触发器构成的基本部件,也是最简单的一种触发器。

锁存器---不需要触发信号,由输入信号直接完成置0或置1操作。

触发器---需要一个触发信号(称为时钟信号CLOCK),只有触发信号有效时,才按输入信号完成置0或置1操作。

1.电路结构与工作原理(1)用或非门组成的锁存器•电路组成信号输入端互补输出端Q和Q′为互补输出端,正常工作时,它们的输出状态相反。

通常用Q的状态表示触发器的状态,即:Q = 0,Q'= 1时,称为触发器的“0”态。

Q = 1,Q'= 0时,称为触发器的“1”态。

•工作原理0①R D =0,S D =1时1001锁存器为“1”态Q'=0Q =1②R D =1,S D =0时101锁存器为“0”态Q'=1Q =0•工作原理③RD =0,SD=0时11锁存器为“0”态Q'=1Q=0锁存器为“1”态Q'=0Q=1•若Q = 00•若Q = 11锁存器的状态保持不变01 0•工作原理1④R D =1,S D =1时1“禁止”态Q'=0Q =0•Q 和Q'违背互补输出的条件。

描述触发器的逻辑功能的方法有

描述触发器的逻辑功能的方法有触发器是数据库中的一个重要概念,它具有逻辑功能,可以在特定事件发生时自动执行相应的操作。

触发器可以用于确保数据库的完整性、约束条件的执行以及触发特定的业务逻辑等。

本文将详细介绍触发器的逻辑功能,并从创建触发器到触发器的应用等方面进行阐述。

首先,触发器的逻辑功能主要包括以下几个方面:1. 数据完整性:在数据库系统中,我们希望数据的完整性得到保证,以避免数据异常和错误。

触发器可以用于实现数据完整性的约束条件。

比如,当插入、更新或删除某条数据时,可以通过触发器来强制执行一些条件,确保数据的完整性。

例如,我们可以创建一个触发器,监测在向某个表中插入数据时是否满足某些条件,如果不满足,则禁止插入操作。

2. 约束条件的执行:数据库系统中的约束条件是一组用于描述数据合法性的规则。

通过使用触发器,我们可以在数据发生变化时,自动执行约束条件。

比如,在某个表中创建了一个唯一性约束,防止重复数据的插入。

在插入或更新数据时,触发器可以检查是否违反唯一性约束条件,如果违反,则拒绝操作。

3. 触发特定的业务逻辑:触发器还可以用于触发特定的业务逻辑。

比如,当插入某个表的数据时,触发器可以根据插入的数据自动执行一些计算操作,计算出一些相关的结果,并将计算结果存储到其他表中。

这样,我们可以在触发器中实现业务逻辑的自动计算,提高数据处理的效率和准确性。

接下来,让我们来看看如何创建触发器及其使用方法。

创建触发器的基本语法如下:CREATE TRIGGER trigger_name{BEFORE AFTER} {INSERT UPDATE DELETE}ON table_nameFOR EACH ROWBEGIN触发器的执行逻辑END其中,`trigger_name` 是触发器的名称,`BEFORE` 或`AFTER` 表示触发器执行的时机,`INSERT`、`UPDATE` 和`DELETE` 表示触发器所绑定的事件类型,`table_name` 是触发器关联的表名。

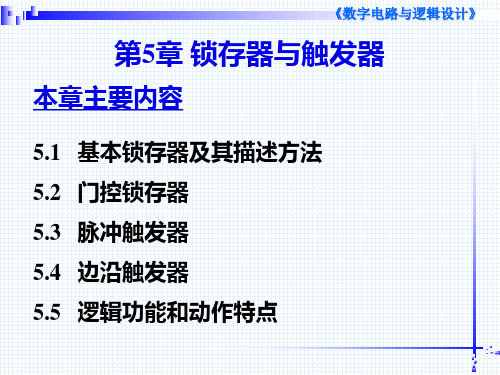

第5章 锁存器与触发器

《数字电路与逻辑设计》

3) 状态转换图与激励表

将锁存器两个状态之间的转换及其所需要的输 入条件用图形的方式表示称为状态转换图(简称为 状态图),用表格的形式表示则称为激励表。

基本SR锁存器的状态图如下图所示,表5-2为 其激励表。

表5-2 基本SR锁存器的激励表

SD=0

RD=´

0

SD=1 RD=0

《数字电路与逻辑设计》

第5章 锁存器与触发器

本章主要内容

5.1 基本锁存器及其描述方法 5.2 门控锁存器 5.3 脉冲触发器 5.4 边沿触发器 5.5 逻辑功能和动作特点

《数字电路与逻辑设计》

本章重点:

掌握锁存器与触发器的电路结构、逻辑 功能和动作特点

本章难点:

触发器的工作原理

《数字电路与逻辑设计》

此外,锁存器的功能还可以用状态转换图和激 励表表示。

《数字电路与逻辑设计》

1) 特性表(真值表) 基本锁存器的特性表如表5-1所示。

表5-1 基本SR锁存器特性表 与非门构成的锁存器 或非门构成的锁存器 SD RD Q Q* SD RD Q Q* 1 1 0 0 0000 1 1 1 1 0011 1 0 0 0 0100 1 0 1 0 0110 0 1 0 1 1001 0 1 1 1 1011 0 0 0 × 1 1 0× 0 0 1 × 1 1 1×

《数字电路与逻辑设计》

(2) CLK为高电平时, 由于SD=(S·CLK)=S、RD=(R·CLK)=R,因 此门控锁存器将根据输入信号S和R实现其相应的 功能。

将SD=S、RD=R代入到基本锁存器的特性方 程Q*=SD+RD·Q,可得到门控锁存器的特性方程为

Q*=S+R·Q

第五章 触发器

图5.5.2 带异步置位、复位端的CMOS边沿触发器

CMOS边沿触发器的特性表

CP

D

Q

n

Q n 1

0 0

0

0 0

1

0

1 1

1 1

1

(4-33)

二、维持阻塞触发器 1、阻塞RS触发器

S

①置1 维持 线

1

0

S’

& G5 0 1

③置0 阻塞线

&

G3 L1 L2

1 0 1

& G1

Q 0 1

§5.3 电平触发的触发器

一、电路结构及工作原理

(1)CP=0,状态不变。

(2)CP=1,工作,同SR锁存器一样约束条件为:SR=0。

电平触发RS触发器的特性表

*CP回到低电平后状态不定 在使用电平触发RS触发器的过程中,有时还需要CP信号到 来之前将触发器预先置成指定的状态,为此在实用的电平触发 RS触发器电路上往往还设置有专门异步置位输入端和异步复位 输入端,如下页图:1717

1

1 0

1 0

01 10

0 1 0 1

设触发器的初始状态Q=0。

CP=0:基本RS触发器的状态通过A,A’得以保持。

CP变为高电平以后:门 B,B’ 首先解除封锁,若此时输入 为J=1,K=0,则P=0,P’=1 ,…状 态无影响。 CP下降沿到达时:门 B,B’ 首先封锁,P,P’ 的电平不会立

第五章 触发器

§5.1 概述 §5.2 SR锁存器 §5.3 电平触发的触发器

§5.4 脉冲触发的触发器

§5.5 边沿触发的触发器 §5.6 触发器的逻辑功能及其描述方法

5第五节 触发器的逻辑功能及其描述方法

11

上页

下页

返回

第五节 触发器的逻辑功能及其描述方法

同样是维持阻塞结构电路,既可以做成 触发器和 同样是维持阻塞结构电路,既可以做成SR触发器和 D触发器,也可以做成下图所示的 触发器。 触发器, 触发器。 触发器 也可以做成下图所示的JK触发器

Q

CLK

Q′

K J

维持阻塞结构JK触发器(74LS109)的电路 维持阻塞结构 触发器( ) 触发器

上页 下页 返回

10

第五节 触发器的逻辑功能及其描述方法

二、触发器的电路结构和逻辑功能、 触发方式的关系

1. 电路结构和逻辑功能 触发器的逻辑功能 电路结构形式是两个不同的概念, 触发器的逻辑功能和电路结构形式是两个不同的概念, 逻辑功能和 是两个不同的概念 触发器的电路结构和逻辑功能之间不存在固定的对应 关系。 关系。 同一种逻辑功能的触发器可以用不同的电路结构实现, 同一种逻辑功能的触发器可以用不同的电路结构实现, 同一种电路结构形式可以做成不同逻辑功能的触发器。 同一种电路结构形式可以做成不同逻辑功能的触发器。

特性方程

2

′ Q* = S + RQ (约束条件) SR = 0 约束条件)

上页 下页 返回

第五节 触发器的逻辑功能及其描述方法

RS触发器输入、输出波形图 RS触发器输入、 触发器输入

S′

R′

Q

Q′

3

上页

下页

返回

第五节 触发器的逻辑功能及其描述方法

2. JK触发器 JK触发器 凡在时钟信号作用下, 凡在时钟信号作用下, 逻辑功能符合以下特性表所规定的逻辑功能者, 逻辑功能符合以下特性表所规定的逻辑功能者, 叫做JK触发器 叫做JK触发器。 触发器。

触发器逻辑功能的描述PPT课件

逻辑函数式对照法 Y D0m0 D1m1 D2m2 D3m3

D0 D2 C D1 1

连线图如下

D3 C

40

第41页/共47页

A B

0

C

1

1

41

第42页/共47页

题 4.18解法二

选择任两个变量作为地址输入变量 (例,令B=A1,C=A0)

Y ABC AC BC ABC A(B B)C BC ABC ABC ABC ABC ABC ( A A)BC ABC ( A A)BC 1 • BC A • BC 1 • BC 0 • BC

设计要求:四人参加比赛,每人一个按 钮,其中最先按下按钮者,相应的指示灯 亮;其他人再按按钮不起作用。

电路的核心是74LS175四D触发器。其 内部包含了四个D触发器,各输入、输出以 字头相区别,管脚图见下页。

30

第31页/共47页

公用时钟

USC 4Q 4Q 4D 3D 3Q 3Q 时钟

CLR

CLK

0 t

S

0 t

R

0 t

Q

0

t

10

第11页/共47页

5.6 触发器的逻辑功能及其描述方法

主从JK 触发器:

CLK

0 t

J

0 t

K

0 t

Q

0

t

11

第12页/共47页

5Q.6 触0时发,器只的允逻许辑J 功1的能及信其号描进述入方主法触发器,置1

Q 1时,只允许K 1的信号进入主触发器,置0

第3页/共47页

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7

第五节 触发器的逻辑功能及其描述方法

二、触发器的电路结构和逻辑功能、 触发方式的关系

1. 电路结构和逻辑功能 触发器的逻辑功能 电路结构形式是两个不同的概念, 触发器的逻辑功能和电路结构形式是两个不同的概念, 逻辑功能和 是两个不同的概念 触发器的电路结构和逻辑功能之间不存在固定的对应 关系。 关系。 同一种逻辑功能的触发器可以用不同的电路结构实现, 同一种逻辑功能的触发器可以用不同的电路结构实现, 同一种电路结构形式可以做成不同逻辑功能的触发器。 同一种电路结构形式可以做成不同逻辑功能的触发器。

D触发器的特性表 触发器的特性表

D =1

D Q

0 0 1 1 0 1 0 1

Q*

0 0 1 1

D=0

0

1

D =1

D=0

D触发器的状态转换图 触发器的状态转换图

特性方程

6

Q* = D

上页 下页 返回

第五节 触发器的逻辑功能及其描述方法

将JK、SR、T三种类型触发器的特性表比较一下可看 、 、 三种类型触发器的特性表比较一下可看 出, 其中JK触发器的逻辑功能最强,它包含了 触发器 其中 触发器的逻辑功能最强,它包含了SR触发器 触发器的逻辑功能最强 触发器的所有逻辑功能 和T触发器的所有逻辑功能。 触发器的所有逻辑功能。 因此在需要使用SR触发器 触发器和 触发器 触发器的场合完全可以 因此在需要使用 触发器和T触发器的场合完全可以 触发器来取代 用JK触发器来取代。 触发器来取代。 例如,在需要 触发器 触发器时 只要将JK触发器 触发器的 、 例如,在需要SR触发器时,只要将 触发器的J、K 端当作S、 端使用 就可以实现SR触发器的功能。 端使用, 触发器的功能 端当作 、R端使用,就可以实现 触发器的功能。 目前生产的触发器定型产品中只有JK触发器和 触发 目前生产的触发器定型产品中只有 触发器和D触发 触发器 这两大类。 器这两大类。

11

上页

下页

返回

T =0

T CP

1T > C1

Q

Q′

逻辑符号 上页 下页 返回

4

第五节 触发器的逻辑功能及其描述方法 仿真

T触发器输入、输出波形图 触发器输入、 输入

T CP

1T > C1

Q

Q′

逻辑符号

CP

Q

Q′

上页 下页 返回

5

第五节 触发器的逻辑功能及其描述方法

4.

D触发器

凡在时钟信号作用下, 凡在时钟信号作用下, 逻辑功能符合以下特性表所规定的逻辑功能者, 逻辑功能符合以下特性表所规定的逻辑功能者, 触发器。 叫做 D 触发器。

8

上页

下页

返回

第五节 触发器的逻辑功能及其描述方法

同样是维持阻塞结构电路,既可以做成 触发器和 同样是维持阻塞结构电路,既可以做成SR触发器和 D触发器,也可以做成下图所示的 触发器。 触发器, 触发器。 触发器 也可以做成下图所示的JK触发器

Q

CLK

Q′

K J

维持阻塞结构JK触发器(74LS109)的电路 维持阻塞结构 触发器( ) 触发器

JK触发器的特性表 JK触发器的特性表

J =1 K =×

J =0 K =×

0

J K Q Q*

0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 1 0

1

J =× K =1

JK触发器的状态转换图 触发器的状态转换图

J =× K =0

特性方程

9

上页

下页

返回

第五节 触发器的逻辑功能及其描述方法

同样,用两个电平触发 触发器结构也可以做成不 同样,用两个电平触发D触发器结构也可以做成不 同逻辑功能的触发器。 同逻辑功能的触发器。

SD J K G2 C C' C C TG C' C' TG C G1 D TG G3 C' C' C TG

Q′

Q

特性方程

2

′ Q* = S + RQ (约束条件) SR = 0 约束条件)

上页 下页 返回

第五节 触发器的逻辑功能及其描述方法

2. JK触发器 JK触发器 凡在时钟信号作用下, 凡在时钟信号作用下, 逻辑功能符合以下特性表所规定的逻辑功能者, 逻辑功能符合以下特性表所规定的逻辑功能者, 叫做JK触发器 叫做JK触发器。 触发器。

第五节 触发器的逻辑功能及其描述方法

第五节 触发器的逻辑功能及其 描述方法

触发器按逻辑功能的分类 触发器的电路结构与 逻辑功能的关系

1

推出 下页 总目录

第五节 触发器的逻辑功能及其描述方法

一、触发器按逻辑功能的分类

1. SR触发器 SR触发器 凡在时钟信号作用下, 凡在时钟信号作用下, 逻辑功能符合以下特性表所规定的逻辑功能者, 逻辑功能符合以下特性表所规定的逻辑功能者, 触发器。 叫做RS触发器 叫做RS触发器。

SR触发器的特性表 触发器的特性表 S R Q Q*

0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 不定 不定

S =1 R= 0

S =0 R=×

0

1

RS触发器的状态转换图 RS触发器的状态转换图

S =0 R=1

S =× R= 0

CLK

RD

两个电平触发D触发器构成的边沿触发 触发器 两个电平触发 触发器构成的边沿触发JK触发器(CC4027) 触发器构成的边沿触发 触发器( )

10

上页

下页

返回

第五节 触发器的逻辑功能及其描述方法

2. 电路结构和触发方式 因为电路的触发方式是由电路的结构形式决定的, 因为电路的触发方式是由电路的结构形式决定的, 所以电路结构形式与触发方式之间有固定的对应关 系。 凡是采用同步SR结构的触发器, 凡是采用同步SR结构的触发器,无论其逻辑功能如 结构的触发器 一定是电平触发方式; 何,一定是电平触发方式; 凡是采用主从SR结构的触发器, 凡是采用主从SR结构的触发器,无论其逻辑功能如 结构的触发器 一定是脉冲触发方式; 何,一定是脉冲触发方式; 凡是采用两个电平触发D触发器结构、 凡是采用两个电平触发D触发器结构、维持阻塞结构 或者利用门电路传输延迟时间结构组成的触发器, 或者利用门电路传输延迟时间结构组成的触发器, 无论其逻辑功能如何,一定是边沿触发方式。 无论其逻辑功能如何,一定是边沿触发方式。

3

′ Q* = JQ′ + KQ

上页 下页 返回

第五节 触发器的逻辑功能及其描述方法

3. T触发器 触发器

T触发器的特性表

T

0 0 1 1

Q

0 1 0 1

Q

0 1 1 0

*

特性方程

′ Q = TQ′ +TQ

*

1时 当T = 1时

Q = Q′

*

T =1

T =0

0

1

T =1

T触发器的状态转换图 触发器的状态转换图